隨著蘋果基于ARM的硅和新的RISC-V CPU的推出,對于CPU開發(fā)來說,這是一個令人興奮的時刻,盡管開發(fā)人員的旅程目前對后者來說有點坎坷。

我最喜歡的理論是,沒有發(fā)生是孤獨的,而只是重復了以前發(fā)生過的事情,也許經(jīng)常發(fā)生過。

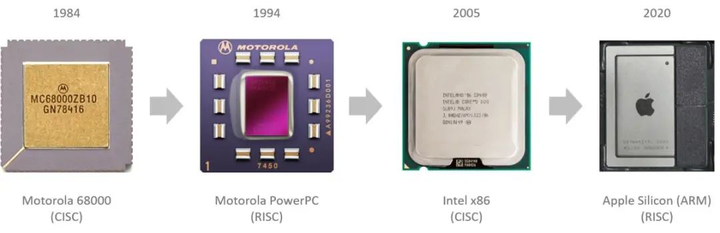

馬克·吐溫認為,生活有重演的傾向。我們可以在蘋果Macintosh的CPU架構變化中看到這一點的證據(jù),如圖1所示,1994年,最初的CISC(復雜指令集計算機)摩托羅拉68000被RISC(簡化指令集計算機)摩托羅拉PowerPC取代。這反過來又在2005年被CISC Intel x86取代,并在2020年推出了基于ARM CPU的Apple Silicon,從而回歸了RISC。

在2005年至2020年期間,英特爾x86作為筆記本電腦、臺式機、企業(yè)服務器和HPC機器的首選CPU的主導地位似乎無懈可擊,盡管ARM在移動設備中占據(jù)主導地位。此外,在此期間,我們看到了企業(yè)服務器和HPC域中競爭的RISC CPU架構的消亡,如Sun SPARC、MIPS和DEC Alpha,這表明CISC也許是CPU架構的未來。

圖1-蘋果Macintosh CPU過渡時間線。

然而,對于臺式機和筆記本電腦來說,隨著基于ARM的Apple Silicon M1片上系統(tǒng)(SoC)的推出,蘋果在2020年對這一假設提出了挑戰(zhàn)。與之前基于英特爾的版本相比,這不僅使基于M1的MacBook Pro的功耗降低了約90%,而且還將運行時性能提高了約75%[2]。此外,基于富士通ARM的超級計算機Fugaku的推出,在2021年11月的Top500排行榜上排名第一[3],進一步加強了x86作為CISC CPU架構的主導地位的挑戰(zhàn)。

雖然Fugaku在2022年6月的Top500榜單中被基于x86的Frontier系統(tǒng)取代,但它仍然位居第2位,并表明ARM將成為x86的重要競爭對手,也許會讓RISC成為高性能機器的主導CPU架構。RISC CPU架構比CISC架構更易于實現(xiàn),需要更小的硅面積,并降低功耗。與CISC架構相比,這可以增加CPU時鐘頻率和模具上更多的內(nèi)核,從而提高性能。

雖然領先的SPARC、MIPS和Alpha RISC架構已經(jīng)倒在一邊,使ARM成為x86的主要RISC挑戰(zhàn)者,但它并不是唯一獲得牽引力的RISC架構。來自加州大學伯克利分校的RISC-V是伯克利RISC CPU架構系列的第五個版本,目前正在引起大量關注。人們普遍認為,這種興趣是由于RISC-V指令集架構(ISA)是開源的,允許其不受約束地使用。然而,其他CPU架構也是開源的,例如SPARC(OpenSPARC [4])。

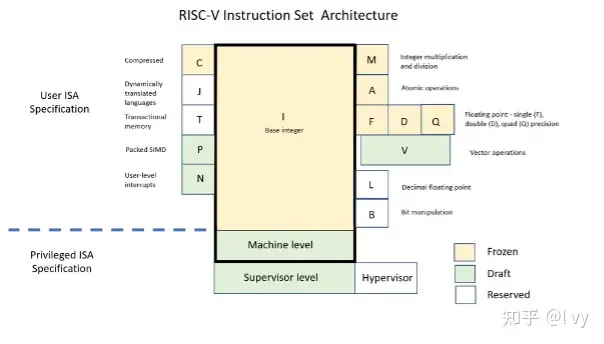

RISC-V的關鍵區(qū)別在于其ISA是模塊化的。目前有五個已批準的基ISA:RVM0(弱內(nèi)存排序)、RV32I(基32位整數(shù))、RV32E(只有16個寄存器的基32位基)、RV64I(基64位整數(shù))和RV64E(只有16個寄存器的基64位整數(shù))。如圖2所示,還定義了一些ISA擴展[5],包括支持單精度和雙精度浮點(分別為“F”和“D”),壓縮指令(“C”)和矢量指令(“V”),使CPU設計人員能夠選擇基本ISA和擴展,以提供滿足其需求的特定功能。例如,RV32E基礎ISA只支持16個寄存器,而不是32個寄存器,通過相應的功率降低,節(jié)省了大約25%的核心硅面積[6]。這對于需要非常低功耗的電池供電的嵌入式或邊緣設備是有益的。由于這些是單獨的擴展,GCC和LLVM/Clang等編譯器提供了根據(jù)需要選擇這些擴展的任意組合的選項。這種模塊化方法不僅為硬件制造商提供了更大的靈活性,還允許在不影響現(xiàn)有ISA規(guī)范的情況下創(chuàng)建和批準新的擴展。

圖2:基礎RISC-V ISA和擴展[7]。

目前有一些嵌入式和低端RISC-V CPU/SoC可用,如64位Allwinner D1(基于XuanTie C906)和64位四核SiFiveU740。還有大量的軟核,從RV32E(例如PicoRV32)到RV64GC(例如XuanTie C910和Andes X45)的變體。

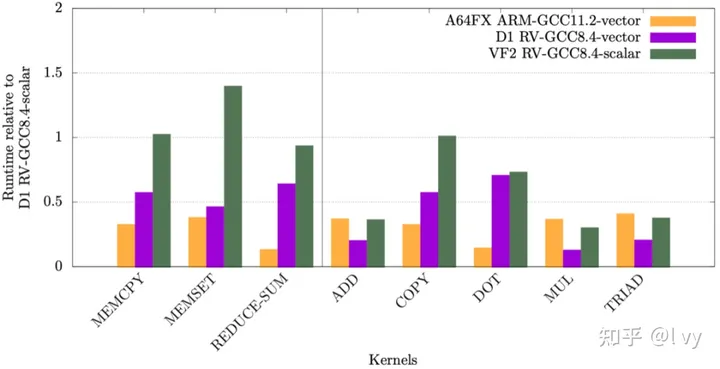

然而,RISC-V ISA擴展的萌芽性質(zhì)給開發(fā)人員帶來了一些困難。例如,“V”矢量擴展,通常稱為“RVV”,于2021年9月下旬在1.0版本中被凍結。雖然這是一個偉大的里程碑,但它與以前的RVV版本不兼容的事實是不幸的,因為目前唯一可用的支持RVV的硬CPU,C906,使用不兼容的v0.7規(guī)范。由于GCC和LLVM / Clang編譯器都針對凍結或批準的ISA擴展,在這種情況下是RVV v1.0,開發(fā)人員無法使用主線編譯器版本針對D1提供的矢量支持,并被迫依賴XuanTie開發(fā)的GCC v8.4。不幸的是,這不再從制造商那里公開提供,但可以從愛丁堡大學的DataShare網(wǎng)站下載[8]。當針對C906設備(如Allwinner D1)時,使用XuanTieGCC編譯器生成矢量化代碼可以獲得明顯的運行時性能優(yōu)勢,如一些RAJAperf[9]基準內(nèi)核的圖3所示[10]。

圖3:矢量化RISC-V與標量代碼的相對運行時性能[10]。

利用Allwinner D1矢量化支持的另一種方法是使用RVV v1.0到v0.7回滾工具[11],該工具由Joseph Lee博士開發(fā),作為ExCALIBUR H&ES RISC-V測試臺項目的一部分[12]。在這里,主線GCC和LLVM/Clang編譯器可用于自動編碼,該工具將生成的RVV v1.0匯編語言“.s”文件轉(zhuǎn)換為RVV v0.7“.s”源文件。然后由XuanTieGCC編譯器組裝,以生成對象“.o”文件/二進制文件,以在基于Allwinner D1的板上執(zhí)行。

雖然這仍然需要使用XuanTie GCC編譯器,但原始源代碼是使用最新的主流編譯器版本編譯的。有關使用RVV回滾工具的更多信息以及有關匯編RISC-V矢量代碼的一般信息,請參閱RISC-V測試臺網(wǎng)站[13]。

更一般地說,已經(jīng)提供了RISC-V測試臺,以支持那些希望在當前可用的RISC-V硬件上測試其代碼的研究人員。目前,測試臺在貧民窟集群中擁有24個RISC-V內(nèi)核,2023年4月和5月將有額外的板,使核心總數(shù)達到72個。您可以使用網(wǎng)站上概述的步驟申請訪問RISC-V測試臺[14]。

當我們考慮20世紀90年代末和21世紀初的原始RISC架構的全盛時期,以及目前基于RISC的ARM和RISC-V CPU架構的興起時,Mark Twain似乎是對的。

審核編輯 黃宇

-

ARM

+關注

關注

134文章

9304瀏覽量

374791 -

cpu

+關注

關注

68文章

11030瀏覽量

215898 -

架構

+關注

關注

1文章

526瀏覽量

25845 -

RISC-V

+關注

關注

46文章

2475瀏覽量

48227

發(fā)布評論請先 登錄

risc-v架構是哪個國家的

risc-v架構是哪個國家的

評論