晶圓測(cè)試

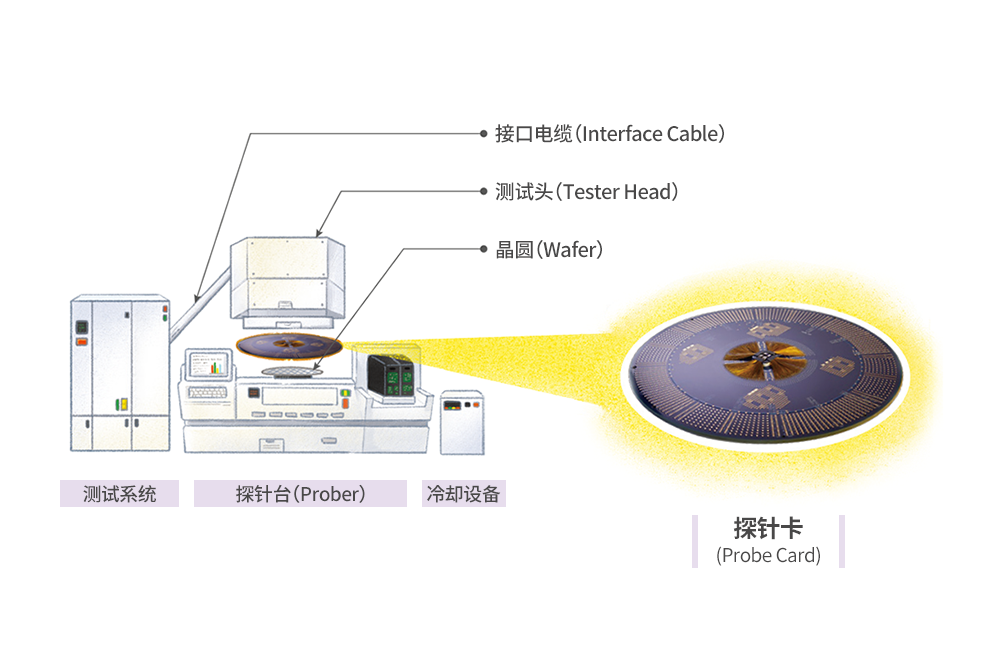

晶圓測(cè)試的對(duì)象是晶圓,而晶圓由許多芯片組成,測(cè)試的目的便是檢驗(yàn)這些芯片的特性和品質(zhì)。為此,晶圓測(cè)試需要連接測(cè)試機(jī)和芯片,并向芯片施加電流和信號(hào)。 完成封裝的產(chǎn)品會(huì)形成像錫球(Solder?Ball)一樣的引腳(Pin),利用這些引腳可以輕而易舉完成與測(cè)試機(jī)的電氣連接。但在晶圓狀態(tài)下,連接兩者就需要采取一些特殊的方法,比如探針卡(Probe?Card)。 如圖2所示,探針卡是被測(cè)晶圓和測(cè)試機(jī)的接口,卡上有很多探針2可以將測(cè)試機(jī)通訊接口和晶圓的焊盤(pán)直接連接起來(lái),卡內(nèi)還布置了很多連接探針與測(cè)試機(jī)的連接線(xiàn)材。探針卡固定在測(cè)試頭上,晶圓探針臺(tái)通過(guò)使探針卡與晶圓焊盤(pán)點(diǎn)精準(zhǔn)接觸,完成測(cè)試。 2?探針: 與晶圓焊盤(pán)進(jìn)行電氣連接和直接接觸的針狀物。

▲ 圖2 : 晶圓測(cè)試系統(tǒng)模式圖(? HANOL出版社/photograph.Formfactor)

將晶圓正面朝上裝載后,再把圖2右側(cè)的探針卡反過(guò)來(lái)使針尖朝下,實(shí)現(xiàn)與晶圓焊盤(pán)的準(zhǔn)確對(duì)位。這時(shí),溫度調(diào)節(jié)設(shè)備根據(jù)測(cè)試所需溫度條件,施加相應(yīng)溫度。測(cè)試系統(tǒng)通過(guò)探針卡傳送電流和信號(hào),并導(dǎo)出芯片訊號(hào),從而讀取測(cè)試結(jié)果。 探針卡要根據(jù)被測(cè)芯片的焊盤(pán)布局和晶圓芯片排布制作,即探針與被測(cè)晶圓焊盤(pán)布局要一致。而且,要按照芯片排列,反復(fù)排布探針。其實(shí),在實(shí)際操作中,僅憑一次接觸是無(wú)法測(cè)試晶圓的所有芯片的。因此,在實(shí)際量產(chǎn)過(guò)程中要反復(fù)接觸2~3次。 一般來(lái)講,晶圓測(cè)試依次按照“電氣參數(shù)監(jiān)控(EPM) → 晶圓老化(Wafer Burn in) → 測(cè)試 → 維修(Repair) → 測(cè)試”順序進(jìn)行。下面,我們來(lái)詳細(xì)講解一下晶圓測(cè)試的具體工序。

◎ 電氣參數(shù)監(jiān)控(EPM,Electrical Parameter Monitoring)

測(cè)試可以篩選出不良產(chǎn)品,又可以反饋正在研發(fā)或量產(chǎn)中的產(chǎn)品缺陷,從而進(jìn)行改善。相比而言,電氣參數(shù)監(jiān)控的主要目的是后者,即通過(guò)評(píng)價(jià)分析產(chǎn)品單位元件的電氣特性,對(duì)晶圓的制作工序提供反饋。具體來(lái)說(shuō),就是在進(jìn)入正式晶圓測(cè)試前,采用電學(xué)方法測(cè)量晶體管的特性和接觸電阻,驗(yàn)證被測(cè)產(chǎn)品是否滿(mǎn)足設(shè)計(jì)和元件部門(mén)提出的基本特性。從測(cè)試的角度來(lái)看,就是利用元件的電學(xué)性能提取直流參數(shù)(Parameter),并監(jiān)控各單位元件的特性。

◎ 晶圓老化(Wafer Burn in)

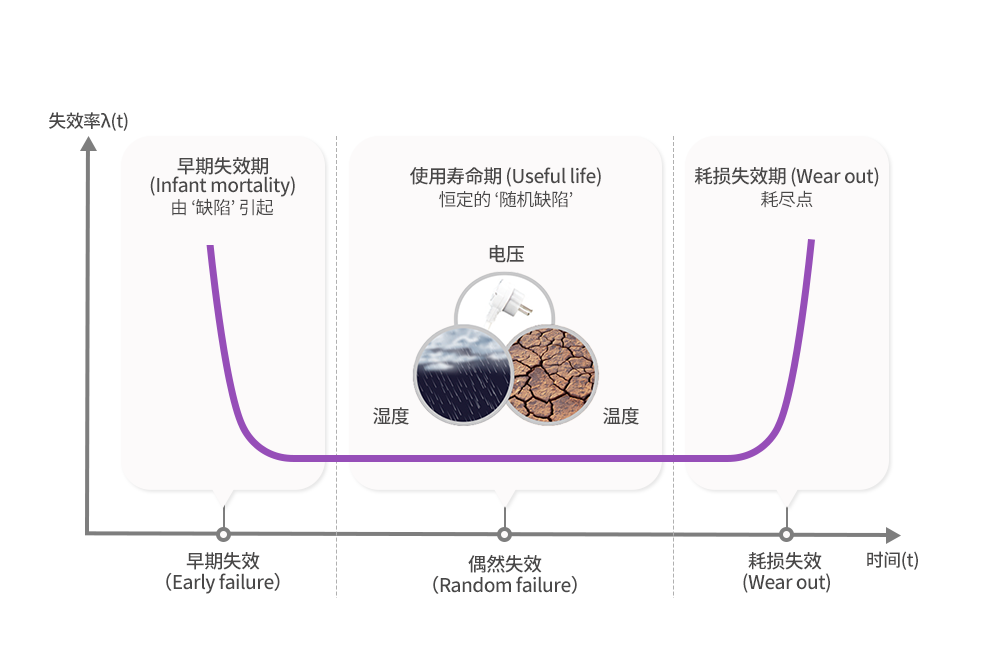

▲ 圖3:產(chǎn)品使用時(shí)間與不良率(? HANOL出版社)

圖3以時(shí)間函數(shù)揭示了產(chǎn)品生命周期中的不良率 [曲線(xiàn)呈現(xiàn)出如同浴缸的形狀,故被稱(chēng)作浴盆曲線(xiàn)(Bath-Tub Curve)] :早期失效(Early failure)期,產(chǎn)品因制作過(guò)程中的缺陷所導(dǎo)致的失效率較高;制造上的缺陷消失后,產(chǎn)品進(jìn)入偶然失效(Random failure)期,在此期間,產(chǎn)品的失效率降低;產(chǎn)品老化磨損后進(jìn)入耗損(Wear out)失效期,失效率明顯再次上升。可見(jiàn),如果完成產(chǎn)品后立即提供給客戶(hù),早期失效會(huì)增加客戶(hù)的不滿(mǎn),造成退貨等產(chǎn)品問(wèn)題的可能性也很大。

“老化(Burn in)”的目的就是為識(shí)別產(chǎn)品的潛在缺陷,提前發(fā)現(xiàn)產(chǎn)品的早期失效狀況。晶圓老化是在晶圓產(chǎn)品上施加溫度、電壓等外界刺激,剔除可能發(fā)生早期失效的產(chǎn)品的過(guò)程。

◎ 晶圓測(cè)試

在晶圓老化(Wafer Burn in)測(cè)試剔除早期失效產(chǎn)品后使用探針卡進(jìn)行晶圓測(cè)試。晶圓測(cè)試是在晶圓上測(cè)試芯片電學(xué)性能的工序。其主要目的包括:提前篩選出不良芯片、事先剔除封裝/組裝3過(guò)程中可能產(chǎn)生的不良產(chǎn)品并分析其原因、提供工序反饋信息,以及通過(guò)晶圓級(jí)驗(yàn)證(Wafer Level Verification)提供元件與設(shè)計(jì)上的反饋等。

在晶圓測(cè)試中篩選出的部分不良單元4,將會(huì)在我們下面要講到的維修(Repair)過(guò)程中被備用單元(Redundancy cell)替換。為測(cè)試這些備用單元是否能正常工作,以及芯片能否成為符合規(guī)格的良品,在維修工序后,必須重新進(jìn)行一次晶圓測(cè)試。

3?組裝: 與基板或系統(tǒng)實(shí)現(xiàn)電氣或直接連接、組裝的工序;

4單元(Cell): 為在記憶元件存儲(chǔ)信息(Data)所需的最小單位的單元數(shù)組;DRAM存儲(chǔ)單元(Cell)由一個(gè)晶體管(Transistor)和一個(gè)電容器(Capacitor)組成;

◎ 維修(Repair)

維修作為內(nèi)存半導(dǎo)體測(cè)試中的一道工序,是通過(guò)維修算法(Repair Algorithm),以備用單元取代不良單元的過(guò)程。假設(shè)在晶圓測(cè)試中發(fā)現(xiàn)DRAM 256bit內(nèi)存的其中1bit為不良,該產(chǎn)品就成了255bit的內(nèi)存。但如果經(jīng)維修工序,用備用單元替換不良單元,255bit的內(nèi)存就又重新成了256bit的內(nèi)存,可以向消費(fèi)者正常銷(xiāo)售。可見(jiàn),維修工序可以提高產(chǎn)品的良率,因此,在設(shè)計(jì)半導(dǎo)體存儲(chǔ)器時(shí),會(huì)考慮備用單元的制作,并根據(jù)測(cè)試結(jié)果以備用單元取代不良單元。當(dāng)然,制作備用單元就意味著要消耗更多的空間,這就需要加大芯片的面積。因此,我們不可能制作可以取代所有不良內(nèi)存的充足的備用單元(比如可以取代所有256bit的備用256bit等)。要綜合考慮工藝能力,選擇可以最大程度地提升良率的數(shù)量。如果工藝能力強(qiáng),不良率少,便可以少做備用單元,反之則需要多做。

維修可分為列(Column)單位和行(Row)單位:備用列取代不良單元所在的列;備用行取代不良單元所在的行。

DRAM的維修要先切斷不良單元的列或行,再連接備用列或行。維修可分為激光維修和電子保險(xiǎn)絲(e-Fuse)維修。激光維修,顧名思義,就是用激光燒斷與不良單元的連接。這要求先脫去晶圓焊盤(pán)周?chē)B線(xiàn)的保護(hù)層(Passivation layer),使連接線(xiàn)裸露出來(lái)。由于完成封裝后的芯片表面會(huì)被各種封裝材料所包裹,激光維修方法只能用于晶圓測(cè)試。電子保險(xiǎn)絲維修則采用在連接線(xiàn)施加高電壓或電流的方式斷開(kāi)不良單元。這種方法與激光維修不同,它通過(guò)內(nèi)部電路來(lái)完成維修,不需要脫去芯片的保護(hù)膜。因此,除晶圓測(cè)試外,該方法在封裝測(cè)試中也可使用。

封裝測(cè)試

在晶圓測(cè)試中被判定為良品的芯片,經(jīng)封裝工序后需要再進(jìn)行封裝測(cè)試,因?yàn)檫@些芯片在封裝工序中有可能發(fā)生問(wèn)題。而且,晶圓測(cè)試同時(shí)測(cè)試多個(gè)芯片,測(cè)試設(shè)備性能上的限制可能導(dǎo)致其無(wú)法充分測(cè)試目標(biāo)參數(shù)。與此相反,封裝測(cè)試以封裝為單位進(jìn)行測(cè)試,對(duì)測(cè)試設(shè)備的負(fù)荷相對(duì)較小,可以充分測(cè)試目標(biāo)參數(shù),從而選出符合規(guī)格的良品。

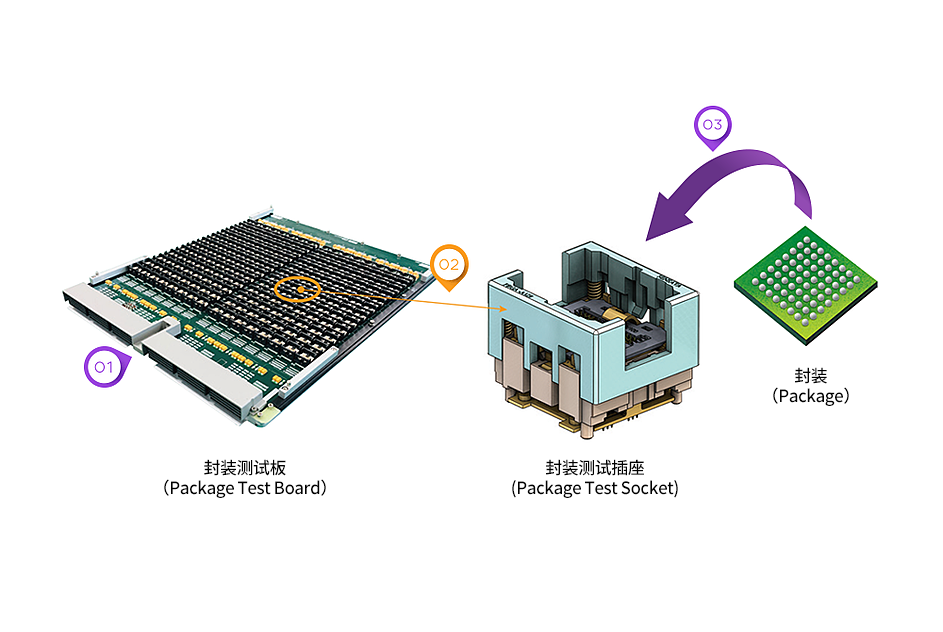

封裝測(cè)試方法如圖4所示:先把“03”的封裝引腳(Pin,圖中為錫球)朝下裝入封裝測(cè)試插座內(nèi),使引腳與插座內(nèi)的引腳對(duì)齊,然后再將封裝測(cè)試插座固定到封裝測(cè)試板(Package Test Board)上進(jìn)行測(cè)試。

▲ 圖4:封裝測(cè)試系統(tǒng)(?HANOL出版社/ photograph.NST, SENSATA)

老化測(cè)試(Test During Burn In,TDBI)

前邊也提到過(guò),“老化(Burn in)”是為了提前發(fā)現(xiàn)產(chǎn)品的早期失效,向晶圓產(chǎn)品施加溫度、電壓等外界刺激的工序。這一工序既可在晶圓測(cè)試中進(jìn)行,也可在封裝測(cè)試階段進(jìn)行。封裝后實(shí)施的“老化”被稱(chēng)為老化測(cè)試(TDBI)。大部分半導(dǎo)體產(chǎn)品在晶圓和封裝測(cè)試均進(jìn)行老化測(cè)試,以便更加全面地把握產(chǎn)品的特性,尋找縮減老化時(shí)間和工序數(shù)量的條件。可見(jiàn),老化對(duì)于量產(chǎn)來(lái)說(shuō)是一道最有效的工序。

◎ 測(cè)試

這是驗(yàn)證數(shù)據(jù)手冊(cè)5中定義的運(yùn)作模式在用戶(hù)環(huán)境中能否正常工作的流程。通過(guò)溫度測(cè)試,檢驗(yàn)產(chǎn)品交流/直流參數(shù)的缺陷,以及單元&外圍電路(Cell & Peri)區(qū)域的運(yùn)作是否滿(mǎn)足客戶(hù)要求的規(guī)格。此時(shí),需要在比數(shù)據(jù)手冊(cè)中規(guī)定的條件更為惡劣的條件下,甚至是最糟糕的條件下進(jìn)行測(cè)試。 5?數(shù)據(jù)手冊(cè)(Data Sheet):定義半導(dǎo)體產(chǎn)品基本配置與特性等具體信息的文件。

◎ 外觀(guān)(Visual)檢測(cè)

完成所有測(cè)試后,需通過(guò)激光打標(biāo)(Laser?Marking)把測(cè)試結(jié)果和速率特性(尤其是需要區(qū)分速率時(shí))記錄在產(chǎn)品封裝的表面。經(jīng)封裝測(cè)試和激光打標(biāo)后,將良品裝入封裝托盤(pán)(Tray),產(chǎn)品即可出廠(chǎng)了。當(dāng)然,在出廠(chǎng)前,還要進(jìn)行最后一道測(cè)試——外觀(guān)測(cè)試,以剔除外觀(guān)上的缺陷。外觀(guān)檢測(cè)主要查看是否有龜裂、打標(biāo)錯(cuò)誤、裝入錯(cuò)誤的托盤(pán)等問(wèn)題;錫球方面主要檢查球是否被壓扁,或球是否脫落等問(wèn)題。

審核編輯:劉清

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28613瀏覽量

232799 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7636瀏覽量

166445 -

DRAM芯片

+關(guān)注

關(guān)注

1文章

88瀏覽量

18278 -

EPM

+關(guān)注

關(guān)注

0文章

10瀏覽量

21494 -

測(cè)試機(jī)

+關(guān)注

關(guān)注

1文章

248瀏覽量

13084

原文標(biāo)題:半導(dǎo)體后端工藝:了解半導(dǎo)體測(cè)試(下)

文章出處:【微信號(hào):閃德半導(dǎo)體,微信公眾號(hào):閃德半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

半導(dǎo)體后端工藝:了解半導(dǎo)體測(cè)試(下)

半導(dǎo)體后端工藝:了解半導(dǎo)體測(cè)試(下)

評(píng)論