迷人的技術革命。

從 2011 年開始,英特爾和其他領先的半導體行業實現了顯著的技術轉型。該行業首次開始生產三維晶體管——主要稱為鰭式場效應晶體管(FinFET)。

平面

幾十年來,半導體行業的構建模塊是金屬氧化物半導體場效應晶體管或 MOSFET。這種晶體管在反相器、與非門和 SRAM 單元等數字電路中非常常見。它由位于連接源極和漏極的通道頂部的柵極組成。

源極和漏極基本上只是摻雜有其他元素原子的硅區域,用于提供或接收電子。兩者之間還有一層薄薄的絕緣層——通常由氧化硅制成。閘門本身并不穿過通道。

除了這個柵極及其絕緣層之外,整個東西都是平坦的或平面的。該柵極可以允許電子沿著溝道從源極移動到漏極。關閉柵極,電子流動停止。

經典縮放

在半導體行業的最初幾十年里,新的工藝節點只需縮小晶體管的物理尺寸并將更多晶體管塞到芯片上即可實現性能、功耗和面積增益,這稱為經典縮放。集成電路工作得更好,因為電信號在每個晶體管之間傳播的距離更短。

正如 IBM 研究人員 Robert Dennard 在 1974 年提出的那樣,第二個但同樣重要的好處是,這些較小的晶體管也使用更少的功率。摩爾定律推動半導體行業每三年將晶體管的線性尺寸減少一半。20 世紀 80 年代,尺寸首次降至1微米以下。

泄漏

大約在那個時候,人們開始注意到他們的晶體管開始表現得有點奇怪。隨著晶體管的物理尺寸縮小,源極和漏極變得越來越靠近。柵極和溝道之間的絕緣層變得更薄,為 1.2 納米或 5 個原子寬,而且通道本身也變得更細。

這樣,柵極對電流從源極到漏極的控制就會變弱。然后基本上發生的是電流從源極流向漏極時“潛入柵極下方”。即使閘門關閉,電流也可以可以穿過離柵極最遠的溝道部分,或者在某些情況下甚至穿過硅襯底本身。這被稱為“短溝道效應”,到 20 世紀 90 年代中期(350 納米工藝節點),它已成為一個嚴重的工業問題。

除了不可預測的行為之外,還存在嚴重的功耗問題。這種泄漏意味著這些較小的晶體管不遵循登納德縮放比例。

按照事情的發展方式,晶體管在“關閉”狀態下消耗的能量與“開啟”狀態下消耗的能量一樣多。這是因為消費電子產品開始變得更加便攜,從而對電源效率提出了更高的要求。

研究人員很快意識到他們正在打一場必敗之仗。經典 MOSFET 結構有一個最終終點,實際的最終尺寸限制在 20 納米左右。1996 年,憑借 250 納米的領先優勢,美國國防部高級研究計劃局(DARPA)意識到該行業沒有 2002年(5 年后)之后的長期計劃。他們呼吁提出有關25 納米以下器件的研究提案,名為25納米開關。

25納米開關

DARPA 收到了來自 IBM、AT&T,當然還有斯坦福大學的 10-12 份提案。然而,所有這些都只是原始 MOSFET 結構的延伸。這不是 DARPA 想要的。他們想要一些雄心勃勃且可行的東西。

獲勝者來自加州大學伯克利分校胡正明教授領導的團隊。胡教授于 1976 年加入伯克利分校。早期,他研究了混合動力汽車等能源主題。但里根政府上臺后,美國政府的資金很快就枯竭了,里根政府轉向半導體研究。

1982年,胡先生休假到美國國家半導體工作。在那里,他有機會從前線看到平面晶體管的終結。在聽說 DARPA 向伯克利分校的一位教員征集提案后,他召集了一批工作人員,并在一周內提出了最終提交的提案。該提案題為“太比特級電子器件的 25 nm FET 的新穎制造、器件結構和物理原理”,提出了兩個想法,都集中在讓柵極更好地控制通道本身的想法。

第一種稱為全耗盡絕緣體上硅或 FD-SOI。如果電子使用硅基板不適當地移動,那么我們會在硅基板頂部添加一層新的絕緣層以防止這種情況發生。

FDSOI 取得了一定的成功。業界已將其用于模擬或電力電子等特定用途。第二個想法是胡教授在一次長途飛行中勾勒出來的——FinFET。

FinFET 崛起

正如前面提到的,重點是讓門能夠更好地控制通道。

傳統的平面源極、漏極和溝道都是平坦的,大門位于其頂部。FinFET 將平面源極、漏極和溝道轉向一側,使其升起至周圍區域上方,并賦予其 3D 鯊魚鰭外觀。然后將門包裹在通道的頂部和側面,而不是僅僅坐在通道的頂部。

FinFET 的主要優點是它允許柵極在三個側面環繞溝道。相比之下,舊平面晶體管上的柵極僅覆蓋一側的溝道。此外,FinFET 的物理占用空間也更小。這意味著我們可以繼續將更多的它們填充到同一塊平面上。

這不是什么新主意了。之前曾提出過兩個概念上相似的提案,但這些想法都沒有被實施或變成真正的發明。

第一個來自日立公司的研究員 D. Hisamoto。早在 1990 年,他就提出了將柵極包裹在溝道周圍并制作 3D 晶體管的想法。他的論文將其稱為“完全耗盡精益溝道晶體管”或 DELTA。久本則受到德州儀器 (TI) 在 20 世紀 80 年代發表的一篇呼吁“溝槽晶體管”的論文的啟發。

發明

如果沒有執行,這個概念就毫無用處,沒有人知道這些晶體管是否可以擴展到 25 納米或更小的世界。因此,在 DARPA 的資金支持下,胡先生和他的團隊花了四年時間制作了一個可工作的 FinFET 器件的原型。

至關重要的是,該團隊可以自由地追求這一長期目標,但也有能力利用私營和公共部門的不尋常資源。這包括斯坦福大學和勞倫斯伯克利國家實驗室的設備和設施。

2001年,DARPA項目進入尾聲,胡的團隊公布了他們的研究結果。人們很快意識到 FinFET 是一項巨大的創新技術。但同樣重要的是,FinFET 并沒有太大的破壞性。該團隊確保仍然可以使用傳統的光刻和蝕刻工具來制造它。

這樣,半導體行業就可以獲得其想要的更好的性能和功效,而無需放棄數十億美元的設備和數十年的經驗。

應變工程

即便如此,半導體行業仍然是一個保守的行業。FinFET 發布后,他們并沒有立即采用,而是選擇了短期措施來避免 MOSFET 的末日。

對于 2000 年代初的 90 至 45 納米節點,業界采用了基于應變或應力的工程。在這里可以將“應變”硅層添加到通道中,通常位于硅-鍺緩沖層的頂部。

應變,意味著硅的晶體原子層被拉伸。這有助于提高電子穿過通道時的移動速度。這也不容易做到,需要工程師使用外延生長這些應變硅層。

高K金屬柵極

然后,在 2009 年至 2010 年的 28 納米工藝節點,英特爾及其團隊在其晶體管中實施了一種新型柵極。這被稱為高 K 金屬柵極。

還記得柵極和溝道之間有一層二氧化硅絕緣層嗎?對于高 K 金屬柵極,我們用氧化鉿等高 K 金屬制成的一層取代了二氧化硅層。這種高 K 值(相對于傳統二氧化硅而言較高)使相反的電荷在其所屬位置彼此分開。

這個概念也不容易實現。這導致了“Gate First or Gate Last”困境,導致行業分裂,并使得大量半導體制造商失去了領先優勢。

是時候轉向 3D 了。

三門

對于 28 納米(22 納米)之后的下一個大節點,英特爾選擇實施一種 3D 設備,他們稱之為三柵晶體管。

Tri-Gate 是原始 FinFET 的后代。最初的裝置在鰭周圍的兩個側壁上各有兩個柵極,稱為雙柵極 FinFET。

隨著時間的推移,業界發現這些選擇不會產生效果。他們對其進行了修改,以創建英特爾最終交付的產品,鰭的所有三個暴露側面上都有三個柵極層。

因此,三門形容詞。無論如何,大多數人和我一樣將它們稱為 FinFET。

過渡

從原型到批量生產始終充滿挑戰。翅片的幾何形狀(寬度、高度等)以及翅片之間的間距(稱為翅片間距)對其整體性能起著重要作用。這些都非常細節,在 20 納米或更小的工藝節點上,鰭片的寬度僅為 10 納米。

鰭片間距約為60納米。數以百萬計的納米級翅片的制造必須具有極小的變化。與一系列新的多重圖案技術同時出現,這是極其困難的。繼英特爾之后,所有代工廠都在努力擴大其首款 FinFET 產品的良率,從而導致了延誤。

臺積電和三星終于在 2013 年憑借他們所謂的 16/14 納米工藝實現了跨越。GlobalFoundries 于 2014 年加入了自己的 14 納米工藝,他們從三星獲得了工藝許可。

全柵Gate All Around

FinFET 在 N7 和 N5 代中表現良好。但最近這些也正在失去效力。代工廠正在盡一切努力來提高性能——例如,使鰭越來越高——但最終需要一套新的架構。業界已決定采用 Gate all around 作為新架構。

FinFET 工作得更好,因為它的柵極覆蓋了通道上更多的表面積,以便更好地控制。周圍的門通過完全包圍通道,甚至從以前不是的底部,進一步推進了這個想法。將柵極完全包裹在通道周圍還意味著我們可以在多個通道(或納米線)通過柵極時將它們堆疊在一起,很完美。

2022 年 6 月,三星開始發售采用全柵 FET 的 3 納米工藝。臺積電在其即將推出的 N3 工藝節點中堅持使用 FinFET。但他們將在下一個重大節點步驟 N2 中采用 Gate-all-around,該節點正在寶山建設中。

結論

這些 3D 晶體管是一個技術奇跡。但它們的價格并不便宜。FinFET 復雜的結構增加了成本,這意味著 28 納米(最后一個平面柵極)是每個柵極成本停止下降并再次開始上升的點。

當只能向下蝕刻時,如何在納米線之間建立間隙?該解決方案涉及超晶格和一種稱為原子層沉積的新方法。這些新結構使得除了最大的公司之外的所有公司都無法在經濟上取得領先優勢。在最近的一次采訪中,ASML 的首席技術官表示,他認為我們已經到達了光刻技術的極限。不是因為技術,而是因為經濟可行性。

-

3D

+關注

關注

9文章

2959瀏覽量

110727 -

晶體管

+關注

關注

77文章

10019瀏覽量

141610 -

半導體行業

+關注

關注

10文章

403瀏覽量

41122

原文標題:3D晶體管的轉變

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ZSKY-D882-SOT-89-3L NPN硅功率晶體管規格書

晶體管電路設計(下)

下一代3D晶體管技術突破,半導體行業迎新曙光!

如何測試晶體管的性能 常見晶體管品牌及其優勢比較

晶體管與場效應管的區別 晶體管的封裝類型及其特點

麻省理工學院研發全新納米級3D晶體管,突破性能極限

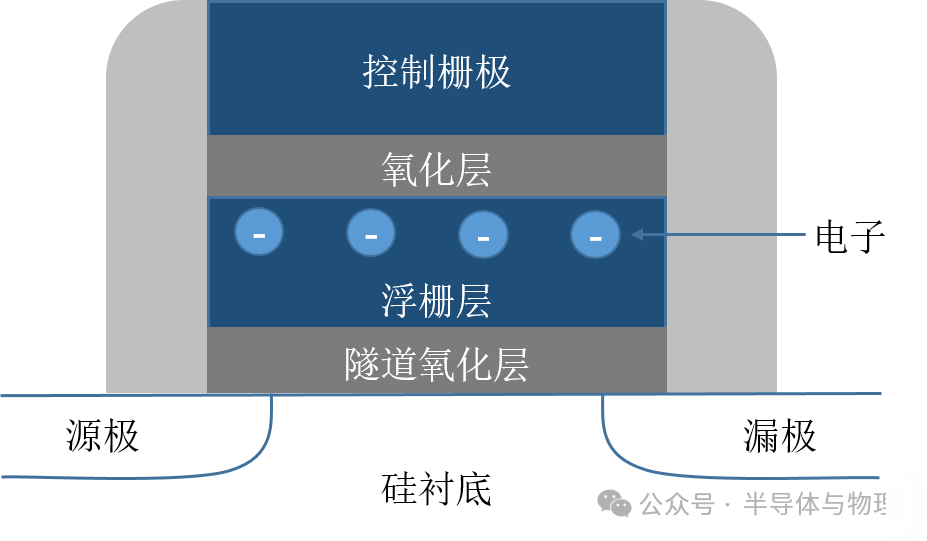

3D-NAND浮柵晶體管的結構解析

3D晶體管的轉變

3D晶體管的轉變

評論