FPGA由可配置邏輯塊(CLB)與可編程互連相結(jié)合的網(wǎng)格構(gòu)成。制造完成后,F(xiàn)PGA還可以重新編程,以滿足特定的功能或應(yīng)用需求。這一特性使FPGA有別于專用集成電路(ASIC)。后者是明確地為給定的目標(biāo)而制定的,以后無(wú)法更改。雖然一次性可編程(OTP)FPGA是一種選擇,但基于靜態(tài)隨機(jī)存取存儲(chǔ)器(SRAM)的型號(hào)是最常見(jiàn)的,并且允許隨著設(shè)計(jì)的變化而重新編程。

輸入/輸出焊盤(pán)、可重新編程的互連和可編程邏輯模塊組成了一個(gè)現(xiàn)場(chǎng)可編程門(mén)陣列。觸發(fā)器或存儲(chǔ)器模塊可用作現(xiàn)場(chǎng)可編程門(mén)陣列邏輯模塊中的存儲(chǔ)器組件。邏輯塊可以執(zhí)行簡(jiǎn)單到復(fù)雜的計(jì)算操作。

現(xiàn)場(chǎng)可編程門(mén)陣列和可編程只讀存儲(chǔ)器芯片有許多相似之處。FPGA可以容納數(shù)千個(gè)門(mén)陣列,這與可編程只讀存儲(chǔ)器芯片不同,可編程只讀存儲(chǔ)器芯片僅限于幾百個(gè)門(mén)陣列。現(xiàn)場(chǎng)可編程門(mén)陣列是可重新編程的,而不是ASIC,ASIC是為專業(yè)作業(yè)而開(kāi)發(fā)的。

計(jì)算機(jī)用戶可以使用現(xiàn)場(chǎng)可編程門(mén)陣列自定義微處理器的功能,以滿足特定的個(gè)性化需求。工程師使用FPGA來(lái)創(chuàng)建專用集成電路。晶圓功能的缺乏使得現(xiàn)場(chǎng)可編程門(mén)陣列的生命周期更具可預(yù)測(cè)性。其他優(yōu)勢(shì)包括潛在的重制、比其他解決方案更快的上市時(shí)間以及簡(jiǎn)單的設(shè)計(jì)周期。

FPGA用于許多行業(yè)和市場(chǎng),包括無(wú)線通信、數(shù)據(jù)中心、汽車、醫(yī)療和航空航天。

FPGA中的芯片是完全可編程的,這是一個(gè)相當(dāng)大的好處。通過(guò)這種方式,它可以變成一個(gè)相當(dāng)大的邏輯電路,一個(gè)遵循設(shè)計(jì)的設(shè)置,但用戶也可以根據(jù)需要進(jìn)行更新以進(jìn)行調(diào)整。換句話說(shuō),如果創(chuàng)建了一個(gè)電路卡或電路板,并且FPGA是電路的一個(gè)組件,則FPGA在創(chuàng)建過(guò)程中被編程,但隨后可以重新編程以反映任何修改。

雖然第一批FPGA是在1980年代初推出的,但直到20世紀(jì)90年代末才開(kāi)始流行起來(lái)。除了Altera、賽靈思和德州儀器等少數(shù)幾家企業(yè)之外,他們并不為人所知。

ASIC(專用集成電路)用于創(chuàng)建對(duì)于常規(guī)CPU或GPU來(lái)說(shuō)過(guò)于復(fù)雜的系統(tǒng),作為ASIC(專用集成電路)的替代方案。

由于它們使用戶能夠以更低的成本和更低的功耗生產(chǎn)產(chǎn)品,因此FPGA仍然是當(dāng)今技術(shù)中的一個(gè)突出主題。在網(wǎng)絡(luò)和網(wǎng)絡(luò)安全等其他應(yīng)用中,它們也很有幫助。將其與傳統(tǒng)微控制器進(jìn)行比較,傳統(tǒng)微控制器無(wú)法容納更大的設(shè)計(jì),這是一項(xiàng)相當(dāng)大的進(jìn)步。

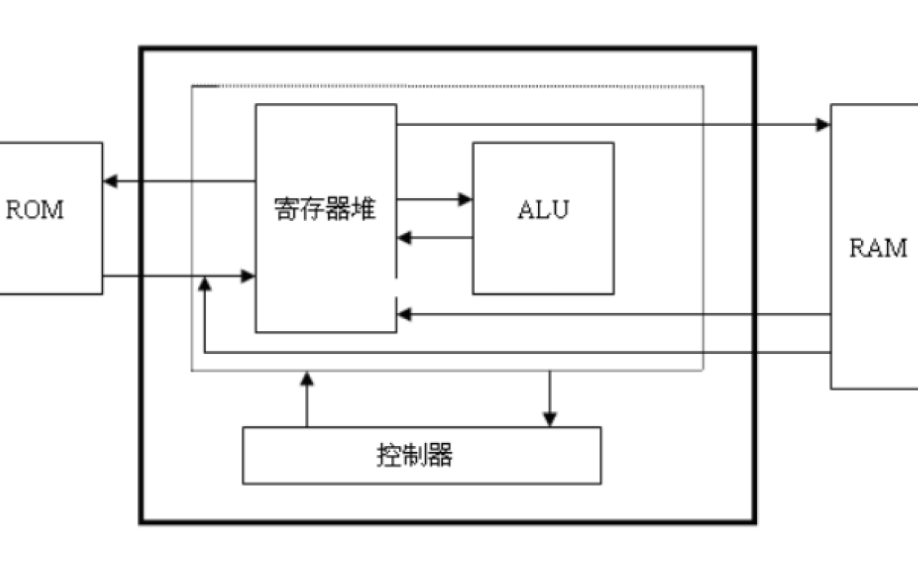

例如,8051微控制器采用了哈佛設(shè)計(jì)和CISC指令集。FPGA沒(méi)有這些內(nèi)置指令集,這給了設(shè)計(jì)人員更多的自由度。盡管FPGA經(jīng)常與高端計(jì)算相關(guān)聯(lián),但消費(fèi)電子行業(yè)的使用也在增加。

現(xiàn)場(chǎng)可編程門(mén)陣列芯片已經(jīng)在頂級(jí)顯卡中包含許多功能。然而,它們比傳統(tǒng)的視頻卡更便宜,更耗電。它們還支持許多同步流,并且具有明顯更快的吞吐量。因此,基于FPGA的圖形卡在游戲機(jī)中越來(lái)越頻繁地使用。

Verilog和VHDL只是FPGA使用的眾多不同編程語(yǔ)言中的兩種。1984年,硬件描述語(yǔ)言Verilog被創(chuàng)建。它可用于構(gòu)建系統(tǒng)所需的任何類型的電路,并且是FPGA的設(shè)計(jì)標(biāo)準(zhǔn)。

另一種基于狀態(tài)機(jī)對(duì)FPGA進(jìn)行編程的常用語(yǔ)言是VHDL。它與Verilog不同,因?yàn)樗喙δ埽鐢?shù)據(jù)類型和信號(hào)名稱,這使得創(chuàng)建復(fù)雜電路和提高效率變得更加簡(jiǎn)單。定義了FPGA編程的語(yǔ)法和語(yǔ)法。

FPGA如何工作?

每個(gè)FPGA制造商都有其獨(dú)特的架構(gòu)規(guī)范。關(guān)鍵組件、原則和功能包括:

1.可配置的邏輯塊

現(xiàn)場(chǎng)可編程門(mén)陣列的基本構(gòu)建模塊是CLB。它是一個(gè)邏輯單元,可以設(shè)置或編程以執(zhí)行特定任務(wù)。連接塊將連接到這些構(gòu)建基塊。這些組件包括攜帶和控制邏輯、晶體管對(duì)和查找表(LUT)。它們執(zhí)行設(shè)計(jì)所需的邏輯操作。

可以使用基于邏輯的多路復(fù)用器或LUT來(lái)創(chuàng)建CLB。基于LUT的邏輯中的模塊由D觸發(fā)器,查找表和2:1多路復(fù)用器組成。多路復(fù)用器選擇正確的輸出。

2.可編程互連

位于不同邏輯塊中的邏輯單元之間的所有獨(dú)特連接都存在于現(xiàn)場(chǎng)可編程門(mén)陣列的這一區(qū)域中。包含多個(gè)基本半導(dǎo)體開(kāi)關(guān)的開(kāi)關(guān)盒通常用于實(shí)現(xiàn)互連。這些電氣可編程鏈路為這些可編程邏輯模塊提供了路徑。

不同長(zhǎng)度的線段可以沿著布線路徑找到,并由電氣可編程開(kāi)關(guān)連接。FPGA密度由用于布線路徑的器件數(shù)量決定。FPGA的單元或輸入焊盤(pán)的輸出可以連接到電路中的任何其他單元或焊盤(pán),利用對(duì)每個(gè)現(xiàn)場(chǎng)可編程門(mén)陣列至關(guān)重要的可編程互連點(diǎn)。

3.可編程路由

可編程路由至關(guān)重要,因?yàn)樗ǔU冀Y(jié)構(gòu)表面的百分之五十以上以及應(yīng)用程序的關(guān)鍵路由延遲。可編程布線由預(yù)制線段和預(yù)配置的開(kāi)關(guān)組成。通過(guò)配置正確的開(kāi)關(guān)組合,功能塊的任何輸出都可以鏈接到任何輸入。現(xiàn)場(chǎng)可編程門(mén)陣列路由架構(gòu)有兩種基本類型。

設(shè)計(jì)本質(zhì)上是分層的,高級(jí)組件實(shí)例化較低級(jí)別的模塊并鏈接其中的信號(hào),從而為可編程門(mén)陣列提供了動(dòng)力。可編程門(mén)陣列可以使用連接芯片離散部分的短線來(lái)構(gòu)建這些連接,因?yàn)樵谠O(shè)計(jì)層次結(jié)構(gòu)中靠近在一起的模塊之間更頻繁地進(jìn)行通信。FPGA的密度和性能受到路由設(shè)計(jì)的影響。

4.可編程I/O模塊

接口引腳用于將邏輯模塊與外部組件連接起來(lái)。現(xiàn)場(chǎng)可編程門(mén)陣列和外部電路之間的接口是IOB(輸入輸出模塊),這是一種可編程輸入和輸出器件,用于滿足各種電氣特性下輸入/輸出信號(hào)的驅(qū)動(dòng)和匹配需求。I/O塊將路由體系結(jié)構(gòu)和CLB連接到外部元素。

在封裝引腳和器件的底層電路之間,輸入/輸出模塊提供可編程的單向或雙向連接。實(shí)現(xiàn)應(yīng)用需要從頭開(kāi)始構(gòu)建電路,因?yàn)橐郧暗默F(xiàn)場(chǎng)可編程門(mén)陣列缺乏運(yùn)行任何軟件的處理器。因此,F(xiàn)PGA可能被編程為像OR門(mén)一樣簡(jiǎn)單,或者像多核處理器一樣復(fù)雜。

5.片上存儲(chǔ)器

集成在FPGA邏輯塊中的FFS是FPGA系統(tǒng)中片上存儲(chǔ)元件的一種形式。盡管如此,隨著現(xiàn)場(chǎng)可編程門(mén)陣列邏輯容量的提高,它被用于更廣泛的系統(tǒng)中,這些系統(tǒng)幾乎總是需要存儲(chǔ)器來(lái)緩沖和重用芯片上的數(shù)據(jù)。由于構(gòu)建由寄存器和LUT組成的大型RAM的密度比SRAM塊低100倍左右,因此還需要具有更密集的片上存儲(chǔ)。

此外,在現(xiàn)場(chǎng)可編程門(mén)陣列上實(shí)現(xiàn)的應(yīng)用程序的RAM要求差異大不相同。

6.數(shù)字信號(hào)處理(DSP)模塊

在運(yùn)輸鏈之前,商業(yè)現(xiàn)場(chǎng)可編程門(mén)陣列系統(tǒng)中使用的專用算術(shù)電路是加法器。

由于需要在利用LUT和攜帶鏈的軟邏輯中加入乘法器,因此產(chǎn)生了嚴(yán)重的面積和延遲損失。由于用于現(xiàn)場(chǎng)可編程門(mén)陣列的高乘法器密度信號(hào)處理和通信應(yīng)用具有相當(dāng)大的市場(chǎng)份額,設(shè)計(jì)人員開(kāi)發(fā)了新穎的實(shí)現(xiàn)來(lái)解決軟邏輯乘法器實(shí)現(xiàn)效率低下的問(wèn)題,這稱為數(shù)字信號(hào)處理或DSP。

無(wú)乘法分布式算術(shù)技術(shù)是使用基于LUT的現(xiàn)場(chǎng)可編程門(mén)陣列創(chuàng)建高效有限脈沖響應(yīng)(FIR)濾波器設(shè)計(jì)的一種方法。乘法器是FPGA系統(tǒng)中作為專用電路進(jìn)行強(qiáng)化的主要候選者,因?yàn)樗鼈冊(cè)陉P(guān)鍵應(yīng)用領(lǐng)域的現(xiàn)場(chǎng)可編程門(mén)陣列設(shè)計(jì)中普遍存在,并且在軟邏輯中實(shí)現(xiàn)時(shí)尺寸、延遲和功耗都降低了。

7.系統(tǒng)級(jí)互連

DDR內(nèi)存和以太網(wǎng)的興起只是FPGA容量和帶寬穩(wěn)步增長(zhǎng)的幾個(gè)原因。管理這些高頻端口和不斷增長(zhǎng)的結(jié)構(gòu)之間的數(shù)據(jù)流量是一項(xiàng)挑戰(zhàn)。這種系統(tǒng)級(jí)鏈路過(guò)去是通過(guò)設(shè)置特定的FPGA邏輯和路由元件來(lái)形成軟總線來(lái)建立的,這些總線在必要的端點(diǎn)之間完成流水線,多路復(fù)用和布線。

更寬總線是匹配這些外部接口帶寬的唯一方法,因?yàn)樗鼈円员痊F(xiàn)場(chǎng)可編程門(mén)陣列結(jié)構(gòu)更高的頻率運(yùn)行。由于大量和物理上很長(zhǎng)的總線的組合,定時(shí)閉合具有挑戰(zhàn)性,并且通常需要對(duì)總線進(jìn)行相當(dāng)大的流水線處理,從而增加了資源消耗。

現(xiàn)場(chǎng)可編程門(mén)陣列的應(yīng)用

FPGA在各行各業(yè)都有廣泛的應(yīng)用,特別是在工業(yè)物聯(lián)網(wǎng)(IoT)領(lǐng)域。它的一些關(guān)鍵應(yīng)用領(lǐng)域:

1.能源行業(yè)案例研究

太陽(yáng)能和風(fēng)能等可再生能源越來(lái)越受歡迎。它們?cè)?a target="_blank">智能電網(wǎng)中是可靠的,其中法規(guī)仍在建立中。輸配電(T&D)變電站尤其需要高效的電力網(wǎng)絡(luò)來(lái)實(shí)現(xiàn)智能電網(wǎng)的最佳運(yùn)行。自動(dòng)化需要持續(xù)監(jiān)控、調(diào)節(jié)和保護(hù)電網(wǎng)的技術(shù),以實(shí)現(xiàn)更有效的峰值需求負(fù)載管理。FPGA可以提高智能電網(wǎng)的性能和可擴(kuò)展性,同時(shí)保持低功耗。

2.使用FPGA設(shè)計(jì)集成電路

必須首先創(chuàng)建此類電路的體系結(jié)構(gòu)。然后,使用FPGA構(gòu)建和測(cè)試原型,由于這種方法,錯(cuò)誤是可以糾正的。一旦原型按預(yù)期執(zhí)行,就會(huì)開(kāi)發(fā)一個(gè)ASIC項(xiàng)目。這能夠節(jié)省時(shí)間,因?yàn)閯?chuàng)建集成電路可能是一項(xiàng)勞動(dòng)密集型和復(fù)雜的操作。

此外,它還可以節(jié)省資金,因?yàn)榭梢允褂脝蝹€(gè)FPGA來(lái)創(chuàng)建同一項(xiàng)目的大量修訂版。值得注意的是,當(dāng)前的張量處理單元(TPU)或加密貨幣礦工最初是作為FPGA開(kāi)發(fā)的,直到那時(shí)它們才被生產(chǎn)出來(lái)。

3.汽車體驗(yàn)的改善

使用汽車芯片和IP實(shí)現(xiàn)車載信息娛樂(lè)、舒適性和便利性的解決方案。借助MicrosemiFPGA,車載原始設(shè)備制造商(OEM)和供應(yīng)商可以開(kāi)發(fā)創(chuàng)新的安全應(yīng)用,如巡航控制、盲點(diǎn)警告和防撞。

FPGA供應(yīng)商提供網(wǎng)絡(luò)安全功能,包括信息保證、防篡改和硬件安全,以及糾錯(cuò)內(nèi)存和低靜態(tài)功耗等可靠性功能。由于其最小的泄漏和在低功耗環(huán)境中工作的能力,基于FPGA的存儲(chǔ)可以提供低靜態(tài)功耗。

4.支持實(shí)時(shí)系統(tǒng)

在實(shí)時(shí)系統(tǒng)中,當(dāng)響應(yīng)時(shí)間至關(guān)重要時(shí),會(huì)使用FPGA。傳統(tǒng)CPU的響應(yīng)時(shí)間是不可預(yù)測(cè)的,因此無(wú)法準(zhǔn)確估計(jì)一旦觸發(fā)器觸發(fā),您將何時(shí)收到回復(fù)。采用實(shí)時(shí)操作系統(tǒng)將反應(yīng)時(shí)間保持在預(yù)定范圍內(nèi)。

在需要快速響應(yīng)時(shí)間的情況下,這是不夠的。系統(tǒng)必須在FPGA中實(shí)現(xiàn)所需的方法,利用組合或順序電路來(lái)解決這個(gè)問(wèn)題并保證恒定的響應(yīng)時(shí)間。一旦準(zhǔn)備就緒,就可以使用FPGA更改這樣的實(shí)時(shí)系統(tǒng)并將其投入生產(chǎn)。

5.航空航天和國(guó)防使用案例

為了滿足惡劣環(huán)境的性能、可靠性和壽命要求,同時(shí)提供比傳統(tǒng)ASIC實(shí)現(xiàn)更大的靈活性,工業(yè)制造公司提供了抗輻射可重構(gòu)的FPGA,這些FPGA通常是空間級(jí)的。抗輻射可重構(gòu)FPGA適用于處理密集型空間系統(tǒng)。

6.在通信和軟件定義網(wǎng)絡(luò)(SDN)中的應(yīng)用

軟件定義網(wǎng)絡(luò)(SDN)和其他算法(如快速傅里葉變換(FFT))必須放入FPGA中,以便在復(fù)雜的實(shí)時(shí)環(huán)境中使用。無(wú)線電的標(biāo)準(zhǔn)組件包括用于接收和傳輸信號(hào)的天線,以及用于通過(guò)過(guò)濾、更改信號(hào)頻率等來(lái)處理信號(hào)的網(wǎng)絡(luò)硬件。

這種硬件無(wú)法從根本上改變它所要實(shí)現(xiàn)的功能。如今,此功能的很大一部分被轉(zhuǎn)移到電子設(shè)備中,這通常是FPGA。模擬器件通常僅限于天線、ADC和DAC轉(zhuǎn)換器。

7.數(shù)據(jù)中心和云中的FPGA

物聯(lián)網(wǎng)(IoT)和大數(shù)據(jù)正在產(chǎn)生獲取和處理的數(shù)據(jù)的指數(shù)級(jí)增長(zhǎng)。這與通過(guò) 并行的多個(gè)操作的深度學(xué)習(xí)技術(shù)進(jìn)行計(jì)算分析相結(jié)合,導(dǎo)致對(duì)低延遲,靈活和安全的計(jì)算能力的高需求。由于空間成本不斷增加,無(wú)法通過(guò)添加更多服務(wù)器來(lái)解決。

由于FPGA能夠加速處理,設(shè)計(jì)靈活性以及硬件對(duì)軟件的安全性,數(shù)據(jù)中心世界的大門(mén)正在在很大程度上向他們敞開(kāi)。

8.計(jì)算機(jī)視覺(jué)系統(tǒng)

在現(xiàn)代世界中,計(jì)算機(jī)視覺(jué)系統(tǒng)存在于許多小工具中。視頻監(jiān)控?cái)z像機(jī),機(jī)器人和其他設(shè)備就是這方面的例子。許多這些小工具通常需要基于FPGA的系統(tǒng),以便它們能夠根據(jù)人的位置,周圍環(huán)境和面部識(shí)別功能,以有意義的方式與人進(jìn)行行動(dòng)和交互。要使用此功能,必須處理許多照片,其中大多數(shù)操作都是實(shí)時(shí)完成的,以檢測(cè)物體,識(shí)別人臉等。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21966瀏覽量

614156 -

集成電路

+關(guān)注

關(guān)注

5420文章

11954瀏覽量

367175

發(fā)布評(píng)論請(qǐng)先 登錄

VR禁毒科普教學(xué):禁毒普法概述

電容器的三種用途

求一種基于FPGA的微處理器的IP的設(shè)計(jì)方法

科普電涌的知識(shí)

了解STM32的八種輸出模式

基于FPGA的八通道超聲探傷系統(tǒng)設(shè)計(jì)

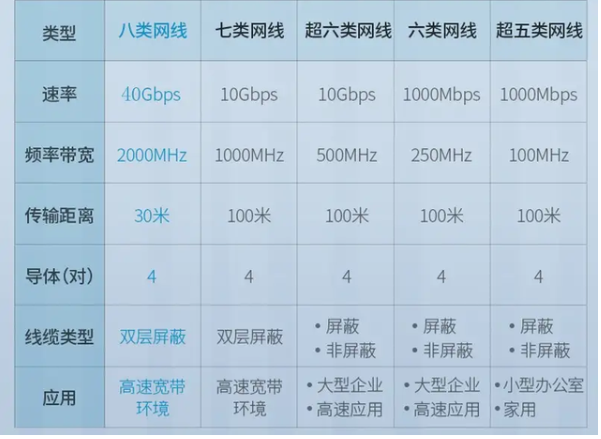

一文科普八類網(wǎng)線標(biāo)準(zhǔn)規(guī)范及區(qū)別

如何使用FPGA實(shí)現(xiàn)八位RISC CPU的設(shè)計(jì)

八種常見(jiàn)的金屬材料,它們的用途有哪些

FPGA的八種用途

電源管理芯片的八個(gè)引腳的功能和用途

科普:GPU和FPGA,有何異同

科普:FPGA的八種用途

科普:FPGA的八種用途

評(píng)論