串行器可以連接并控制攝像頭IC,ADI的這類器件包括MAX9257 (帶有半雙工UART/I2C控制通道)、MAX9259和MAX9263 (兩款均帶有全雙工同步控制通道),MAX9263還支持寬帶數(shù)字內(nèi)容保護(hù)(HDCP)。本應(yīng)用筆記介紹如何將攝像頭的RGB或YUV輸出轉(zhuǎn)換成標(biāo)準(zhǔn)顯示器接受的RGB數(shù)據(jù)。

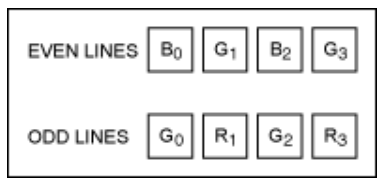

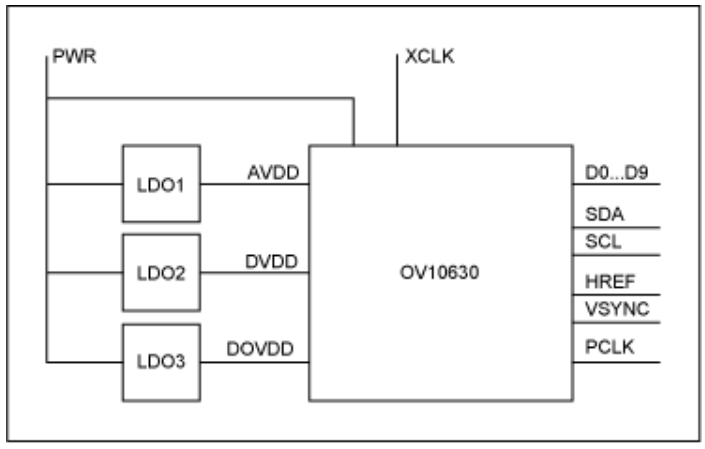

攝像頭輸出數(shù)據(jù)格式 攝像頭芯片,例如OmniVisionOV10630,可通過串行器連接。OV10630的接口引腳包括:像素時(shí)鐘、PCLK、行有效、HREF、幀同步、VSYNC和并行數(shù)據(jù)位D[9:0],數(shù)據(jù)位在時(shí)鐘的上升沿保持穩(wěn)定。YUV和原始RGB數(shù)據(jù)格式CMOS攝像頭傳感器包括數(shù)百萬光敏單元,每個(gè)單元可響應(yīng)整個(gè)波長的光信號。利用濾光膜使特定傳感器僅響應(yīng)紅光、綠光或藍(lán)光信號。相鄰的光敏單元通常以拜耳結(jié)構(gòu)的濾色規(guī)律排列,綠色濾色片的數(shù)量是紅色或藍(lán)色濾色片數(shù)量的兩倍。這種方式用于模擬人眼的感光特性。從左至右、從上至下讀取傳感器單元輸出,原始的RGB數(shù)據(jù)序列為藍(lán)、綠...藍(lán)、綠 (首行末尾),綠、紅...綠、紅(第二行末尾),依次類推,如圖1所示。

圖1. 原始RGB數(shù)據(jù)排列

通過相鄰單元內(nèi)插生成與傳感器單元密度相同的RGB數(shù)據(jù)。另外,利用相鄰單元的顏色,按照特定的規(guī)則可以恢復(fù)圖像。構(gòu)成每個(gè)像素RGB數(shù)據(jù)組的規(guī)則之一是:使用同一行的相鄰單元,再加上下一行(或上一行)的綠色相鄰單元。內(nèi)插后的RGB數(shù)據(jù)序列為...、紅(i-1)、綠(i-1)、藍(lán)(i-1)、紅(i)、綠(i)、藍(lán)(i)、紅(i+1)、綠(i+1)、藍(lán)(i+1)、...如圖2所示。每個(gè)像素需要一組RGB數(shù)據(jù),驅(qū)動(dòng)彩色顯示器并保持?jǐn)z像頭傳感器的最高分辨率。內(nèi)插RGB數(shù)據(jù)的亮度分辨率接近于傳感器單元的分辨率,但色度分辨率較差。由于人眼對每個(gè)像素的灰度要比對像素的色彩分量更為敏感,所以感覺到的分辨率基本與傳感器單元分辨率相同。

圖2. RGB數(shù)據(jù)排列

圖2. RGB數(shù)據(jù)排列

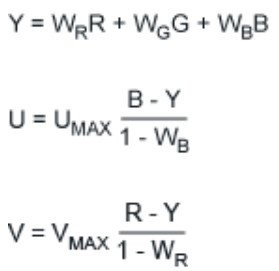

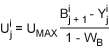

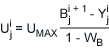

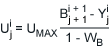

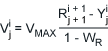

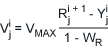

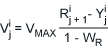

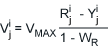

然而,這種RGB數(shù)據(jù)的內(nèi)插算法使得數(shù)據(jù)速率增至三倍。為了降低數(shù)據(jù)速率,尤其是需要圖像傳輸?shù)膱龊希刹捎肶UV彩色空間(將模擬彩色電視信號壓縮到模擬黑白電視的頻帶)。在下式中,亮度以Y表示,藍(lán)色和亮度之間的色差以U表示,紅色和亮度之間的色差以V表示,

式中,典型的色彩加權(quán)為:WR= 0.299,WB= 0.114,WG= 1 - WR- WB= 0.587,歸一化值為UMAX,VMAX= 0.615。

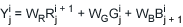

對于采用拜耳濾色鏡的攝像頭傳感器,相鄰像素的U或V數(shù)據(jù)大致相同,取決于行索引i和像素索引j (如果采用的規(guī)則為相鄰顏色)。利用本指南,可根據(jù)下式利用RGB數(shù)據(jù)直接生成YUV數(shù)據(jù)。

偶數(shù)行索引i和偶數(shù)像素索引j。

偶數(shù)行索引i和偶數(shù)像素索引j。 偶數(shù)行索引i和偶數(shù)像素索引j。

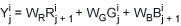

偶數(shù)行索引i和偶數(shù)像素索引j。 對于奇數(shù)行索引i和偶數(shù)像素索引j。

對于奇數(shù)行索引i和偶數(shù)像素索引j。 對于奇數(shù)行索引i和偶數(shù)像素索引j。

對于奇數(shù)行索引i和偶數(shù)像素索引j。

偶數(shù)行索引i和偶數(shù)像素索引j。

偶數(shù)行索引i和偶數(shù)像素索引j。

偶數(shù)行索引i和偶數(shù)像素索引j。 對于奇數(shù)行索引i和偶數(shù)像素索引j。

對于奇數(shù)行索引i和偶數(shù)像素索引j。 對于奇數(shù)行索引i和偶數(shù)像素索引j。

對于奇數(shù)行索引i和偶數(shù)像素索引j。 偶數(shù)行索引i和偶數(shù)像素索引j。

偶數(shù)行索引i和偶數(shù)像素索引j。 >偶數(shù)行索引i和偶數(shù)像素索引j。

>偶數(shù)行索引i和偶數(shù)像素索引j。 對于奇數(shù)行索引i和偶數(shù)像素索引j。

對于奇數(shù)行索引i和偶數(shù)像素索引j。 對于奇數(shù)行索引i和偶數(shù)像素索引j。

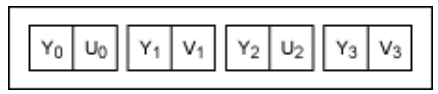

對于奇數(shù)行索引i和偶數(shù)像素索引j。為了降低數(shù)據(jù)速率,利用偶數(shù)像素索引的U數(shù)據(jù)和奇數(shù)像素索引的V數(shù)據(jù),以及偶數(shù)和奇數(shù)像素索引的Y數(shù)據(jù)。壓縮后的YUV數(shù)據(jù)按照圖3所示排列發(fā)送,即:Y1、U0和V1為像素1的數(shù)據(jù);Y2、U2和V1為像素2的數(shù)據(jù)等。

圖3. YUV422數(shù)據(jù)排列

422表示YV的采樣比,4x標(biāo)準(zhǔn)為早期彩色NTSC標(biāo)準(zhǔn),按照41色度再次采樣,所以,圖像的色彩分辨率僅為亮度分辨率的四分之一。目前,只有處理非壓縮信號的高端設(shè)備才會采用44彩色再采樣,亮度和彩色信息的分辨率完全相同。

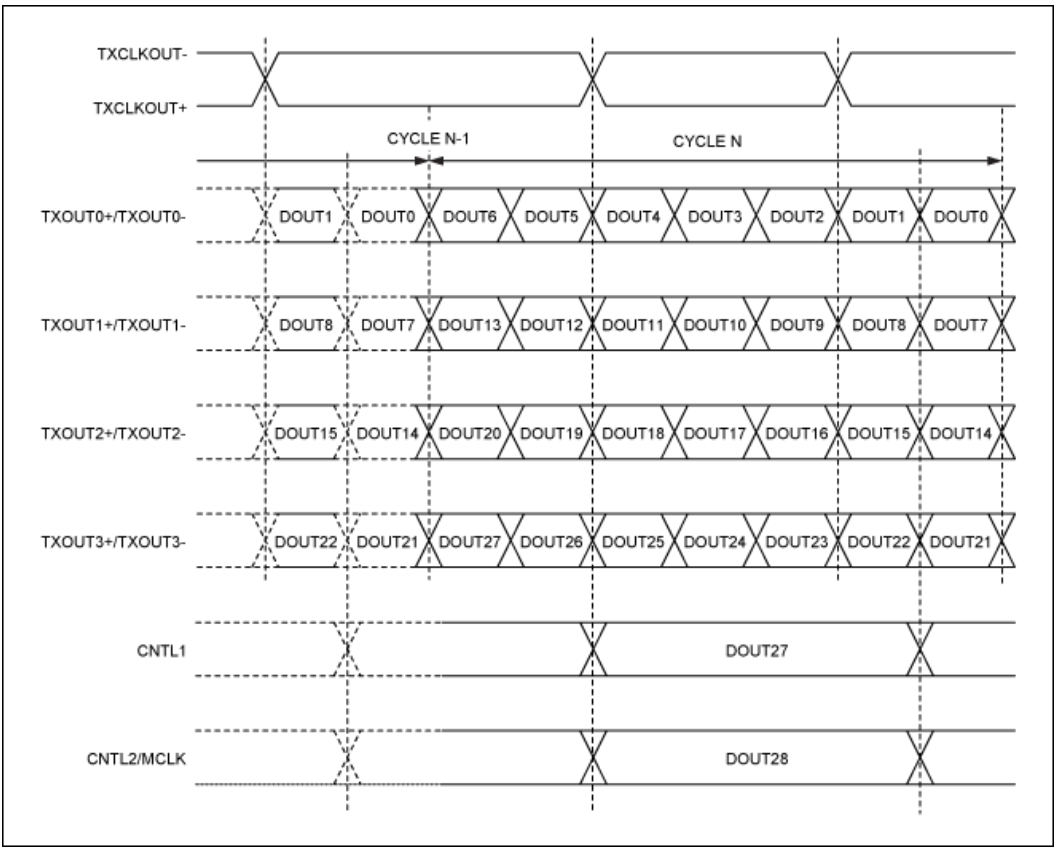

串行器輸入格式 ADI串行器的并行接口設(shè)計(jì)用于24位RGB數(shù)據(jù),特別是MAX9259,具有像素時(shí)鐘位(PCLK)和29個(gè)數(shù)據(jù)位,用于24位RGB以及行同步、場同步和3個(gè)控制位。除并行數(shù)據(jù)接口外,需要把DRS和BWS引腳設(shè)置成高電平或低電平,分別選擇數(shù)據(jù)速率和總線寬度。ADI串行器/解串器 MAX9257和MAX9258串行器/解串器(SerDes)具有18位并行輸入/輸出,適用于YUV數(shù)據(jù)傳輸;MAX9259/MAX9260芯片組具有28位并行輸入/輸出,適用于RGB數(shù)據(jù)傳輸;MAX9263/MAX9264 SerDes具有28位并行輸入/輸出,增加了HDCP功能。此外,MAX9265和MAX9268 28位SerDes帶有攝像鏈路,代替并行輸入/輸出接口。所有28位ADI串行器和解串器具有相同的并/串?dāng)?shù)據(jù)映射,可互換使用。例如,MAX9259串行器可配合MAX9268解串器使用,傳輸RGB數(shù)據(jù)(借助于FPGA)。數(shù)據(jù)從CMOS攝像頭通過串行鏈路發(fā)送至攝像鏈路接口的顯示器。串行器映射 為匹配MAX9268解串器攝像鏈路的輸出接口,并行RGB數(shù)據(jù)應(yīng)按照以下信號圖映射。圖4所示為MAX9268并行位與其攝像鏈路輸出之間的映射,圖5所示為相機(jī)鏈路的RGB數(shù)據(jù)映射。表1所示為MAX9259串行器的對應(yīng)內(nèi)容映射。

圖4. MAX9268內(nèi)部并行至輸出映射

圖4. MAX9268內(nèi)部并行至輸出映射

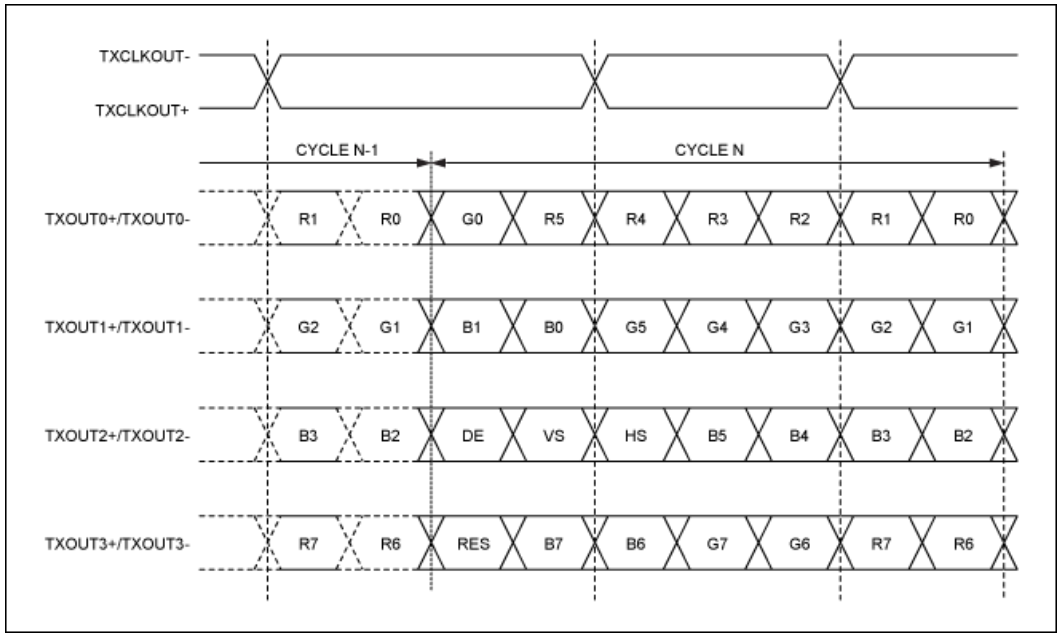

圖5. 攝像鏈路內(nèi)容映射

圖5. 攝像鏈路內(nèi)容映射

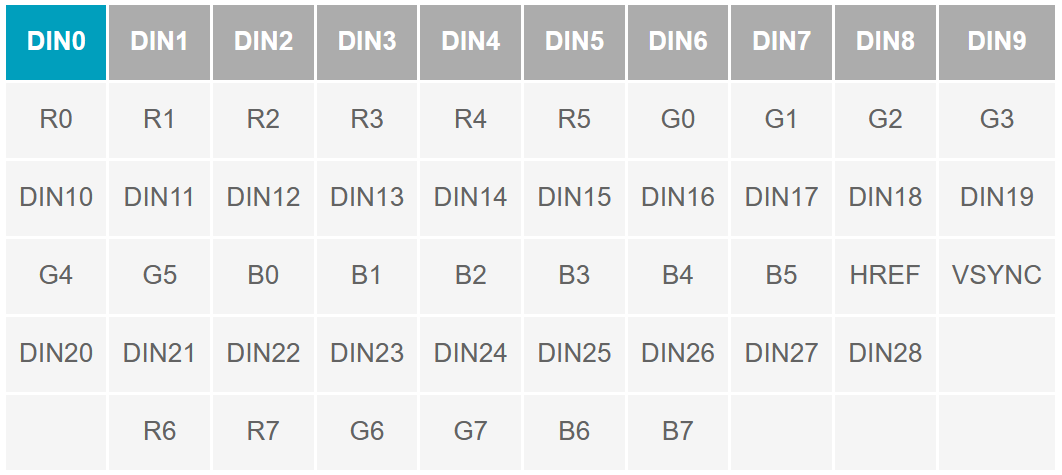

表1. MAX9259串行器RGB內(nèi)容位映射

表1. MAX9259串行器RGB內(nèi)容位映射

FPGA芯片可將壓縮(降低數(shù)據(jù)速率)后的攝像頭數(shù)據(jù)YUV轉(zhuǎn)換成RGB數(shù)據(jù),用于MAX9259串行器。采用8位定點(diǎn)運(yùn)算時(shí),色彩空間轉(zhuǎn)換的公式如下,式2和式3中,Dn和En的n為偶數(shù)。

Cn= Yn- 16

Dn= Dn + 1= Un- 128

En= En + 1= Vn + 1- 128

Rn= clip((298 × Cn+ 409 × En+ 128) >> 8)

Gn= clip((298 × Cn- 100 × Dn- 208 × En+ 128) >> 8)

Bn= clip((298 × Cn× 516 × Dn+ 128) >> 8)

式中,>> 8表示“向右移8位”,clip表示“只取最低8位”。

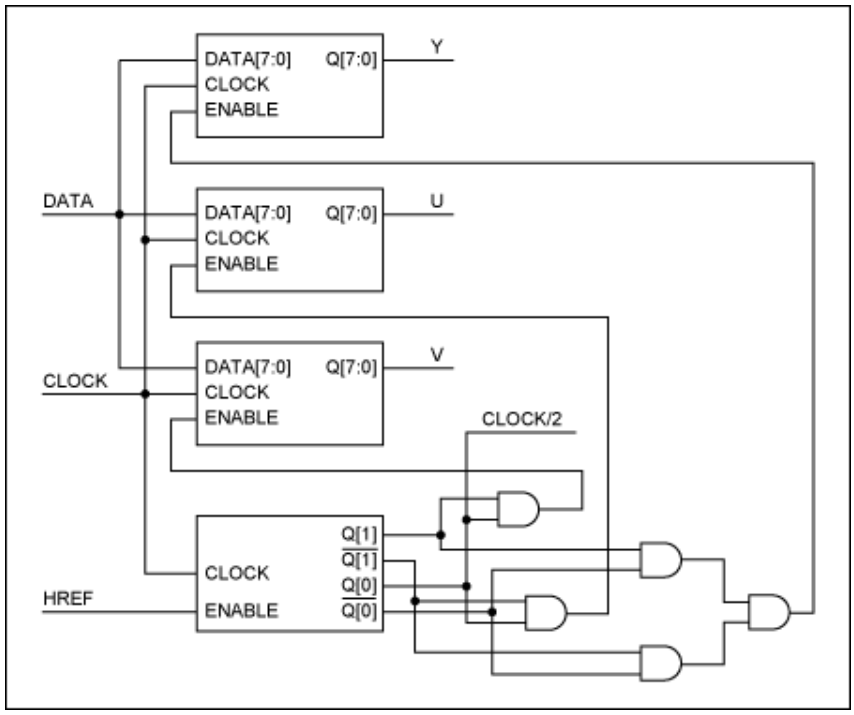

FPGA方案輸入緩沖

輸入緩沖電路包括計(jì)數(shù)器、三個(gè)寄存器和組合邏輯,將單字節(jié)時(shí)鐘輸入轉(zhuǎn)換成三字節(jié)時(shí)鐘輸出,輸出時(shí)鐘速率為輸入的一半。組合邏輯僅用于分別使能Y、U和V字節(jié)的對應(yīng)寄存器。

圖6. 輸入緩沖電路

圖6. 輸入緩沖電路

時(shí)鐘開關(guān)

FPGA輸出像素時(shí)鐘速率為攝像頭像素時(shí)鐘的一半,用于驅(qū)動(dòng)串行器像素時(shí)鐘輸入。但是,攝像頭在初始化之前不會輸出像素時(shí)鐘。解決方案是在FPGA內(nèi)部采用2:1時(shí)鐘復(fù)用器(mux)和時(shí)鐘信號檢測器,mux由時(shí)鐘信號檢測器控制。上電時(shí),mux的默認(rèn)時(shí)鐘來自攝像頭的時(shí)鐘振蕩器,使SerDes芯片組提供啟動(dòng)攝像頭的控制通道。時(shí)鐘信號檢測器對場同步信號脈沖進(jìn)行計(jì)數(shù),經(jīng)過幾個(gè)場同步脈沖后,mux切換到攝像頭像素時(shí)鐘速率的一半。采用高清攝像頭傳感器時(shí),例如OV10630,每個(gè)場同步周期包含100k以上的像素時(shí)鐘。幾個(gè)場同步周期足以使攝像頭的鎖相環(huán)(PLL)達(dá)到穩(wěn)定。場同步計(jì)數(shù)比像素時(shí)鐘計(jì)數(shù)的效率高得多,并可節(jié)省FPGA邏輯單元的資源。中間緩沖

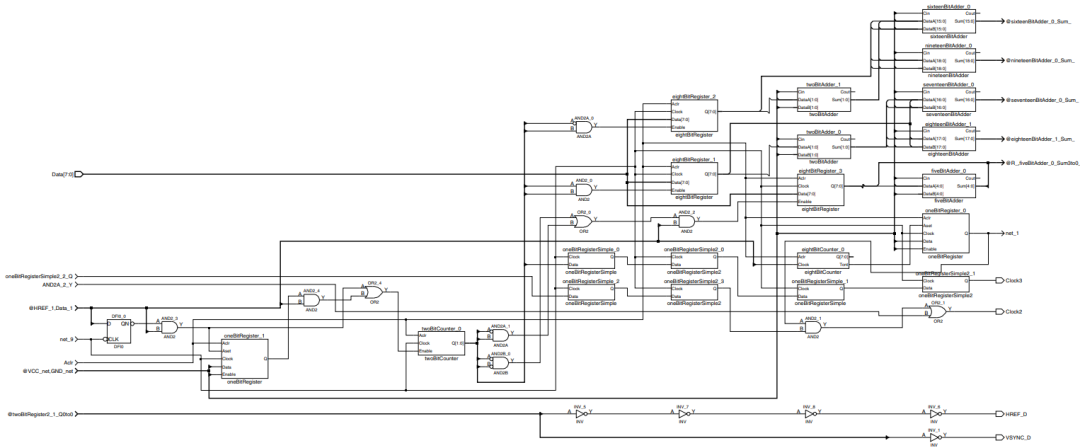

格式轉(zhuǎn)換表達(dá)式中沒有體現(xiàn)硬件電路的延遲。為了從YUV輸入生成RGB數(shù)據(jù),需要兩到三次乘法運(yùn)算和三到四次加法運(yùn)算。盡管FPGA邏輯電路(門電路) 的延時(shí)只有幾個(gè)納秒,但載波傳輸、加法器、移位乘法器都會導(dǎo)致不同程度的延時(shí),使整體延時(shí)增大。為了使延遲最小化,每個(gè)常數(shù)乘法器均由兩個(gè)移位輸入(代表常數(shù)的2個(gè)非零最高有效位MSB)的加法器近似。輸入的YUV字節(jié)速率大約為100MHz時(shí),延遲會跨越相鄰像素的定時(shí)邊界,增大圖像噪聲。在每個(gè)乘法器之后通過中間寄存器來消除擴(kuò)展延時(shí)。 以上提及的YUV至RGB彩色轉(zhuǎn)換已用于ActelProASIC3 A3PN125Z FPGA,圖7所示為實(shí)現(xiàn)這一FPGA的原理圖。

圖7. YUV至RGB轉(zhuǎn)換器的FPGA實(shí)現(xiàn)

圖7. YUV至RGB轉(zhuǎn)換器的FPGA實(shí)現(xiàn)

應(yīng)用電路

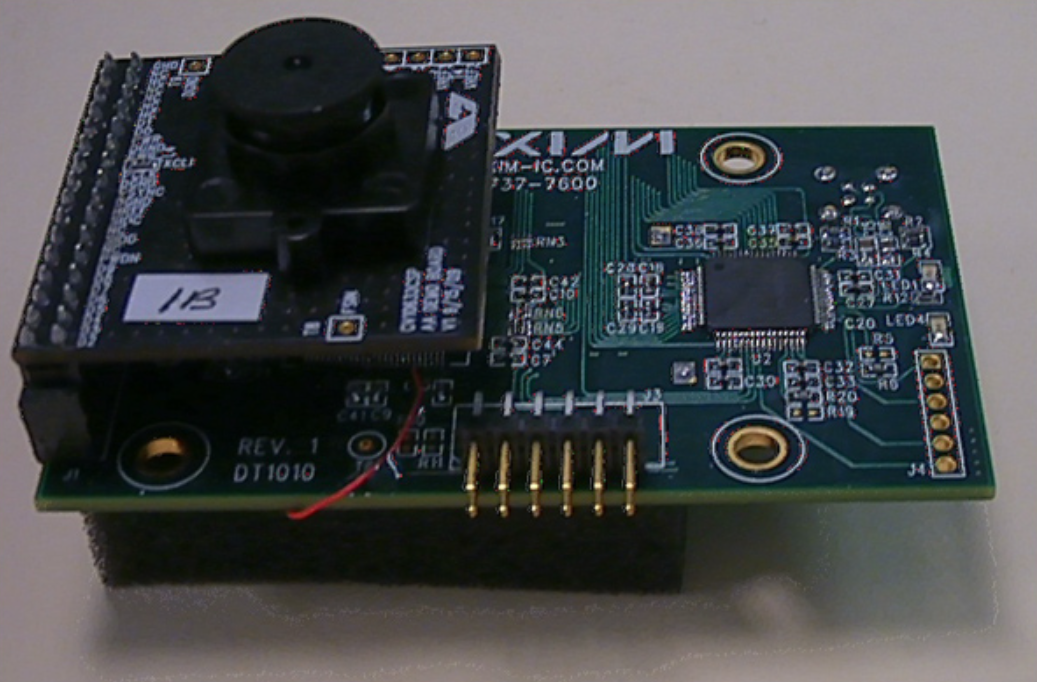

廠家提供的攝像頭芯片可能位于PCB子板,圖8所示為攝像頭子板模塊的功能框圖。輸入包括電源、PWR和晶振時(shí)鐘(XCLK)。輸出信號包含并行數(shù)據(jù)位(D0..D9)、I2C總線(SDA、SCL)、視頻同步(HREF、VSYNC)和像素時(shí)鐘(PCLK)。

圖8. 攝像頭模塊功能框圖

圖8. 攝像頭模塊功能框圖

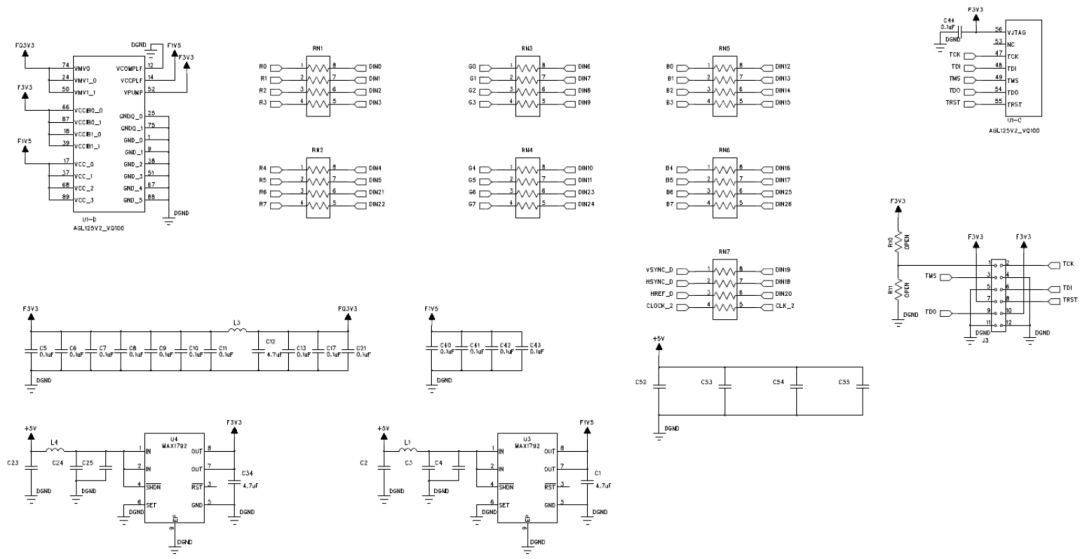

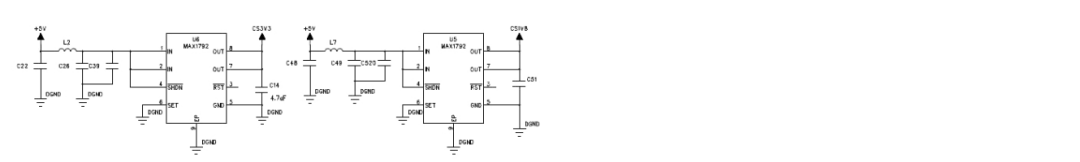

圖9a. 應(yīng)用電路的FPGA部分

圖9a. 應(yīng)用電路的FPGA部分

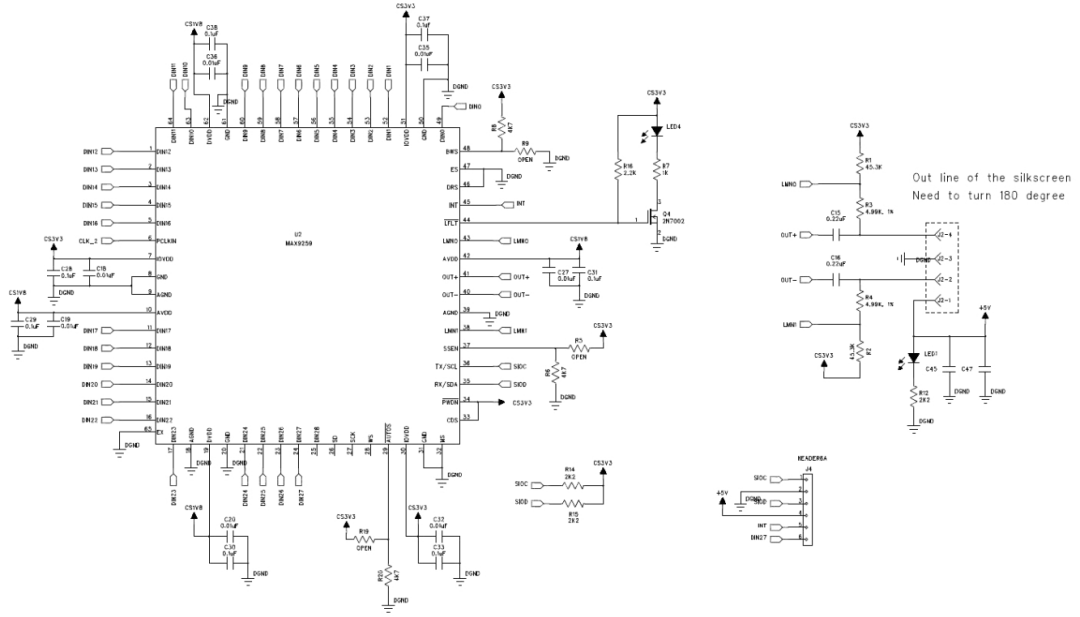

圖9b. 應(yīng)用電路的串行器部分

MAX9259也能夠直接連接至攝像頭傳感器,例如OV10630,以構(gòu)建更小的攝像頭。彩色空間轉(zhuǎn)換FPGA可置于解串器之后。由于這種應(yīng)用需要攝像鏈路輸出,可直接由MAX9268驅(qū)動(dòng),所以彩色轉(zhuǎn)換FPGA置于攝像頭傳感器和串行器(MAX9259)之間。視頻采集示例

圖10所示攝像頭應(yīng)用電路也是利用這些攝像頭電路搭建的。

圖10. 攝像頭應(yīng)用電路

-

CMOS

+關(guān)注

關(guān)注

58文章

5988瀏覽量

238068 -

ADI

+關(guān)注

關(guān)注

148文章

46023瀏覽量

258624 -

攝像頭

+關(guān)注

關(guān)注

61文章

4949瀏覽量

97659 -

串行器

+關(guān)注

關(guān)注

0文章

159瀏覽量

14857 -

亞德諾

+關(guān)注

關(guān)注

6文章

4680瀏覽量

16235

原文標(biāo)題:串行器應(yīng)用之如何將攝像頭的RGB或YUV輸出轉(zhuǎn)換成RGB數(shù)據(jù)?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

TSH8135的三組數(shù)據(jù)線輸入,分別對應(yīng)的RGB的數(shù)據(jù)?還是需要轉(zhuǎn)換成YCbCr信號?

LMH03XX可以輸出YUV信號,但并不直接輸出RGB信號,是否有相關(guān)的產(chǎn)品方案?

米爾-Xilinx XC7A100T FPGA開發(fā)板試用

用DS90C387將RGB信號轉(zhuǎn)換成LVDS信號,顯示花屏,可能是哪里的問題呢?

TFP401APZP將DVI信號轉(zhuǎn)換成TTL RGB信號,輸出的TTL RGB信號測量的波形就是3.3v高電平,為什么?

攝像頭及紅外成像的基本工作原理

BT656RGB888YUV422等數(shù)字信號轉(zhuǎn)HDMI發(fā)送芯片CV9887

飛凌嵌入式-ELBOARD-RGB LCD顯示屏接口的PCB設(shè)計(jì)要點(diǎn)

《DNK210使用指南 -CanMV版 V1.0》第二十六章 攝像頭圖像捕獲實(shí)驗(yàn)

LT9211C轉(zhuǎn)換器英文手冊

在DRA7xx器件上使用DSS回寫管道進(jìn)行RGB到YUV轉(zhuǎn)換

串行器應(yīng)用之如何將攝像頭的RGB或YUV輸出轉(zhuǎn)換成RGB數(shù)據(jù)?

串行器應(yīng)用之如何將攝像頭的RGB或YUV輸出轉(zhuǎn)換成RGB數(shù)據(jù)?

評論