之前有人問題易靈思的BRAM是否可以修改ROM的初始化參數(shù),像xilinx一樣不需要編譯,也有人問RISC 修改了bootloader有沒有辦法不用重新編譯,在之前確實(shí)不行。不過易靈思2023.1.150軟件這周發(fā)布了,增加了一些新的功能,其中就有客戶提到的上面的問題的解決方法。

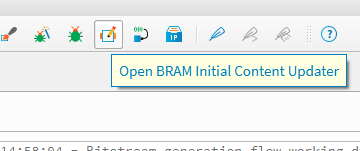

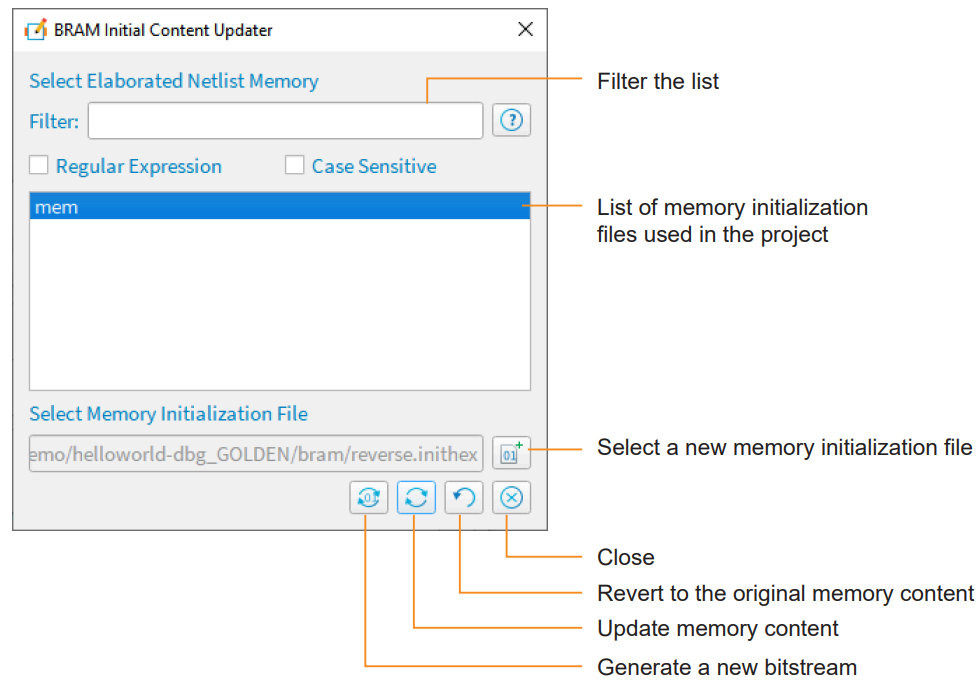

新軟件增加了一個(gè)功能叫Open BRAM Initial Content Updater。它可以讓用戶快速更新BRAM初始化的數(shù)據(jù)而不需要全編譯。它是更新elaborated網(wǎng)表的數(shù)據(jù),

說明:--optimize-zero-init-rom綜合選項(xiàng)是告訴軟件優(yōu)化初始化值為0的ROM的,如果你的ROM初始值是0,又想通過Open BRAM Initial Content Updater工具來修改初始值,需要把--optimize-zero-init-rom選項(xiàng)Disable。

RISCV片上ROM更新

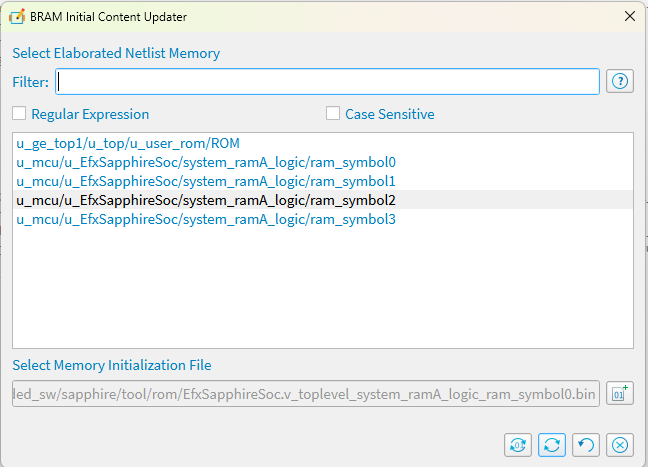

(1)當(dāng)工程編譯完成之后,打開該工具就可以看到可以初始化的BRAM塊。其中ram_symbol0,1,2,3就是RISCV的初始化文件。用戶只需要選擇相應(yīng)的文件,然后再點(diǎn)擊Update memory content就會(huì)把初始化文件更新掉,RISCV有4個(gè)bin文件,所以要對(duì)每個(gè)bin文件都進(jìn)行更新。

至于怎么生成要更新的bin文件,之前寫過

自定義RISC V的bootloader(1) (qq.com)

有一種老的生成bootloader的辦法用在這里。

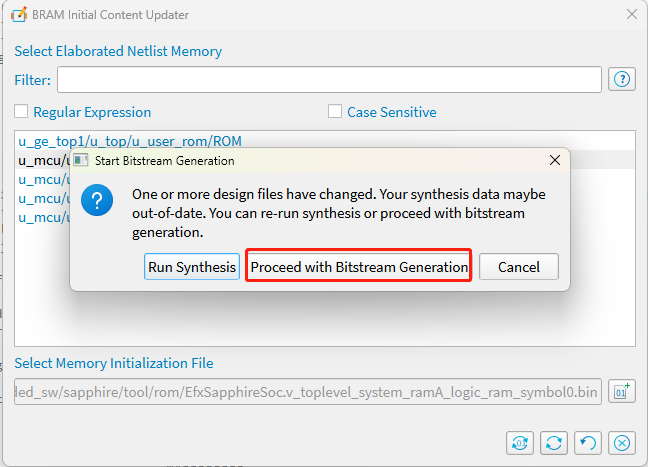

(2)當(dāng)4個(gè)文件都更新完成之后點(diǎn)擊Genarate a new Bitstream,就會(huì)有提示是否要重樣綜合還是繼續(xù)生成Bitstream的過程,按下圖選擇Proceed with Bitstream Generation.軟件會(huì)運(yùn)行最后一步生成新的bit流。

(3)用新生成的數(shù)據(jù)流就可以重新下載看效果了。新生成的文件不會(huì)影響debug。

一般ROM的初始化

在Efinity的安裝目錄下提供了一個(gè)T20的參考工程。

/debugger/demo/helloworlddbg_GOLD

我把它修改成了Ti60F225的demo工程(因?yàn)槭稚蠜]有T20的demo板)

鏈接:https://pan.baidu.com/s/106I_xipVjXc1sfV9c5982A?pwd=1234

提取碼:1234

具體的操作步驟請(qǐng)參考efinity-ug.pdf的About the BRAM Initial Content Updater部分,有詳細(xì)的說明,這里先不贅述。

-

Xilinx

+關(guān)注

關(guān)注

73文章

2185瀏覽量

125340 -

IDE

+關(guān)注

關(guān)注

0文章

352瀏覽量

47755 -

RISC

+關(guān)注

關(guān)注

6文章

482瀏覽量

84992 -

BRAM

+關(guān)注

關(guān)注

0文章

41瀏覽量

11309 -

易靈思

+關(guān)注

關(guān)注

5文章

57瀏覽量

5219

原文標(biāo)題:易靈思IDE更新ROM可以不用全編譯了

文章出處:【微信號(hào):gh_ea2445df5d2a,微信公眾號(hào):FPGA及視頻處理】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

玩轉(zhuǎn)FPGA,賽靈思FPGA設(shè)計(jì)大賽開賽啦

【芯靈思A83T試用體驗(yàn)】安卓源碼編譯打包教程

易靈思推Trion Titanium FPGA,采用 “Quantum? 計(jì)算架構(gòu)”

AMD同意以350億美元的全股票交易收購賽靈思

易靈思Programmer工具的配置模式過程分析

易靈思MIPI CSI自環(huán)調(diào)試步驟

易靈思FPGA之---國產(chǎn)化替代選型策略

易靈思FPGA軟件更新的節(jié)奏,也許能磨出一個(gè)好產(chǎn)品

易靈思RAM使用--Update3

易靈思FPGA產(chǎn)品的主要特點(diǎn)

易靈思IDE更新ROM可以不用全編譯了

易靈思IDE更新ROM可以不用全編譯了

評(píng)論