-

本文要點(diǎn)

理解電路中的雜散電容。

了解雜散電容如何影響電子電路。

探索減少電路中雜散電容的策略。

雜散電容就像被遺棄的寵物流浪在街道和巷子里一樣,它們潛伏在電路中。本文將了解電子電路中的雜散電容是如何產(chǎn)生的、如何影響電路的性能,以及如何在設(shè)計(jì)中減少雜散電容。

什么是雜散電容?

基礎(chǔ)電子學(xué)對(duì)電容的定義是:在具有不同電壓電位的兩個(gè)端點(diǎn)上積累的電荷的測(cè)量值。這也是電容器的制造原理。雜散電容是指電路或非電容性元件中出現(xiàn)了預(yù)期之外的電荷。

就像流浪的狗或貓一樣,雜散電容只是由于環(huán)境的原因而恰好出現(xiàn)在那里。在電路上制造雜散電容是很容易的。所需的只是兩個(gè)導(dǎo)電元件,它們?cè)诮^緣體上足夠封閉,因而表現(xiàn)得像一個(gè)電容器。

雜散電容就像是電路上存在著看不見的電容。

雜散電容可能存在于電感、晶體管或二極管等元件上。即使是 PCB 上的兩個(gè)平行導(dǎo)體,也總會(huì)有一些雜散電容存在。我們也會(huì)在導(dǎo)體中發(fā)現(xiàn)相對(duì)于接地面的雜散電容。

在書面上,雜散電容用公式 C = Q/V 表示,用于測(cè)量微分電位上積累的電荷。在 PCB 設(shè)計(jì)中,我們會(huì)發(fā)現(xiàn)公式 C= ?A/D,體現(xiàn)了絕緣體的介電常數(shù)、面積和導(dǎo)體之間的距離與電容值的關(guān)系。

雜散電容是否會(huì)影響電路性能?

大多數(shù)流浪的動(dòng)物通常沒有什么危害。雜散電容的影響則取決于頻率。如果在電路上放置一個(gè)電容器,在低頻下,電容器會(huì)造成開路。隨著頻率的增加,電容器會(huì)逐漸允許電流通過。

雜散電容的影響在高頻率下十分明顯。

因此,如果我們正在進(jìn)行低頻設(shè)計(jì),雜散電容并不會(huì)造成嚴(yán)重問題。例如,一個(gè)簡(jiǎn)單的 LED 閃光燈不會(huì)受到雜散電容的影響。當(dāng)設(shè)計(jì)涉及到高頻時(shí),問題會(huì)悄然而至,這可能會(huì)大大降低雜散電容的電抗。

在高頻率下,具有雜散電容的元件往往像短路或虛擬電阻一樣。雜散電容的影響是運(yùn)算放大器設(shè)計(jì)中一個(gè)難題,特別是在放大器的輸入和輸出之間。雜散電容創(chuàng)造了一個(gè)反饋路徑,會(huì)不準(zhǔn)確地增加增益和改變峰值頻率。

在傳輸線中,導(dǎo)體之間的雜散電容會(huì)導(dǎo)致傳輸損失。這意味著傳輸功率和信號(hào)質(zhì)量會(huì)下降。雜散電容也會(huì)在導(dǎo)體和相鄰的接地平面之間產(chǎn)生,這將導(dǎo)致高頻率下出現(xiàn)信號(hào)完整性問題。多余的電容也會(huì)造成串?dāng)_和 EMI 噪聲。

如何減少雜散電容?

我們并非對(duì)雜散電容束手無策。雖然雜散電容不能完全消除,但有一些方法可以將電路中的雜散電容降到最低。

1. 讓導(dǎo)體彼此分開

無論是 PCB 上的走線還是并排放置的電纜,都可以通過增加它們之間的距離來減少雜散電容。電容與距離成反比,這是減少雜散電容的一條重要原則。

讓銅走線彼此分開可以將雜散電容降到最低。

2. 屏蔽導(dǎo)體

如果擔(dān)心相鄰的走線會(huì)產(chǎn)生雜散電容,可以在走線之間增加一條接地的銅線。該銅線可以發(fā)揮屏蔽作用,進(jìn)而防止電荷堆積。

3. 減少走線寬度

當(dāng)導(dǎo)體的橫截面積增加時(shí),電容也會(huì)增加。因此,要盡量減少走線寬度,尤其是傳導(dǎo)高頻信號(hào)的走線。

4. 移除內(nèi)層接地平面

大片的內(nèi)層接地平面可能有助于散熱和降低 EMI,但卻不利于減少雜散電容。在為設(shè)計(jì)添加接地平面時(shí),一定要考慮到這一點(diǎn)。

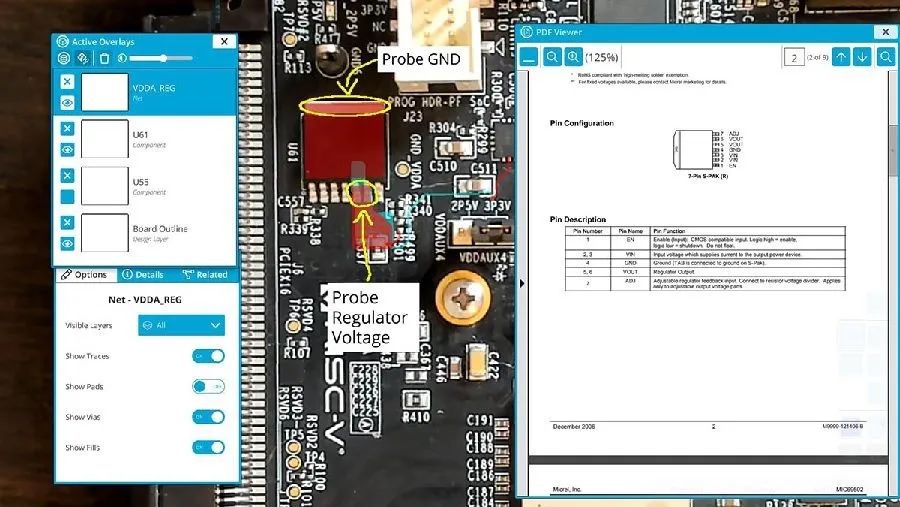

借助合適的 PCB 設(shè)計(jì)軟件,可以確保電路設(shè)計(jì)不受雜散電容的影響。通過使用 inspectAR工具,利用增強(qiáng)現(xiàn)實(shí)(AR)技術(shù)以交互性的方式評(píng)估和改進(jìn) PCB,輕松準(zhǔn)確地進(jìn)行 PCB 檢查、調(diào)試、返工和組裝。

inspectAR軟件中直接將 AR 疊層對(duì)應(yīng)在 PCBA物理板上

上圖顯示了inspectAR 軟件中 AR 疊層制造的 PCBA物理板的交互。利用AR技術(shù),工程師或制造技術(shù)人員可以在制造過程中的任何時(shí)候?qū)蝹€(gè)器件、走線、子電路或整個(gè)電路板與設(shè)計(jì)規(guī)格進(jìn)行比較,并隨時(shí)查看技術(shù)手冊(cè)、添加留言、注釋。

-

電容

+關(guān)注

關(guān)注

100文章

6227瀏覽量

153152 -

電子電路

+關(guān)注

關(guān)注

78文章

1242瀏覽量

67640

發(fā)布評(píng)論請(qǐng)先 登錄

如何抑制電子電路中的噪聲

ADC10D1500采樣數(shù)據(jù)雜散的原因?

ADS5407雜散較差的原因?

邊帶雜散和開關(guān)雜散的含義是什么?會(huì)對(duì)電路造成什么影響?

DAC3482存在雜散怎么解決?

DAC39J82輸出信號(hào)在140MHz頻率存在雜散怎么解決?

LMX2594如何降低整數(shù)邊界雜散?

請(qǐng)問LMX2694-EP輸出信號(hào)中有小數(shù)分頻雜散該如何解決?

電子電路中的地是什么?什么是數(shù)字地和模擬地

雜散有什么影響?雜散從哪里來?

時(shí)鐘雜散對(duì)高速DAC性能的影響

最大限度地提高GSPS ADC中的SFDR性能:雜散源和Mitigat方法

深入解析晶振時(shí)鐘信號(hào)干擾源:寄生電容、雜散電容與分布電容

什么是無雜散動(dòng)態(tài)范圍 (SFDR)?為什么 SFDR 很重要?

LMX2531整數(shù)雜散優(yōu)化的案例分析

技術(shù)資訊 | 如何減少電子電路中的雜散電容

技術(shù)資訊 | 如何減少電子電路中的雜散電容

評(píng)論