一、 前言

G9X 系列處理器是專為新一代車內核心網關設計的高性能車規級汽車芯片,采用雙內核異構設計,包含一個高性能的 Cortex-A55 CPU 內核,一對雙核鎖步的高可靠 Cortex-R5 內核,在支持多種外設接口,包括兩個 PCIe3.0 接口,兩個 USB3.0 接口, 兩個支持 TSN 的千兆以太網接口,以及多達 20 個 CAN-FD 接口和 16 個 UART 接口。承載未來網關豐富的應用同時,也能滿足高功能安全級別和可靠性的要求。

① G9X 系列處理器中,DRAM 接口 16位,支持 LPDDR4 和 LPDDR4X。

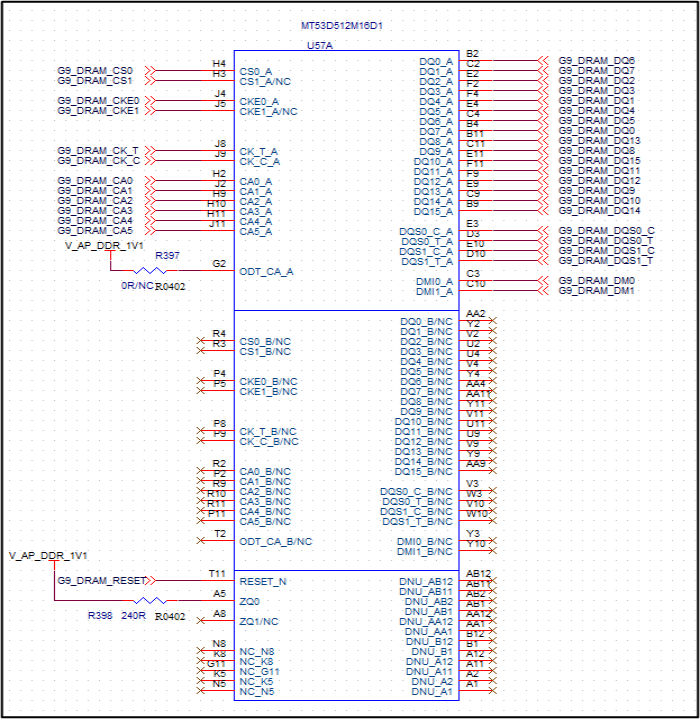

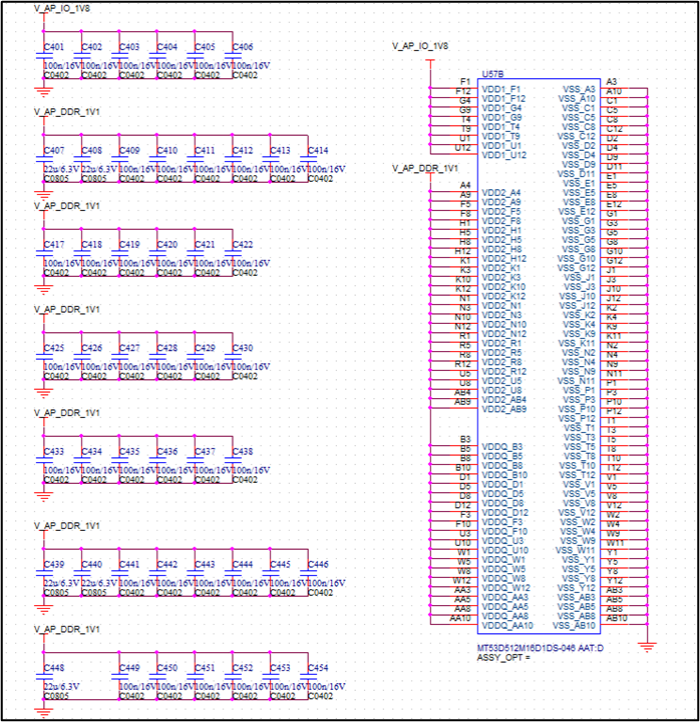

②LPDDR4 我們選用的是 Micron 的 MT53D512M16D1DS-046 AAT:D,封裝 WFBGA200 的車規級芯片。

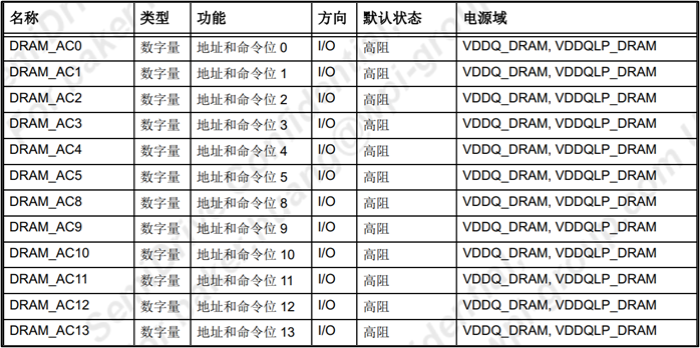

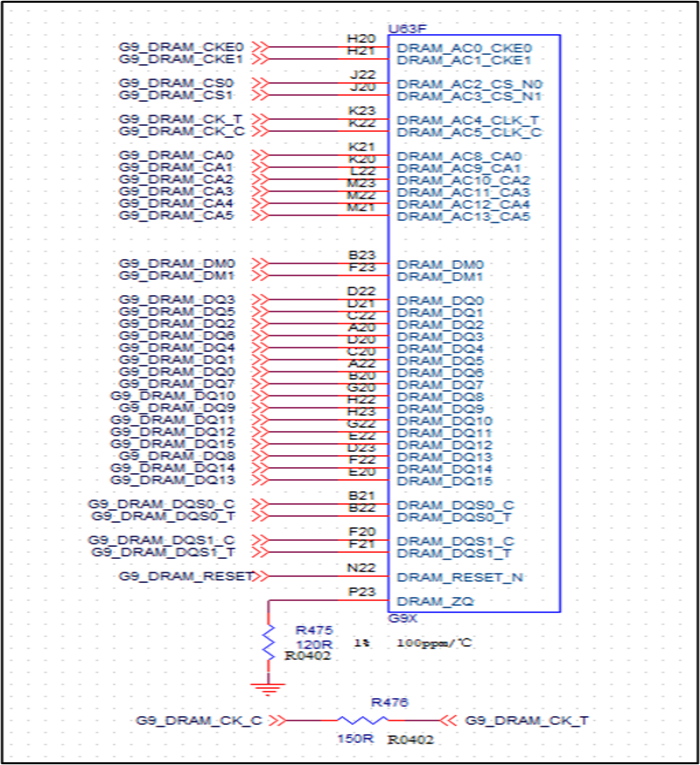

③ G9X 端 DRAM 引腳描述

▲ 圖1 G9X 端引腳描述

▲ 圖2 G9X 端引腳描述

▲ 圖3 G9X 端引腳描述

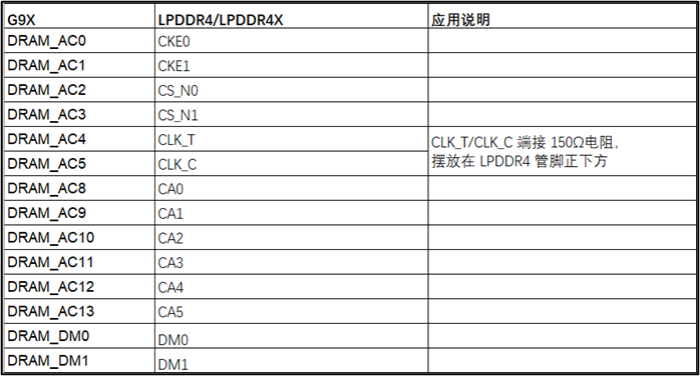

④ G9X 端與 LPDDR4 端的地址與控制命令對應連接如下,CLK_T/CLK_C 端接 150Ω 電阻,擺放在 LPDDR4 管腳正下方。

▲ 圖4 G9X 與 LPDDR4 控制端連接關系

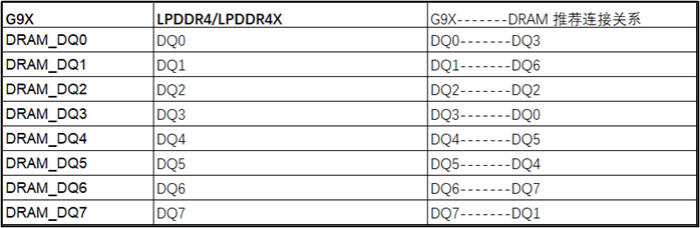

⑤ G9X 的 DQ [7:0] 數據線與 DRAM 的 DQ [7:0] 數據線可以亂序連接,推薦連接關系如下圖示。

▲ 圖5 G9X 與 LPDDR4 數據端連接關系

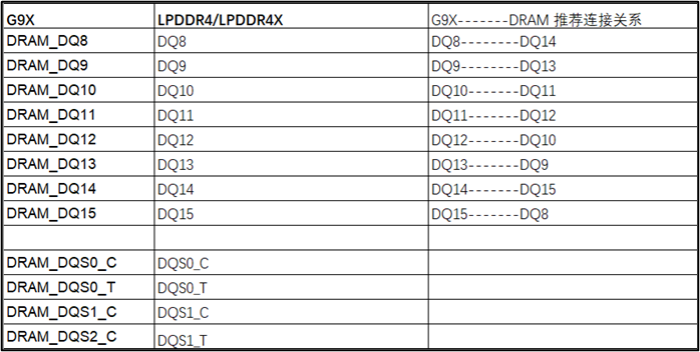

⑥ G9X 的 DQ [15:8] 數據線與 DRAM 的 DQ [15:8] 數據線可以亂序連接,推薦連接關系如下圖示,

▲ 圖6 G9X 與 LPDDR4 數據端連接關系

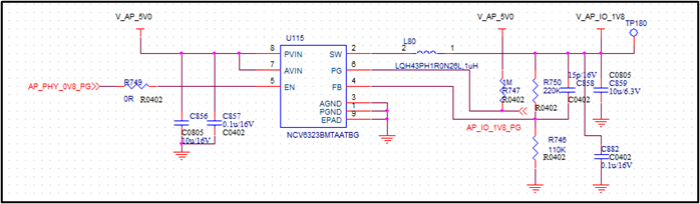

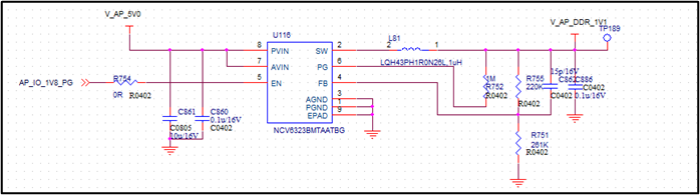

⑦ LPDDR4 的供電需要 1.8V 和 1.1V。供電時序是 1.8V 先于 1.1V,也可以兩路電壓同時上電,具體電路如下。

▲ 圖7 LPDDR4 1.8V 供電

▲ 圖8 LPDDR4 1.1V 供電

⑧ G9X 端原理圖

▲ 圖9 G9X 端原理圖

⑨ LPDDR4 端原理圖

▲ 圖 10 LPDDR4 端信號連接

▲ 圖 11 LPDDR4 端電源連接

三、PCB 設計建議

① 總線阻抗,按單端信號 40Ω,差分信號 80Ω 設計,如果做不到可按單端信號 50Ω,差分信號 100Ω 設計,保證信號完整性。

② CA [5:0]、CKE0、CKE1、CK_C、CK_T、CS0、CS1 布線要做等長,誤差 30mil。

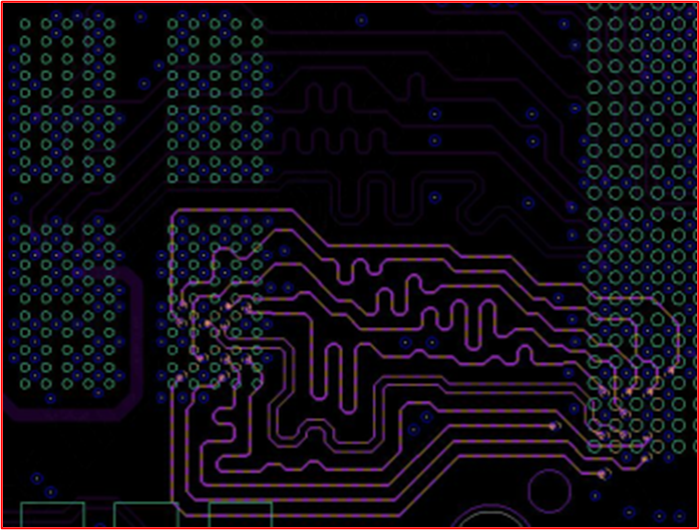

③ DM0、DQS0_C、DQS0_T、DQ [7:0] 在同一層布線并且要做等長,誤差 30mil。

▲ 圖12 DQ [7:0] 走線圖

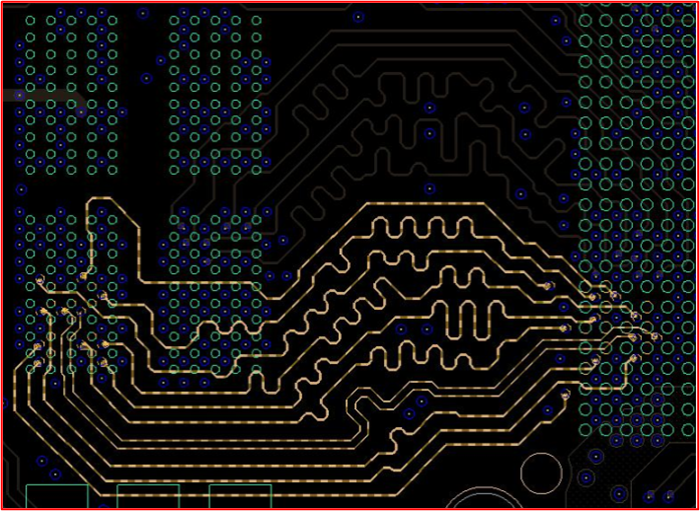

④ DM1、DQS1_C、DQS1_T、DQ [15:8] 在同一層布線并且要做等長,誤差 30mil。

▲ 圖13 DQ [15:8] 走線圖

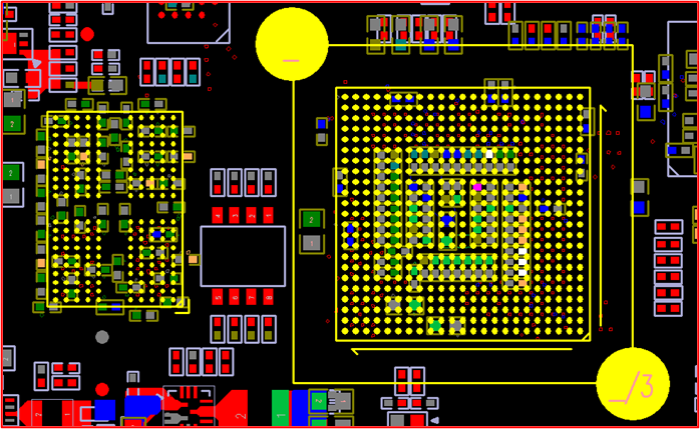

⑤ LPDDR4 應靠近 G9X 擺放,去耦電容靠近 LPDDR4 電源管腳擺放。

▲ 圖14 去耦電容及 LPDDR4 擺放位置

以上便是芯馳 SEMIDRIVE G9X DRAM 電路設計要點。

接下來我們也會不斷更新更多關于 SEMIDRIVE X9、G9 系列的開發博文,同時我們也會持續推出更多 ADAS相關的技術開發博文。如需更深入的技術交流,歡迎在博文下方評論或者關注并給我留言。

附錄:參考文獻

①《 G9X 處理器硬件設計指南_Rev0.9.2 》

②《 SD004_G9X_REF_A03_SCH 》

③《 SD004_G9X_REF_A03_PCB 》

-

電路設計

+關注

關注

6697文章

2518瀏覽量

210563

發布評論請先 登錄

智能工業與電力通訊管理機:基于Semidrive D9342的創新應用方案

學電路設計分享學習心得、技術疑問及實戰成果

武漢 7月11日-12日《電子電路設計、測試與故障定位技術》公開課即將開始!

學電路設計分享學習心得、技術疑問及實戰成果,贏取專屬禮品!

跟著華為學硬件電路設計,華為全套硬件電路設計學習資料都在這里了!

DRAM基本單元最為通俗易懂的圖文解說

《典型電子電路設計與測試》閱讀體驗

9個開關電源電路設計項目

汽車安全再進化 - SemiDrive X9HP 與環景影像系統 AVM 的系統整合

4G模組SIM卡接口電路設計:從入門到精通

使用LP875230C-Q1 和 LP87565V-Q1 的 Semidrive X9H 電源設計

SemiDrive X9 AI 開發環境搭建

學技術 | SEMIDRIVE G9X DRAM 電路設計要點

學技術 | SEMIDRIVE G9X DRAM 電路設計要點

評論