Allegro和 Sigrity 軟件最新發布了一系列的產品更新(SPB17.4 QIR4 release)。我們將通過實例講解、視頻演示讓您深入了解 Allegro PCB Editor、Allegro System Capture、Allegro Package Designer Plus(本期內容)、Sigrity Aurora(本期內容)、Sigrity SystemSI、Sigrity SystemPI等產品的新功能及用法,助力提升設計質量和設計效率。

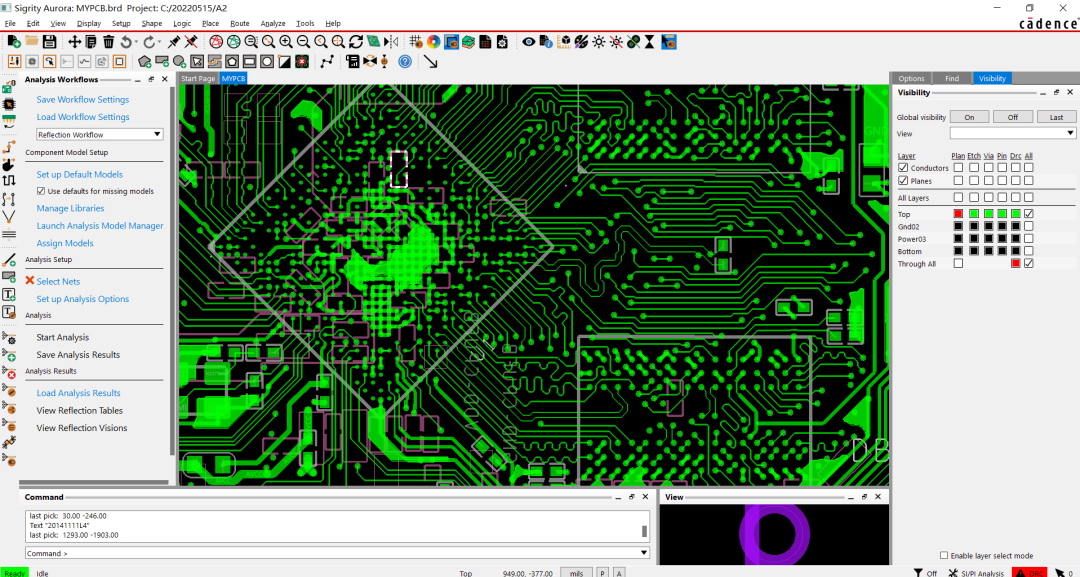

Cadence Sigrity Aurora 為 PCB 設計前、設計中和布局后提供傳統的信號和電源完整性 (SI/PI) 分析,結合 Cadence Allegro PCB 編輯和布線技術,Sigrity Aurora用戶在設計初期就可以使用 “What-if” 探索環境進行分析,從而獲得更準確的設計約束并減少設計迭代。

Sigrity Aurora 直接讀寫 Allegro PCB 數據庫,可快速準確地整合設計和分析結果。它提供了一個基于 SPICE 仿真器和獲得專利的 Sigrity 嵌入式混合場求解器,用于二維和三維結構提取。同時支持兼顧電源影響(Power-Aware)的 IBIS 模型,如需要還支持晶體管級別的模型。高速信號可以在布局階段中或布局階段后,對比備選方案進行研究,以便對所有相關信號進行全面分析。

在最新的 SPB 17.4 版本中,Cadence Sigrity Aurora 主要在以下幾個方面對互連建模的仿真功能進行了更新:

支持對未布線網絡的拓撲提取及建模:支持布線前按照預拉線曼哈頓長度拓撲提取,并進行信號互連搭建,進行信號完整性仿真分析。

支持 Clarity 3D Solver 和 Sigrity PowerSI 引擎直接集成:在 Aurora 環境中,可以通過選擇需要提取的網絡調用 Clarity3D Solver 和 Sigrity PowerSI 引擎進行 S參數 的仿真建模。

IR Drop 直流電壓降仿真支持自動剪切功能:自動剪切功能,可以加快仿真的速度,針對大型 PCB 的區域分析及部分電路仿真提升仿真的速度。

新增生成同軸電纜和雙絞線電纜的模型:生成同軸電纜和雙絞線建模,支持框架及及參數建模和自定義參數建模的辦法,通過修改編輯支持直接進行信號互連拓撲及信號互連仿真。

Sigrity Aurora

互連建模仿真亮點——

#2 支持 Clarity 3D Solver 和 Sigrity PowerSI 引擎直接集成

Aurora_TopWbench_SPB17.4 更新之后,Clarity 3D Solver 和 Sigrity PowerSI 引擎直接集成到 Allegro 環境中,可以通過選擇需要提取的網絡調用 Clarity3D Solver 和 Sigrity PowerSI 引擎進行 S參數 的仿真建模。

接下來我們使用一個實例文件來講解 S參數 的仿真建模方法。

1?

實例講解 · 視頻版

建議在WIFI環境下觀看,并注意調整音量

2?

實例講解 · 圖文版

1

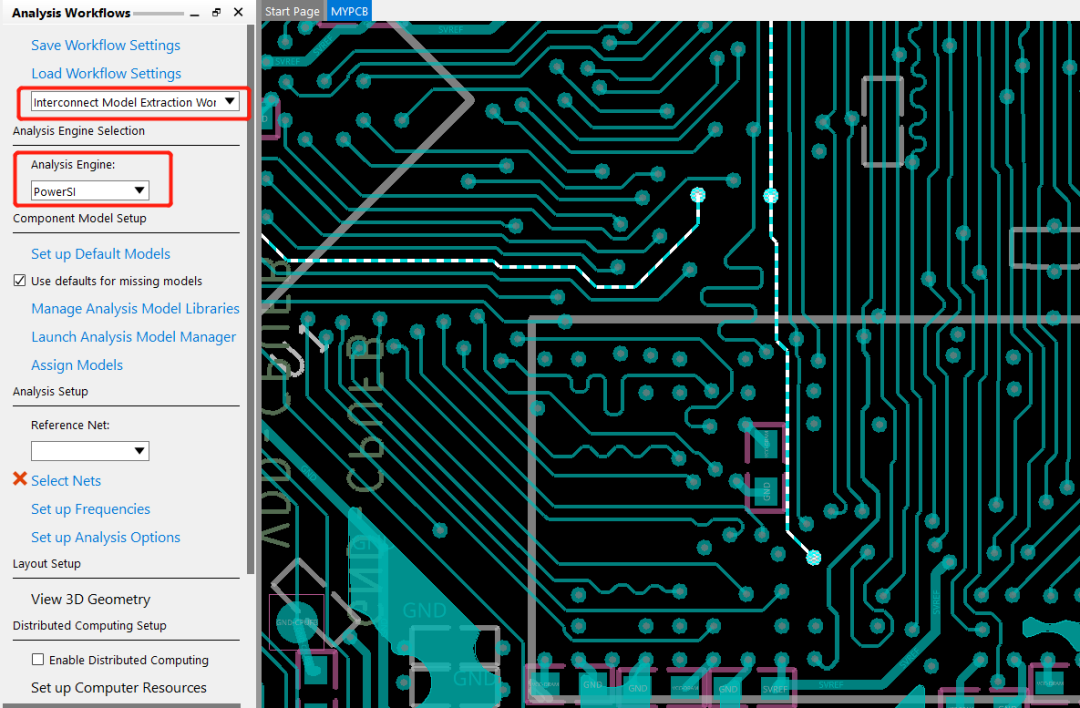

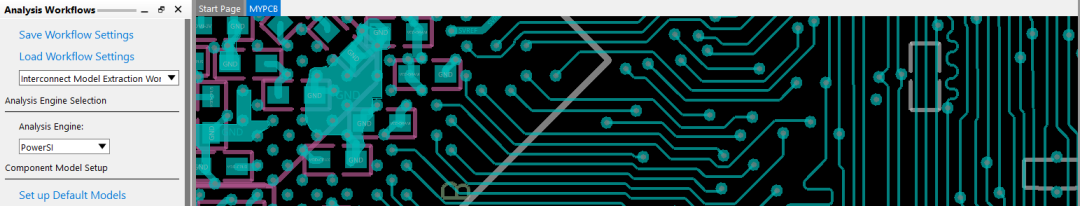

在 Analysis Workflows 流程中選擇 Interconnect Model Extraction Workflows 傳輸線提取流程,進行S參數提取。

2

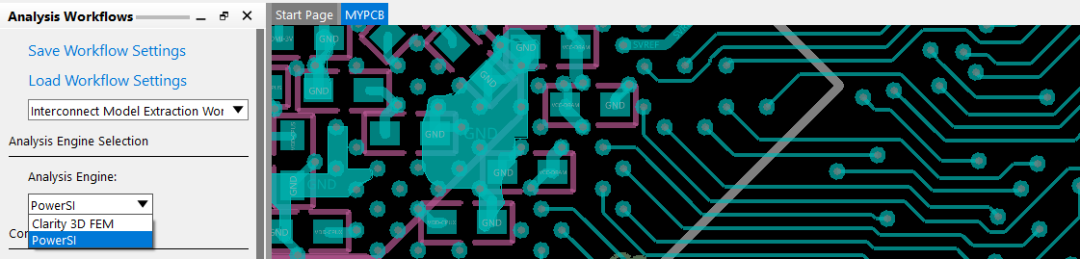

Analisis Engine Selection 選擇分析的引擎為 Sigrity PowerSI。

3

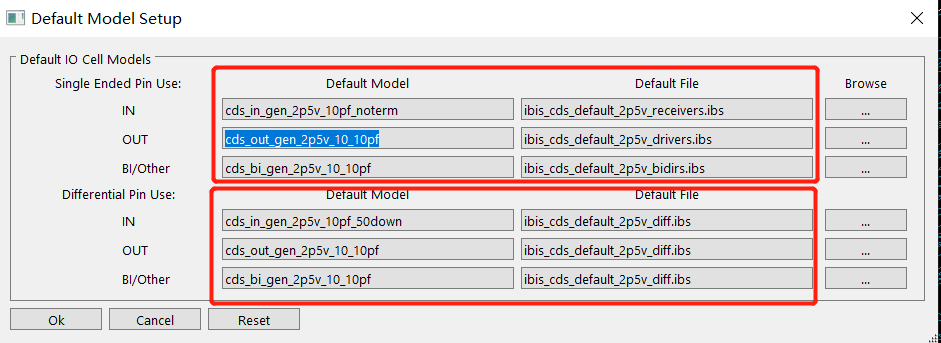

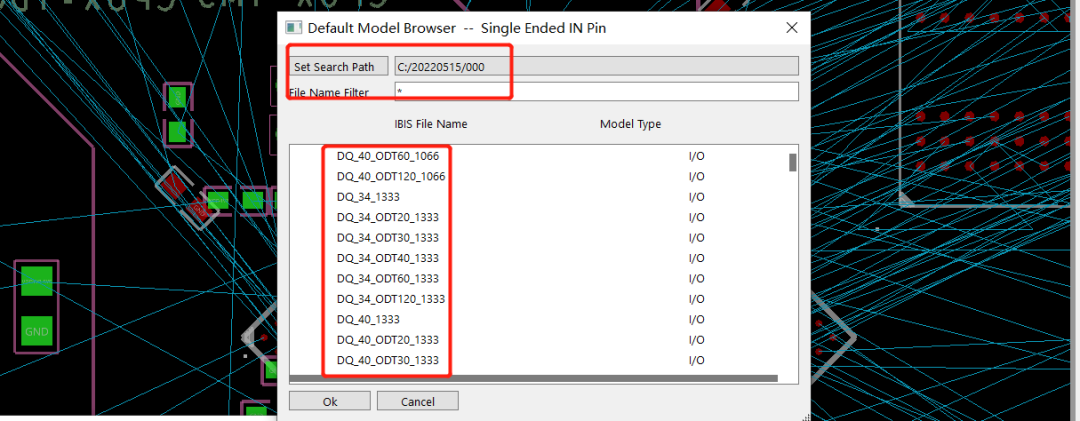

Component Model Setup 用來設置元件模型的參數配置, Set up Default Models 用來配置默認的元件模型。Single Ended Pin Use 設置單端口網絡引腳設置, IN 輸入引腳模式設置, OUT 輸出模型設置, BI/Other 橋接其他模型設置。Differential Pin Use 設置差分端口網絡引腳設置,允許瀏覽 IBIS 文件修改輸入、輸出、橋接的 GPIO 引腳模型。

4

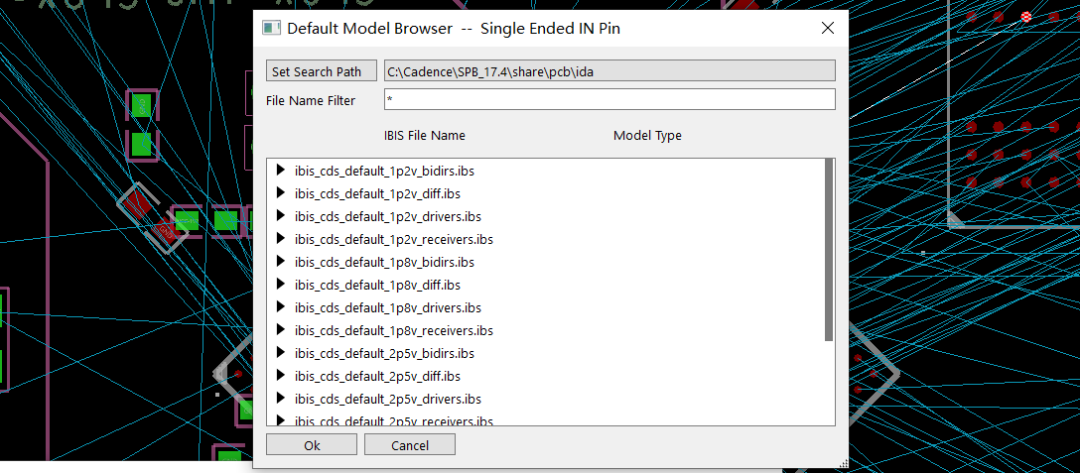

支持修改模型,點擊 Browse 瀏覽默認的模型文件,點擊 Set Search Path 可以支持設置 IBIS 的路徑,允許在修改后的 IBIS 路徑下查找新的 IBIS 文件進行模型的配置和參數設置。

5

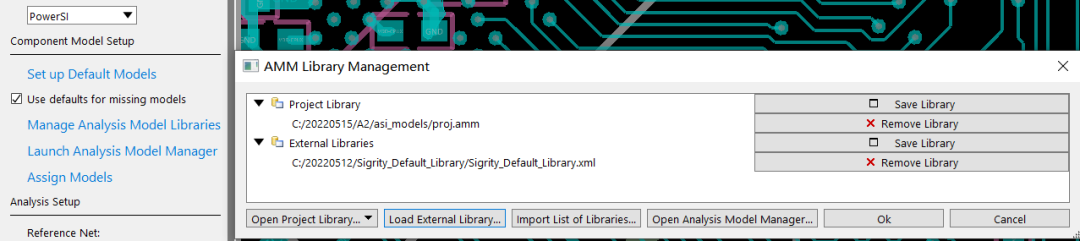

Manage Analysis Model Libraries 用來配置和管理模型庫,允許支持對本地項目庫的修改和編輯管理,也允許調用 AMM 外部系統庫。能導入 AMM 外部庫,導入庫的清單,打開和管理分析庫文件等。

6

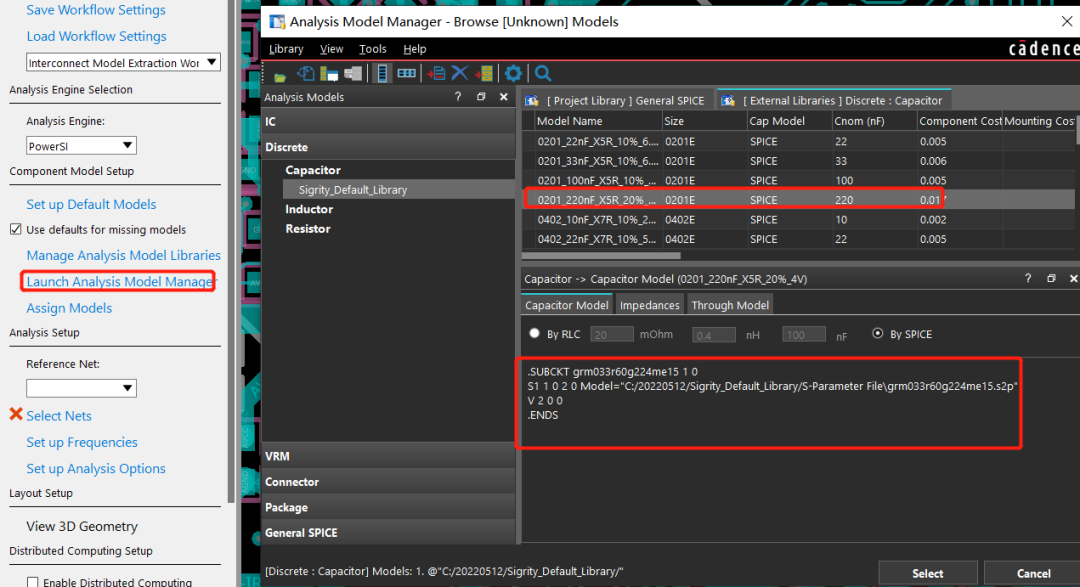

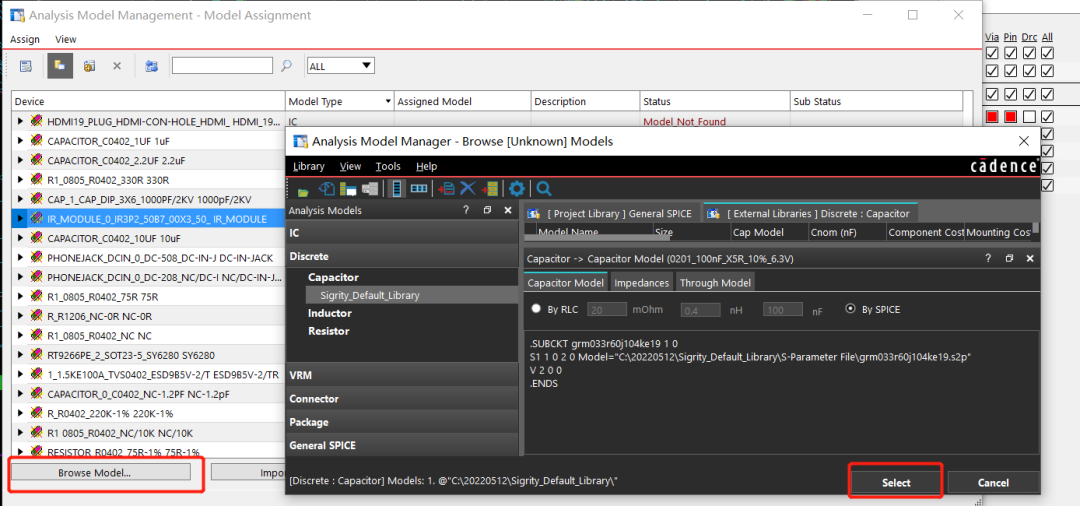

Launch Analysis Model Manager 用來啟動元件的模型管理器,在模型管理器窗口中,能夠對項目庫和外部的庫文件進行查閱、編輯、刪除、修改等操作。并且可以分析模型庫中元件的參數,包括電容、電阻、電感、VRM、連接器、封裝、SPICE 模型等。

7

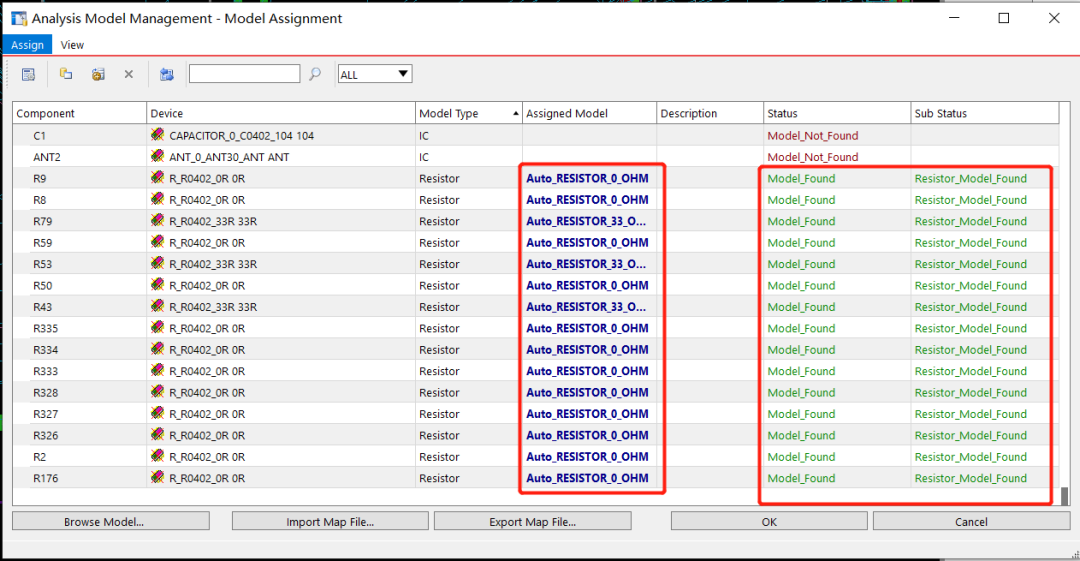

Asign Models 用來給元件添加賦予模型,在 Analysis Model Management 窗口中可以查看。允許對元件自動生成賦予模型,也支持手動對模型進行設置。允許從 AMM 文件元件的模型管理器選中模型,和調用 IBIS 模型文件進行模型的設置。

8

選中需要添加模型的元件,然后選擇 Browse Model按鈕,在元件的模型管理器中選取模型文件和對模型參數進行設置。

9

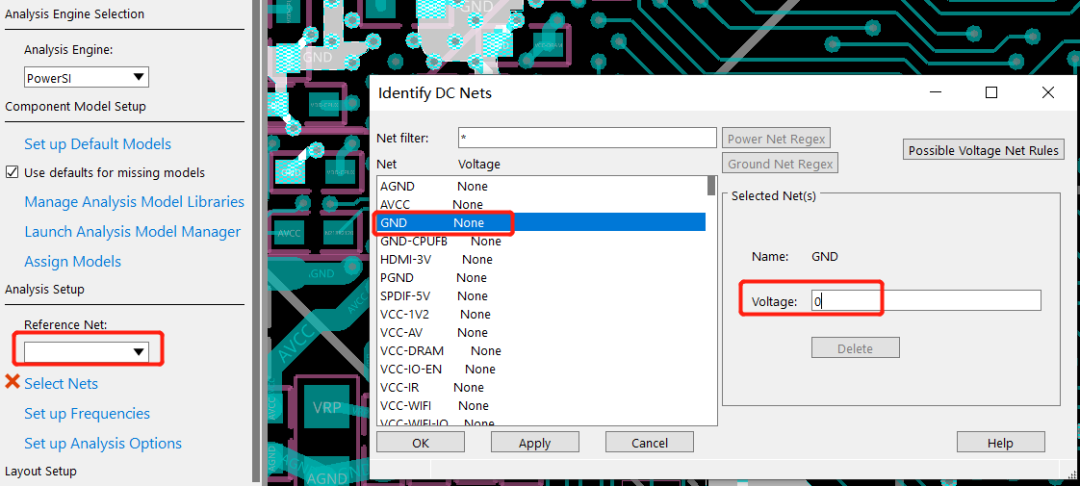

Reference Net 設置參考網絡,在例子中該處文件要設置成 GND 網絡,提取信號網絡是以 GND 網絡作為參考進行網絡設置。

10

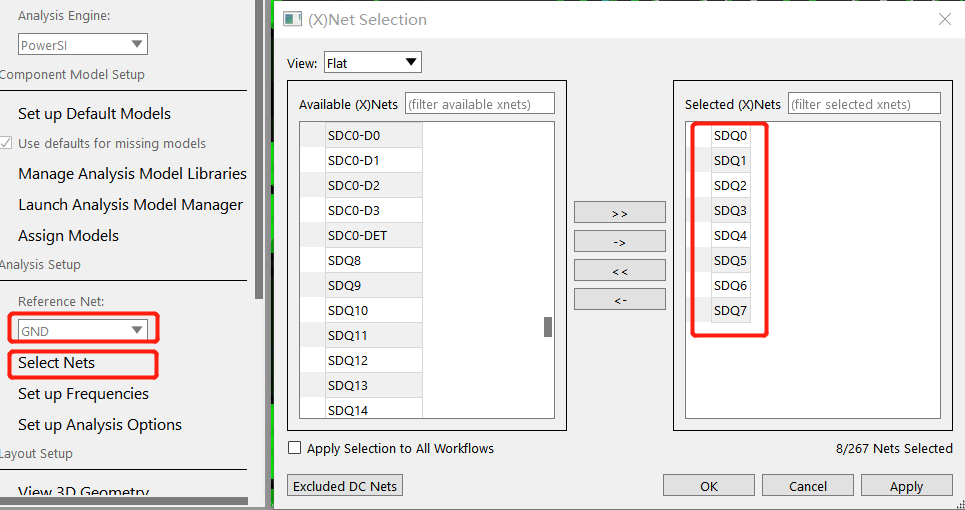

Select Nets 選取需要分析的網絡,在 Net Selection 中選擇需要分析的網絡,點擊右側圖標按鈕確認,支持單網絡和差分網絡的提取分析。若分析網絡中存在直流電源網絡或者 GND 網絡可以點擊 Excluded DC Nets 按鈕進行 DC 直流網絡的設置。

11

Set Up Frequencies 設置仿真提取的頻率參數等, Sigrity PowerSI 設置仿真頻率范圍、開始和截至頻率、掃描頻點模式、頻點數量等。

12

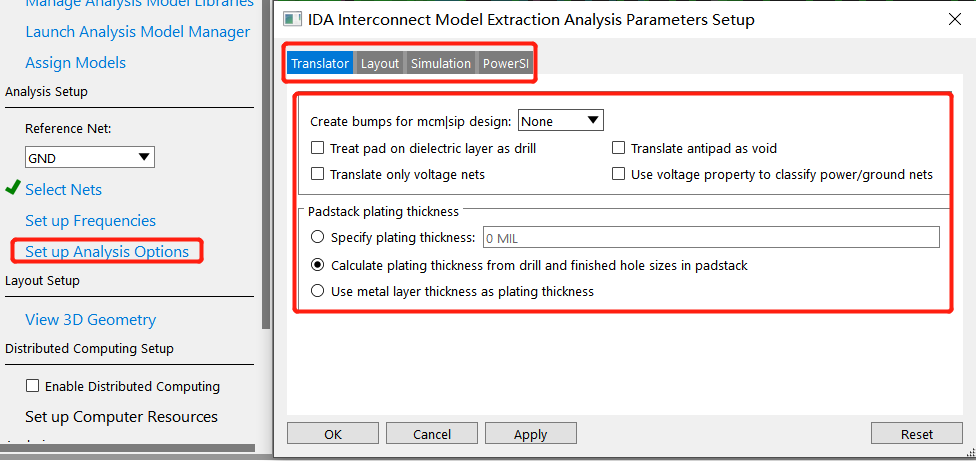

Set Up Analysis Options 是分析的可選設置項,Translator 設置文件轉換的參數,Layout 設置 PCB 的裁切區域,Simulation 設置仿真的參數,比如端口、挖空區域、電氣模型、銅皮和 NET 的選擇以及遠場結果。

13

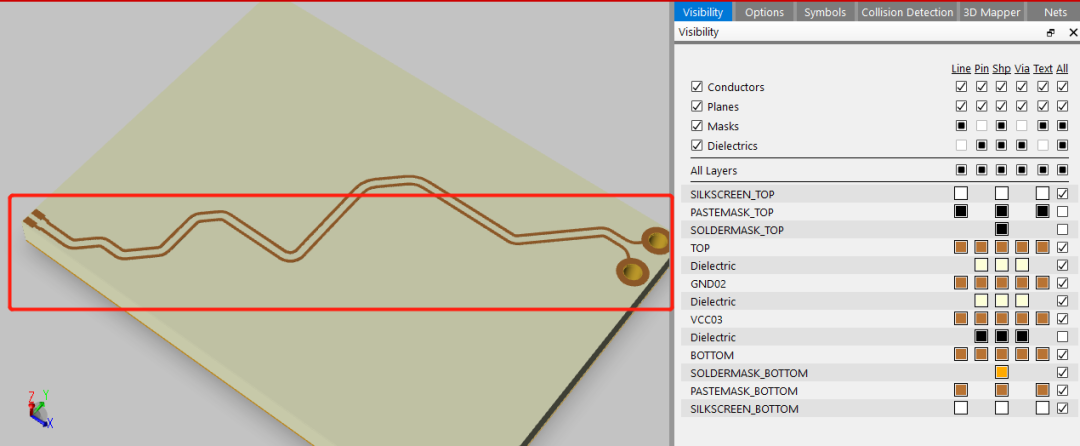

View 3D Geometry 用來預覽顯示選中分析網絡的互連通路,可以查看分析網絡的所在層及網絡通道的屬性顯示結果。

14

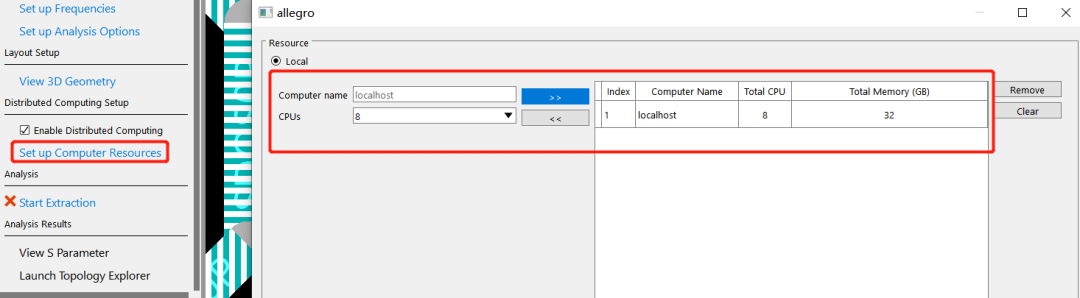

Set up Computer Resources 設置計算機資源,支持多核心的資源調用,這里可以按照計算機 CPU 的核心數量來選擇執行的資源配置。

15

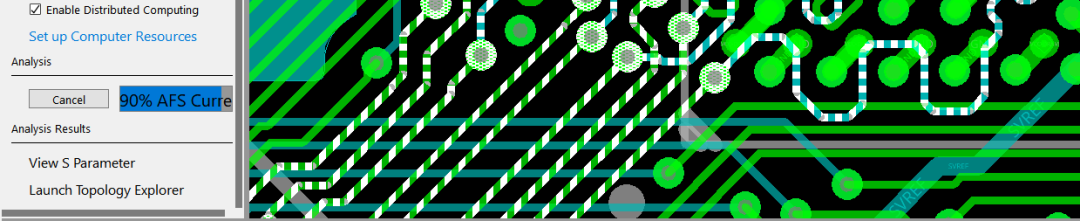

設置完成后選擇 Start Extraction 命令可以開始進行 S參數 提取。

16

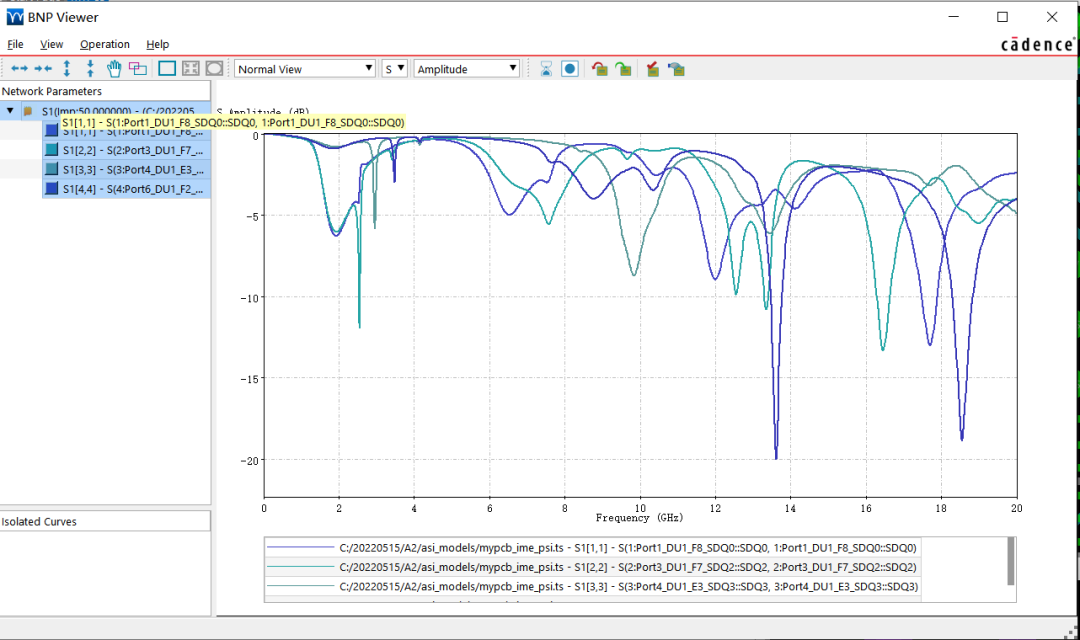

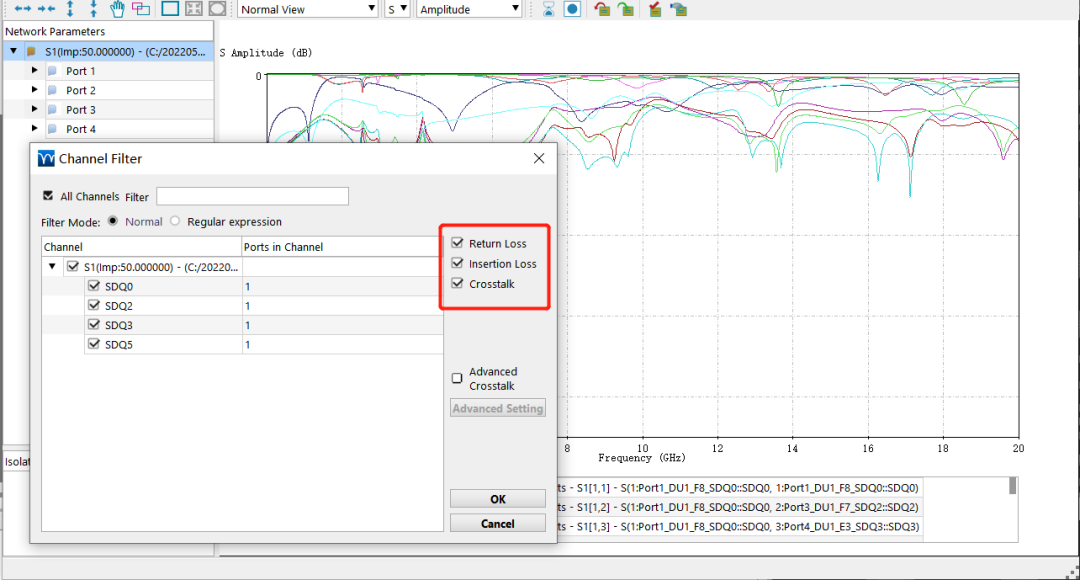

S參數 提取完成后軟件會自動打開 BNP Viewer 界面,彈出提取完成的 S參數 結果。

17

報告可以對 S參數 的結果進行分析,顯示出插損、回損、串擾的分析結果。

18

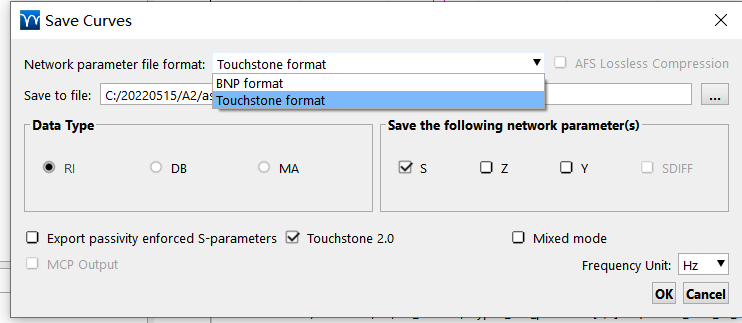

還可以支持 S參數 的結果報告,支持 BNP、Touchstone 格式文件保存。

19

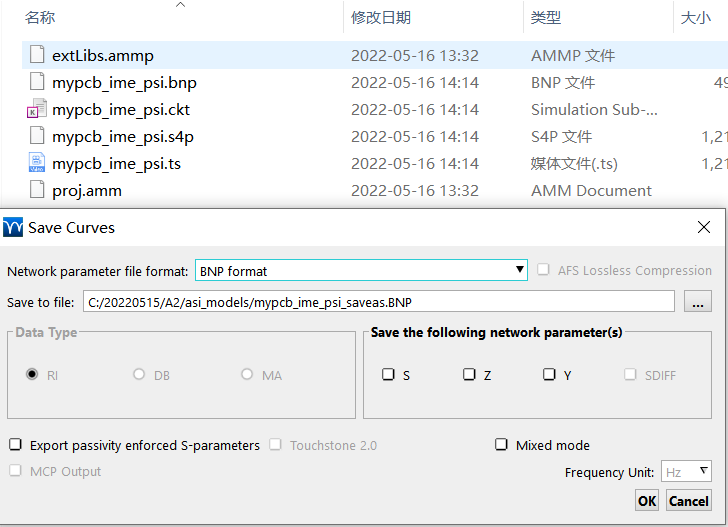

文件保存完成以后,可以看到提取到的參數文件已經保存在硬盤的文件目錄下。

20

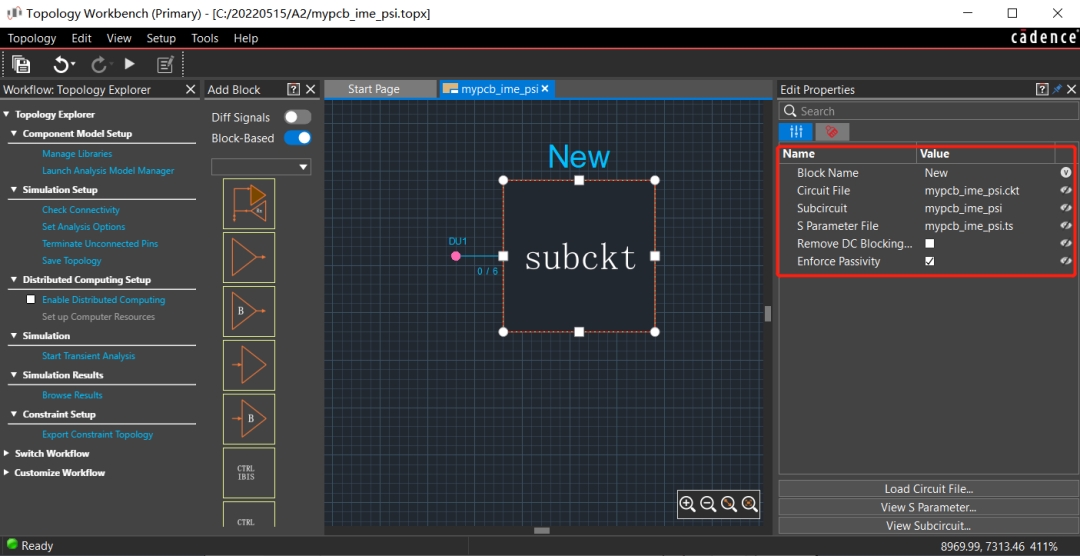

選擇 Launch Topology Explorer 按鈕,可以將已經生成的 S參數 結果文件,自動加載到 Topology Workbench 拓撲仿真界面中,并形成 BLOCK 圖標。

-

SPB

+關注

關注

0文章

27瀏覽量

13239

發布評論請先 登錄

統信Windows應用兼容引擎V3.3.0更新

作為硬件工程師,你用那款PCB 設計軟件?超全EDA工具整理!

Cadence SPB OrCAD Allegro24.1安裝包

GPU-Z迎來2.62 版本的更新發布

時隔7年的大版本更新,HDMI 2.2有哪些變化?

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

SOLIDWORKS 2025版本使用了全新的渲染引擎

Allegro X 23.11 版本更新 I PCB 設計:梯形布線的分析性能提升

【2K0300先鋒板】【v1.0.241021版本】BSP 更新,歡迎更新使用

Allegro X 23.11 版本更新 I PCB 設計:與器件關聯的動態禁布區

Allegro X 23.11 版本更新 I PCB 設計:圖紙打印和時序調整

Allegro X 23.11 版本更新 I PCB 設計:DFA_BOUND 用于 DFA 規則設定

求助,通過VScode構建的集成開發環境如何更新環境下的ESP-IDF版本?

chrome插件新版本(v3版本)中的熱更新,即加載更新遠程js的方法探索

2022 Sigrity Aurora SPB 17.4 版本更新 I 支持 Clarity 和 PowerSI 引擎直接集成

2022 Sigrity Aurora SPB 17.4 版本更新 I 支持 Clarity 和 PowerSI 引擎直接集成

評論