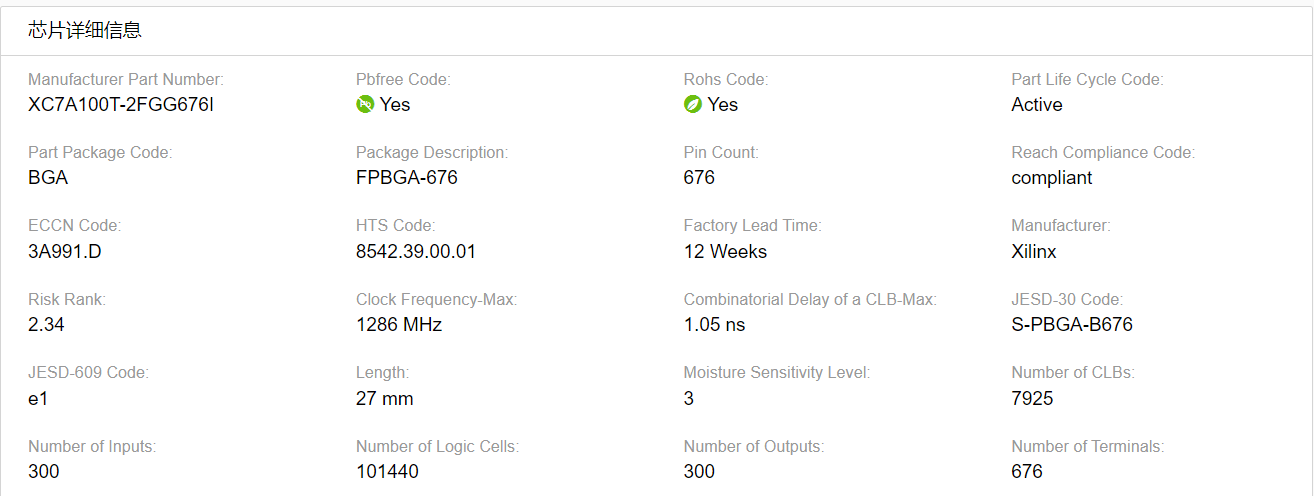

XC7A100T-2FGG676I 芯片詳細(xì)信息如圖XC7A100T-2FGG676I 供應(yīng)商XC7A100T-2FGG676I 怎么訂貨 XC7A100T-2FGG676I價(jià)格

FPGA Artix-7 系列 101440 單元 28nm 技術(shù) 1V 676-Pin FCBGA

制造商: 賽靈思

產(chǎn)品類別: 可編程邏輯、 FPGA

制造商部件號(hào): XC7A100T-2FGG676I

Xilinx? 7 系列 FPGA 包括三個(gè)全新的 FPGA 系列,可滿足從低成本、小尺寸、成本敏感、大批量應(yīng)用到超高端連接帶寬、邏輯容量和信號(hào)處理的所有系統(tǒng)要求能力最苛刻的高性能應(yīng)用程序。7 系列 FPGA 包括:

- Artix?-7 系列:針對(duì)大批量應(yīng)用的小尺寸封裝進(jìn)行了優(yōu)化,以實(shí)現(xiàn)最低的成本和功耗。

7 系列 FPGA 基于最先進(jìn)的、高性能、低功耗 (HPL)、28 nm、高 k 金屬門 (HKMG) 工藝技術(shù),以 2.9 Tb/ s 的 I/O 帶寬、200 萬個(gè)邏輯單元容量和 5.3 TMAC/s DSP,同時(shí)功耗比上一代設(shè)備低 50%,為 ASSP 和 ASIC 提供完全可編程的替代方案。

XC7A100T-2FGG676I 主要特點(diǎn)

- 基于可配置為分布式存儲(chǔ)器的真實(shí) 6 輸入查找表 (LUT) 技術(shù)的高級(jí)高性能 FPGA 邏輯。

- 具有內(nèi)置 FIFO 邏輯的 36 Kb 雙端口 Block RAM,用于片上數(shù)據(jù)緩沖。

- 高性能 SelectIO? 技術(shù),支持高達(dá) 1,866 Mb/s 的 DDR3 接口。

- 具有內(nèi)置多千兆位收發(fā)器的高速串行連接,從 600 Mb/s 到最大速率 6.6 Gb/s 到 28.05 Gb/s,提供特殊的低功耗模式,針對(duì)芯片到芯片接口進(jìn)行了優(yōu)化。

- 用戶可配置的模擬接口 (XADC),將雙 12 位 1MSPS 模數(shù)轉(zhuǎn)換器與片上熱傳感器和電源傳感器結(jié)合在一起。

- DSP Slice 帶有 25 x 18 乘法器、48 位累加器和用于高性能濾波的預(yù)加器,包括優(yōu)化的對(duì)稱系數(shù)濾波。

- 強(qiáng)大的時(shí)鐘管理塊 (CMT),結(jié)合鎖相環(huán) (PLL) 和混合模式時(shí)鐘管理器 (MMCM) 模塊,可實(shí)現(xiàn)高精度和低抖動(dòng)。

- 用于 PCI Express? (PCIe) 的集成模塊,適用于高達(dá) x8 Gen3 端點(diǎn)和根端口設(shè)計(jì)。

- 多種配置選項(xiàng),包括對(duì)商品存儲(chǔ)器的支持、具有 HMAC/SHA-256 身份驗(yàn)證的 256 位 AES 加密以及內(nèi)置 SEU 檢測(cè)和校正。

- 低成本、引線鍵合、無蓋倒裝芯片和高信號(hào)完整性倒裝芯片封裝,可在同一封裝中的家庭成員之間輕松遷移。所有可用的無鉛封裝和有鉛選項(xiàng)的選定封裝。

- 采用 28 納米、HKMG、HPL 工藝、1.0V 核心電壓工藝技術(shù)和 0.9V 核心電壓選項(xiàng),專為高性能和最低功耗而設(shè)計(jì),可實(shí)現(xiàn)更低的功耗。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21950瀏覽量

613744 -

芯片

+關(guān)注

關(guān)注

459文章

52119瀏覽量

435627 -

FPGA芯片

+關(guān)注

關(guān)注

3文章

248瀏覽量

40204

發(fā)布評(píng)論請(qǐng)先 登錄

初次使用XC7A35T-FGG484做設(shè)計(jì),用的是25MHZ有源晶振,有源晶振3.3V供電,DDR3的供電1.35V,現(xiàn)在接上晶振后,DDR3的供電變成1.8V

使用XC3S1500-4FGG456C控制ADS1248,讀不到AD數(shù)據(jù),為什么?

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】 UART測(cè)試

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】Key-test

米爾-Xilinx XC7A100T FPGA開發(fā)板試用

【米爾-紫光MYB-J7A100T國產(chǎn)FPGA開發(fā)板試用】米爾-紫光PG2L100H國產(chǎn)FPGA開發(fā)板開箱評(píng)測(cè)

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】測(cè)試一

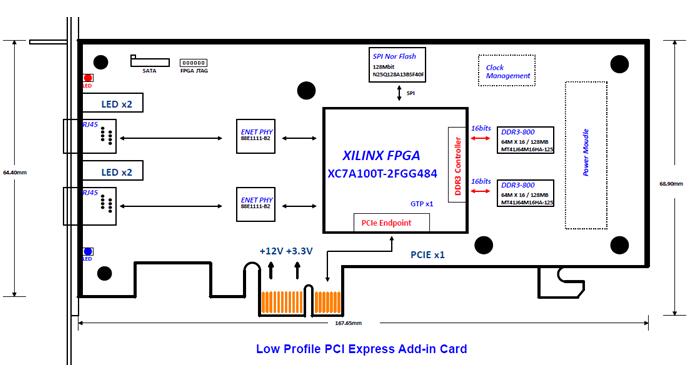

XC7A100T板卡設(shè)計(jì)原理圖:297-基于XC7A100T的PCIe千兆電口以太網(wǎng)收發(fā)卡

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】+04.SFP之Aurora測(cè)試(zmj)

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】+01.開箱(zmj)

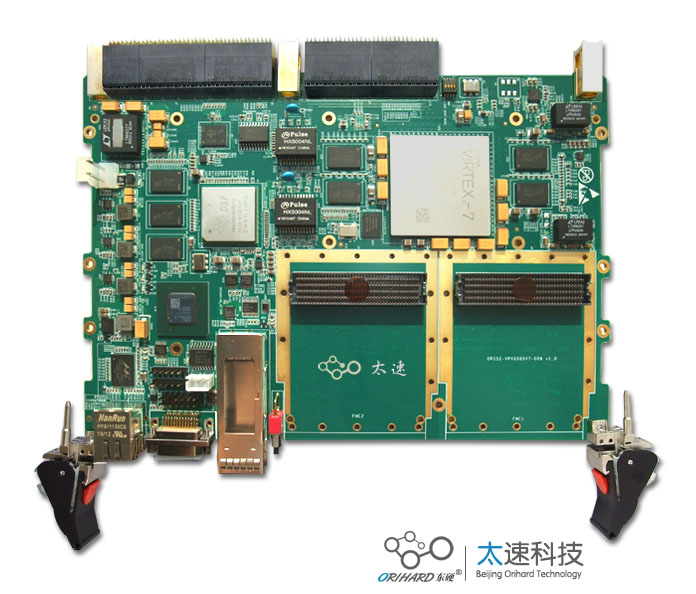

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號(hào)處理卡

XC7A100T-2FGG676I 芯片詳細(xì)信息淺談

XC7A100T-2FGG676I 芯片詳細(xì)信息淺談

評(píng)論