FIR(Finite Impulse Response)濾波器:有限長單位沖激響應濾波器,又稱為非遞歸型濾波器,是數字信號處理系統中最基本的元件,它可以在保證任意幅頻特性的同時具有嚴格的線性相頻特性,同時其單位抽樣響應是有限長的,因而濾波器是穩定的系統。因此,FIR濾波器在通信、圖像處理、模式識別等領域都有著廣泛的應用。由于 FIR 濾波器處理的是數字信號,所以模擬信號在進入 FIR 濾波器前,需要先經過 AD 器件進行模數轉換將模擬信號轉化為數字信號,而為了讓信號處理不發生失真,信號的采樣速度必須滿足奈奎斯特采樣定理,一般取信號最高頻率的 4 到 5 倍作為采樣頻率。

1 、FIR結構介紹

2 、EQ6HL130可編程邏輯芯片介紹

3 、eLinx工具介紹

4 、使用Verilog建立混頻波形

5 、matlab工具參數配置

6 、FIR結構程序設計

7 、FIR IP核使用

8 、仿真驗證

9 、開發板試用

10、公司情況

1

FIR結構介紹

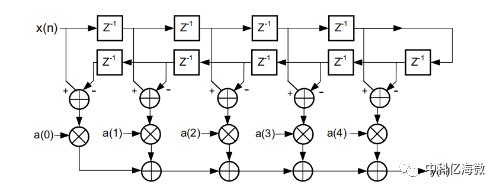

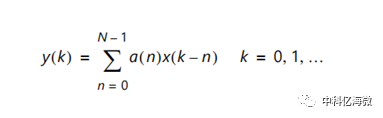

FIR 濾波器信號處理如下公式所示,其中 x(n)是輸入的信號,a(n)為 FIR 濾波系數,y(n)為濾波后的信號。N為FIR濾波器的抽頭數,濾波器階數為 N-1。

低通濾波器:低通濾波器是容許低于截止頻率的信號通過,但高于截止頻率的信號不能通過的濾波。

高通濾波器:高通濾波器,又稱低截止濾波器,低阻濾波器,允許高于某一截頻的頻率通過,而大大衰減較低頻率的一種濾波器 ,它去掉了信號中不必要的低頻成分或者說去掉了低頻干擾。

帶通濾波器:是指能通過某一頻率范圍內的頻率分量,但將其他范圍的頻率分量衰減到極低水平的濾波器,與帶阻濾波器的概念相對。

帶阻濾波器:是指能通過大多數頻率分量,但將某些范圍的頻率分量衰減到極低水平的濾波器,與帶通濾波器的概念相對。

2

EQ6HL130可編程邏輯芯片介紹

EQ6HL130是中科億海微自主研發的可編程邏輯芯片,有效系統門容量達到1360萬門;

芯核電壓1.1V,I/O標準電壓3.3V,支持多種I/O標準;

具有1200個4.5K嵌入式存儲器單元,最大存儲容量5.4M bit;

具有192個高速18bit×18bit乘法器;

具有8個可編程PLL,最高時鐘管理頻率可達500MHz;

最多可提供16路全局時鐘信號;

最大可提供338個可編程用戶I/O, 最多提供169對LVDS差分端口;

支持片上數字控制終端電阻(Digital Control Termination,DCT);

支持主動串行、被動串行、主動并行、被動并行、JTAG、SPI等配置模式;

ESD大于2000V。

3

eLinx工具介紹

億靈思設計套件(eLinx Design Suite)是中科億海微研發的一款擁有國產自主知識產權的大規模可編程邏輯芯片開發軟件,可以支持千萬門級以上可編程邏輯芯片器件的設計開發。eLinx軟件不僅可以支持工業界標準的開發流程,即從RTL綜合到配置碼流生成下載的全套操作,而且可以提供面向嵌入式可編程電路IP核定制開發的評估流程,幫助用戶定制嵌入式可編程電路IP核資源的規模和排布,并生成相應的芯片數據庫,為終端用戶提供與可編程邏輯芯片成片相同的EDA全流程服務。

產品特點:

從 RTL到Bitstream的全正向自主可控融合架構EDA工具;

集成了IP核生成器,包含豐富的IP軟硬核資源,幫助用戶快捷地實現復雜設計;

除傳統流程外,還支持嵌入式可編程電路 IP 核的評估以及定制流程;

高效的時序裝箱布局布線算法,在延時/面積方面有著高質量的QoR;

支持工業標準SDC文件作為時序約束來滿足時序要求;

集成了在線邏輯分析Bitprobe,可提供方便的在線調試手段;

支持各類碼流下載模式,包括PROM/Flash片外下載;

支持第三方的仿真工具ModelSim;

基于TCL腳本環境的自動化流程控制;

軟件界面兼容國際主流商業工具,容易上手;

直觀的圖形化管腳分配以及Floorplan功能;

三模冗余(TMR)軟件抗輻照加固措施。

4

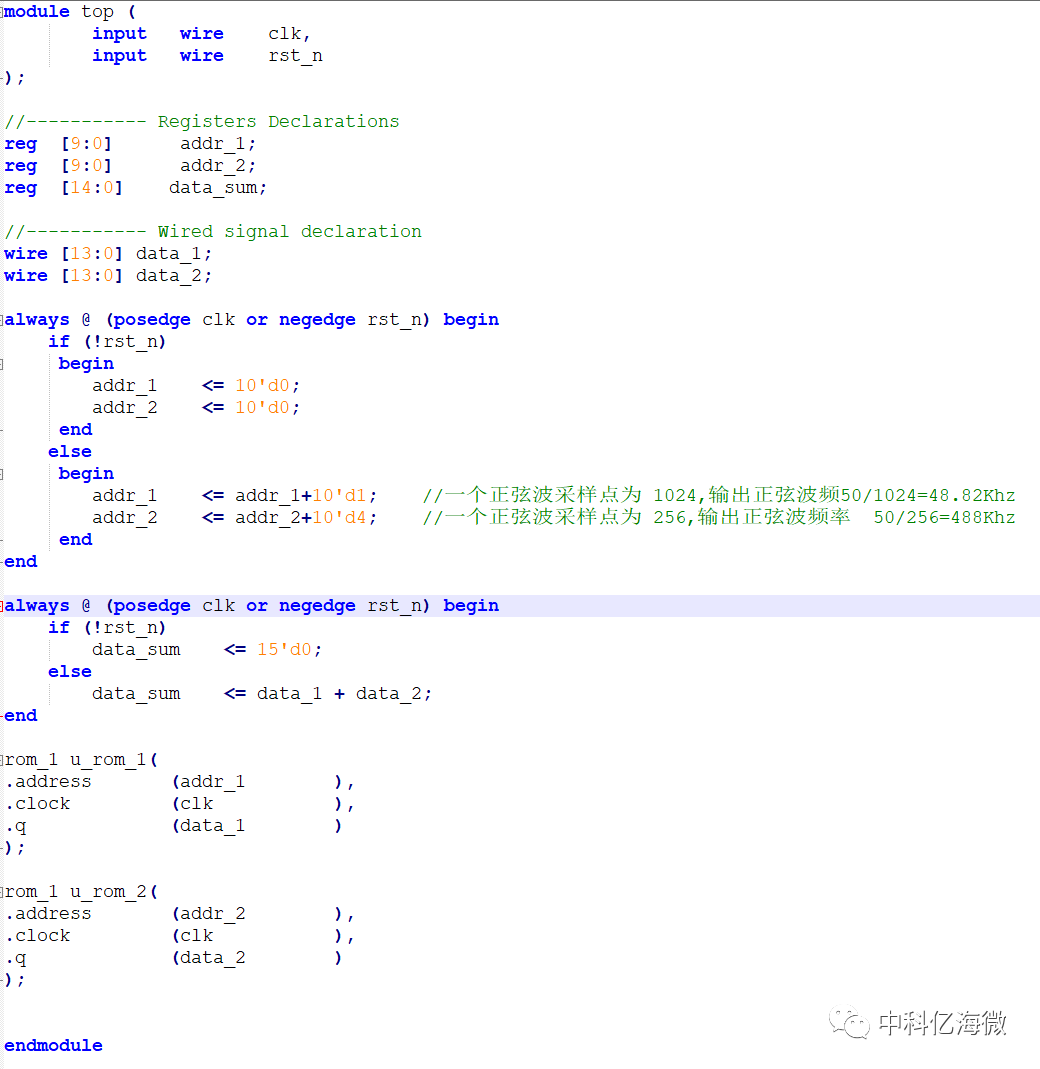

使用Verilog建立混頻波形

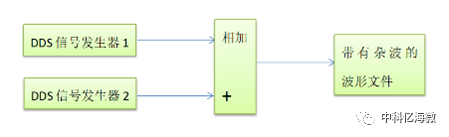

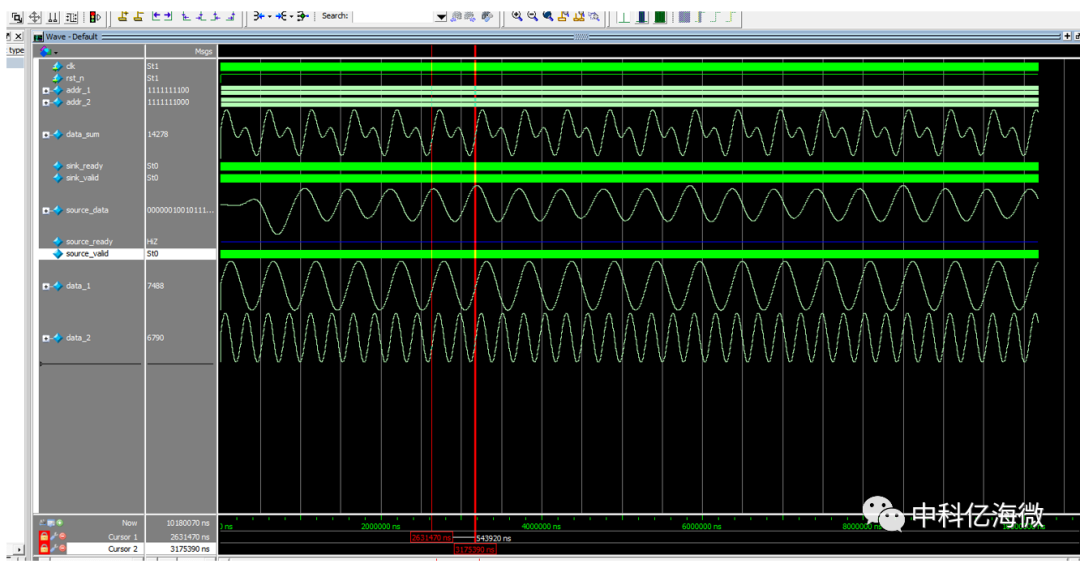

程序介紹:分別使用兩個rom輸出不同頻率,進行相加。

頻率計算:使用時鐘/采樣點=真實頻率。

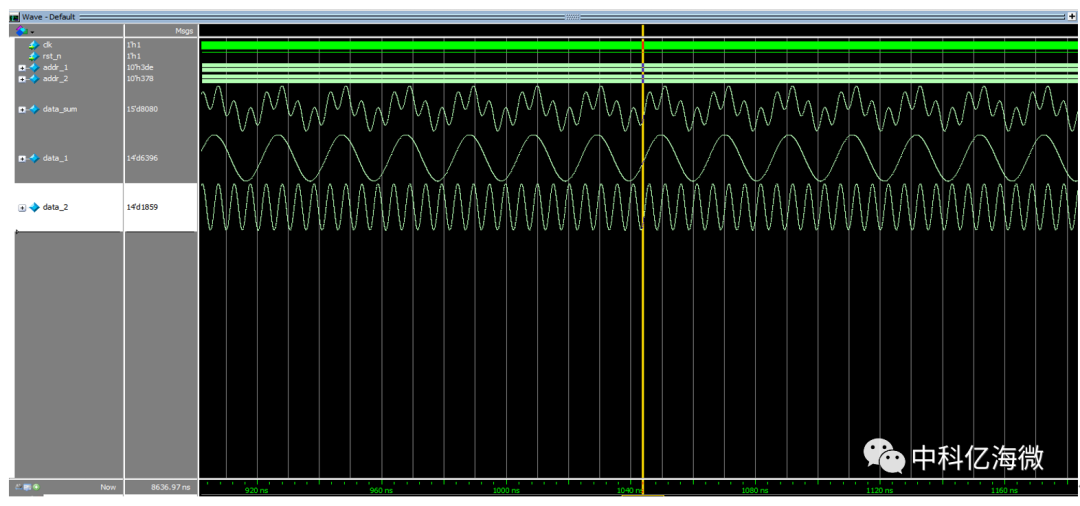

仿真結果:data_sum為相加后的結果!

5

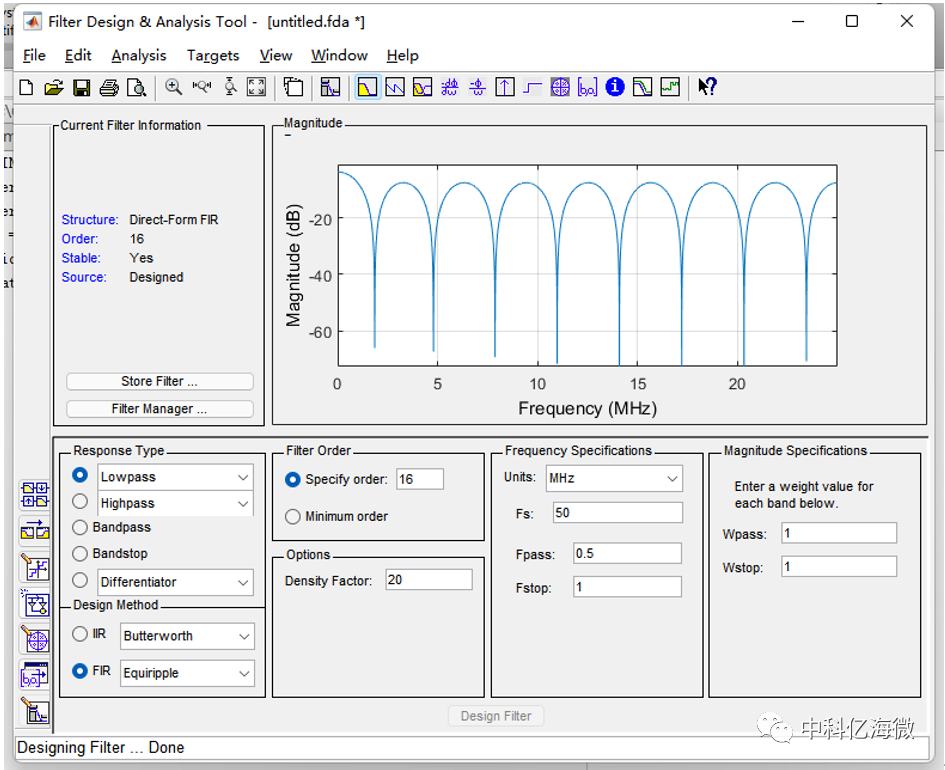

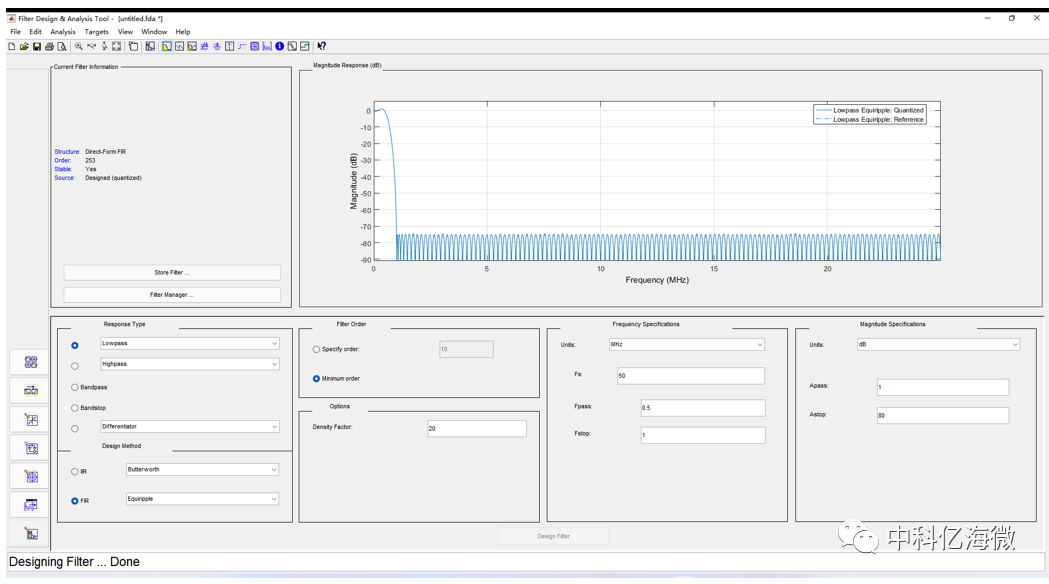

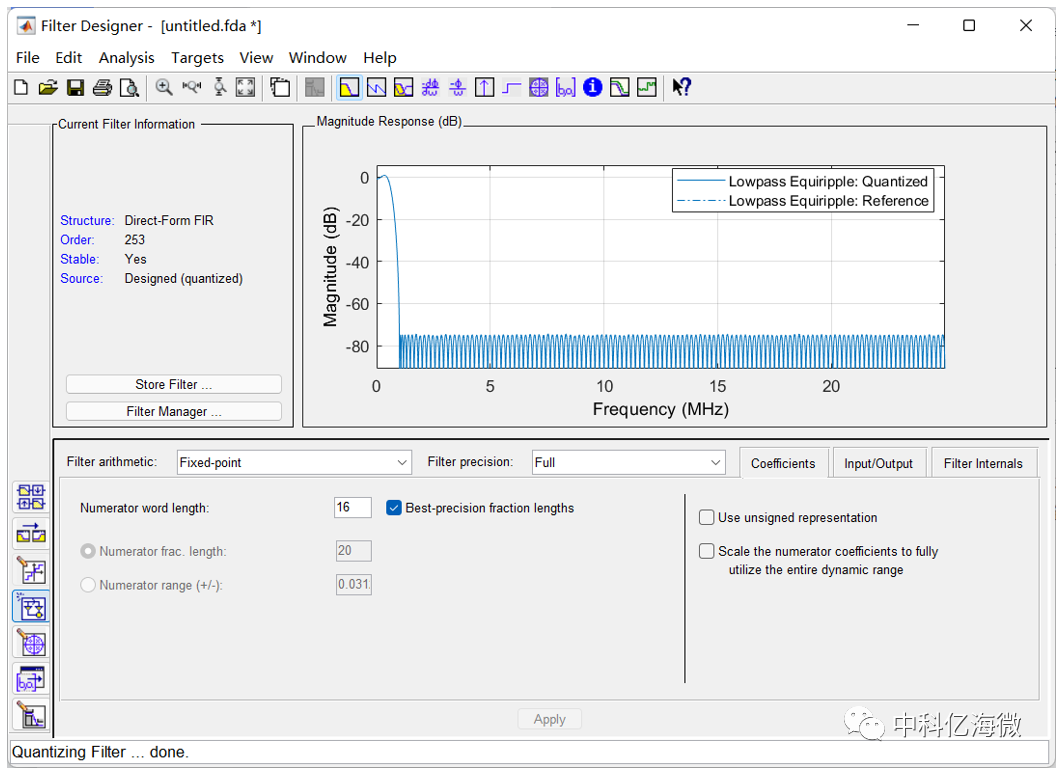

matlab工具參數配置

設計一個16階的低通濾波器

參數選擇:選用低通濾波器,使用波紋設計法,階數自定義了16個(當然階數越多濾波效果越好),FS的采樣頻率是50M,通過頻率0.5M,截至頻率為1M。

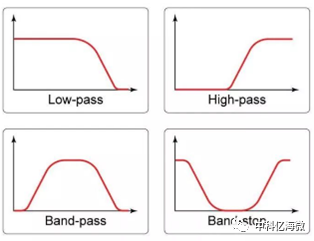

Response Type:選擇FIR濾波器的類型:低通、高通、帶通和帶阻等。

Design Method:FIR濾波器設計方法有多種,最常用的是窗函數設計法(Window)、等波紋設計法(Equiripple)和最小二乘法 (Least-Squares)等。其中窗函數設計法在學校課堂中是重點講解的,提到FIR濾波器肯定會想到hamming、kaiser窗,但是實際應用中卻很少使用,因為如果采用窗函數設計法,達到所期望的頻率響應,與其它方法相比往往階數會更多;而且窗函數設計法一般只參照通頻帶wp、抑制頻帶ws 和理想增益來設計濾波器,但是實際應用中通頻帶和抑制帶的波紋也是需要考慮的,那在這種情況下,采用等波紋設計法就非常適用了。

Frequency Specification:設置頻率響應的參數,包括采樣頻率Fs、通帶頻率Fpass和阻帶頻率Fstop。

Filter Order:設置濾波器的階數,這個選項直接影響濾波器的性能,階數越高,性能越好,但是相應在可編程邏輯芯片實現耗用的資源需要增多。在這個設置中提供2個選項:Specify order和Minimum order,Specify order是工程師自己確定濾波器的階數,Minimum order是讓工具自動確定達到期望的頻率相應所需要的最小階數,因此具體選擇哪個選項得視實際情況而定了,(這里我選用16階)。

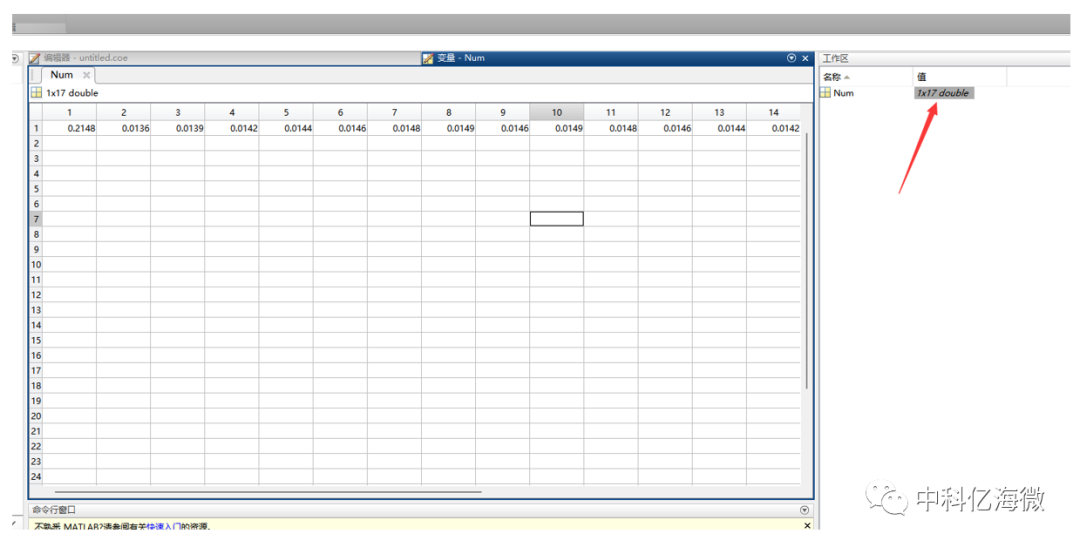

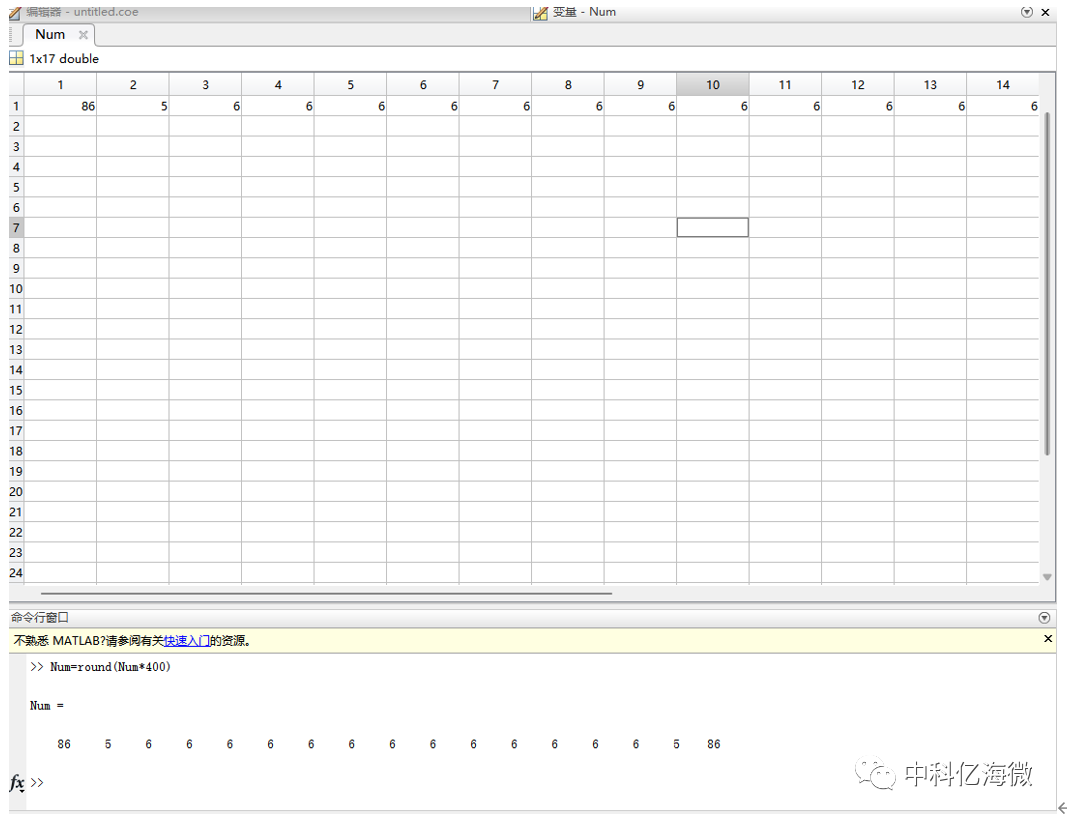

將配置完成后的數據導出 :

File ---> Export ---> Export ;

輸入:> Num=round(Num*400) 取整數

將上方數據代入到verilog進行乘累加濾波。

6

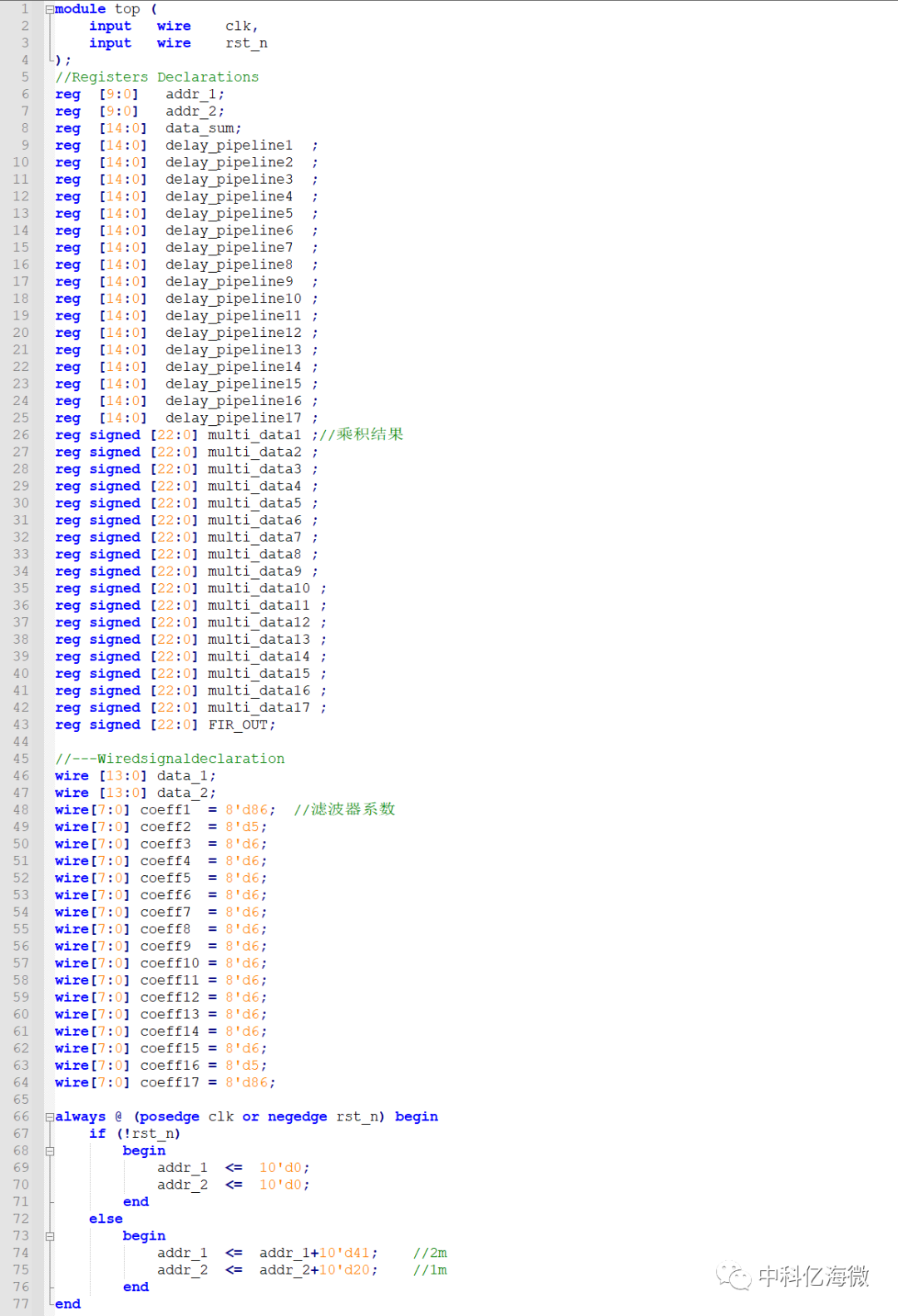

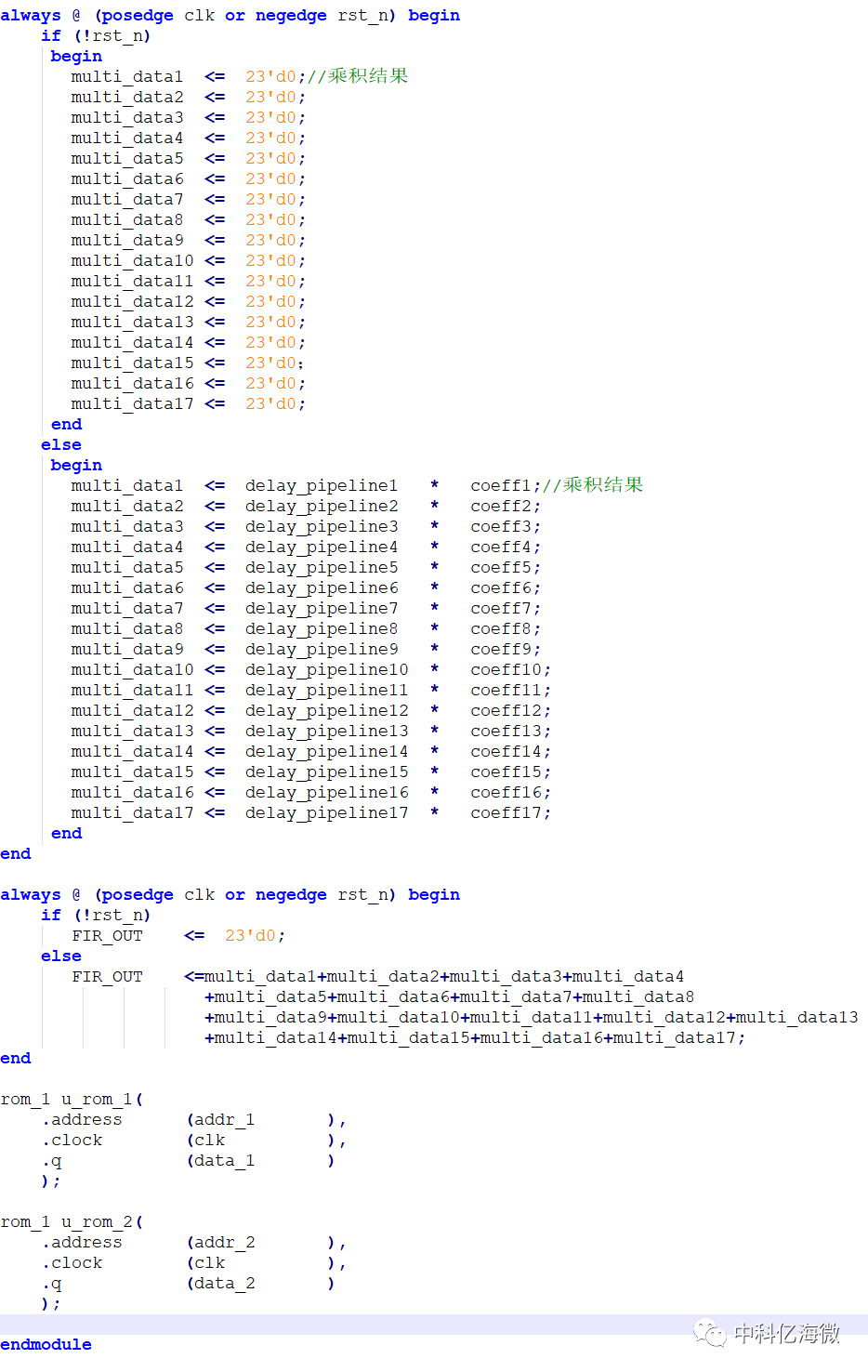

FIR結構程序設計

module top (

input wire clk,

input wire rst_n

);

//Registers Declarations

reg [9:0] addr_1;

reg [9:0] addr_2;

reg [14:0] data_sum;

reg [14:0] delay_pipeline1 ;

reg [14:0] delay_pipeline2 ;

reg [14:0] delay_pipeline3 ;

reg [14:0] delay_pipeline4 ;

reg [14:0] delay_pipeline5 ;

reg [14:0] delay_pipeline6 ;

reg [14:0] delay_pipeline7 ;

reg [14:0] delay_pipeline8 ;

reg [14:0] delay_pipeline9 ;

reg [14:0] delay_pipeline10 ;

reg [14:0] delay_pipeline11 ;

reg [14:0] delay_pipeline12 ;

reg [14:0] delay_pipeline13 ;

reg [14:0] delay_pipeline14 ;

reg [14:0] delay_pipeline15 ;

reg [14:0] delay_pipeline16 ;

reg [14:0] delay_pipeline17 ;

reg signed [22:0] multi_data1 ;//乘積結果

reg signed [22:0] multi_data2 ;

reg signed [22:0] multi_data3 ;

reg signed [22:0] multi_data4 ;

reg signed [22:0] multi_data5 ;

reg signed [22:0] multi_data6 ;

reg signed [22:0] multi_data7 ;

reg signed [22:0] multi_data8 ;

reg signed [22:0] multi_data9 ;

reg signed [22:0] multi_data10 ;

reg signed [22:0] multi_data11 ;

reg signed [22:0] multi_data12 ;

reg signed [22:0] multi_data13 ;

reg signed [22:0] multi_data14 ;

reg signed [22:0] multi_data15 ;

reg signed [22:0] multi_data16 ;

reg signed [22:0] multi_data17 ;

reg signed [22:0] FIR_OUT;

//---Wiredsignaldeclaration

wire [13:0] data_1;

wire [13:0] data_2;

wire[7:0] coeff1 =8'd86; //濾波器系數

wire[7:0] coeff2 = 8'd5;

wire[7:0] coeff3 = 8'd6;

wire[7:0] coeff4 = 8'd6;

wire[7:0] coeff5 = 8'd6;

wire[7:0] coeff6 = 8'd6;

wire[7:0] coeff7 = 8'd6;

wire[7:0] coeff8 = 8'd6;

wire[7:0] coeff9 = 8'd6;

wire[7:0] coeff10 = 8'd6;

wire[7:0] coeff11 = 8'd6;

wire[7:0] coeff12 = 8'd6;

wire[7:0] coeff13 = 8'd6;

wire[7:0] coeff14 = 8'd6;

wire[7:0] coeff15 = 8'd6;

wire[7:0] coeff16 = 8'd5;

wire[7:0] coeff17 = 8'd86;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

addr_1<=? 10'd0;

addr_2<=? 10'd0;

end

else

begin

addr_1<=? addr_1+10'd41;??? //2m

addr_2<=? addr_2+10'd20;??? //1m

end

end

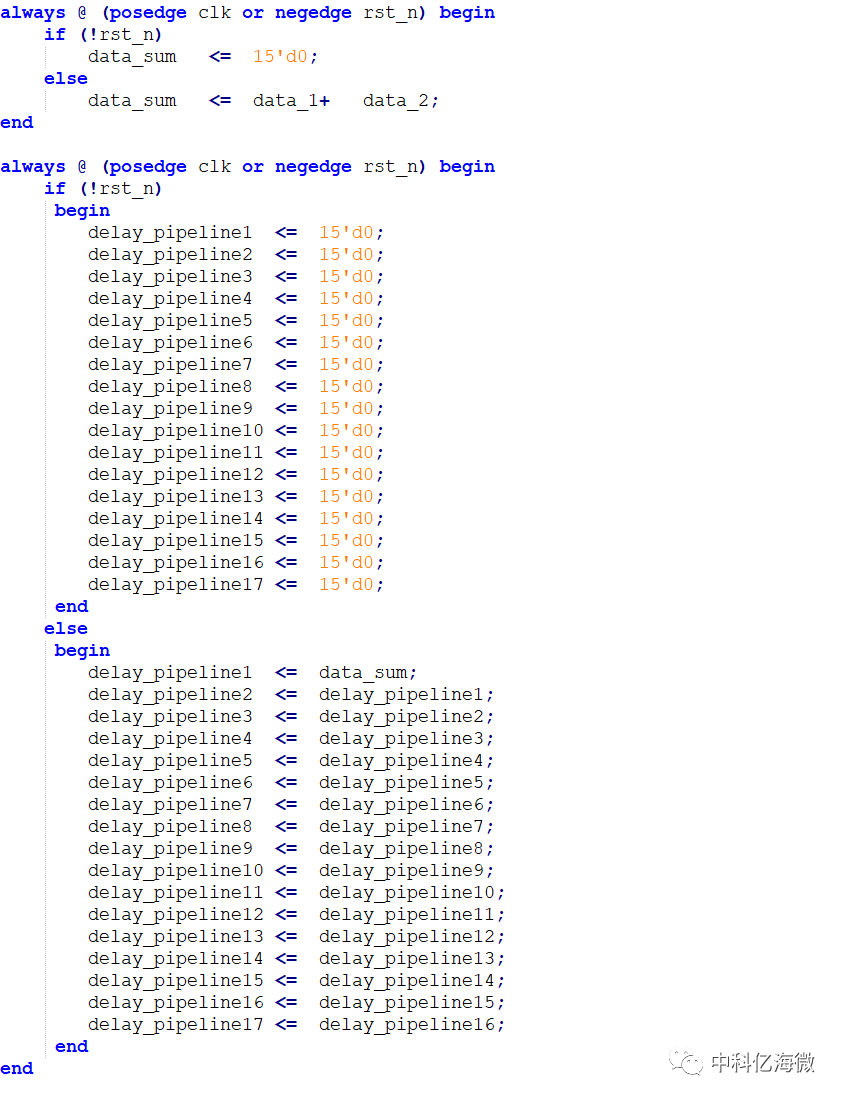

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

data_sum <=? 15'd0;

else

data_sum <=? data_1+?? data_2;

end

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

delay_pipeline1 <=? 15'd0;

delay_pipeline2 <=? 15'd0;

delay_pipeline3 <=? 15'd0;

delay_pipeline4 <=? 15'd0;

delay_pipeline5 <=? 15'd0;

delay_pipeline6 <=? 15'd0;

delay_pipeline7 <=? 15'd0;

delay_pipeline8 <=? 15'd0;

delay_pipeline9 <=? 15'd0;

delay_pipeline10 <=? 15'd0;

delay_pipeline11 <=? 15'd0;

delay_pipeline12 <=? 15'd0;

delay_pipeline13 <=? 15'd0;

delay_pipeline14 <=? 15'd0;

delay_pipeline15 <=? 15'd0;

delay_pipeline16 <=? 15'd0;

delay_pipeline17 <=? 15'd0;

end

else

begin

delay_pipeline1 <=? data_sum;

delay_pipeline2 <=? delay_pipeline1;

delay_pipeline3 <=? delay_pipeline2;

delay_pipeline4 <=? delay_pipeline3;? ??

delay_pipeline5 <=? delay_pipeline4;? ??

delay_pipeline6 <=? delay_pipeline5;? ??

delay_pipeline7 <=? delay_pipeline6;? ??

delay_pipeline8 <=? delay_pipeline7;? ??

delay_pipeline9 <=? delay_pipeline8;? ??

delay_pipeline10 <=? delay_pipeline9;? ??

delay_pipeline11 <=? delay_pipeline10;??

delay_pipeline12 <=? delay_pipeline11;??

delay_pipeline13 <=? delay_pipeline12;??

delay_pipeline14 <=? delay_pipeline13;??

delay_pipeline15 <=? delay_pipeline14;??

delay_pipeline16 <=? delay_pipeline15;??

delay_pipeline17 <=? delay_pipeline16;??

end

end

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

multi_data1 <=? 23'd0;//乘積結果

multi_data2 <=? 23'd0;

multi_data3 <=? 23'd0;

multi_data4 <=? 23'd0;

multi_data5 <=? 23'd0;

multi_data6 <=? 23'd0;

multi_data7 <=? 23'd0;

multi_data8 <=? 23'd0;

multi_data9 <=? 23'd0;

multi_data10 <=? 23'd0;

multi_data11 <=? 23'd0;

multi_data12 <=? 23'd0;

multi_data13 <=? 23'd0;

multi_data14 <=? 23'd0;

multi_data15 <=? 23'd0;

multi_data16 <=? 23'd0;

multi_data17 <=? 23'd0;

end

else

begin

multi_data1 <=? delay_pipeline1?? *?? coeff1;//乘積結果

multi_data2 <=? delay_pipeline2?? *?? coeff2;

multi_data3 <=? delay_pipeline3?? *?? coeff3;

multi_data4 <=? delay_pipeline4?? *?? coeff4;

multi_data5 <=? delay_pipeline5?? *?? coeff5;

multi_data6 <=? delay_pipeline6?? *?? coeff6;

multi_data7 <=? delay_pipeline7?? *?? coeff7;

multi_data8 <=? delay_pipeline8?? *?? coeff8;

multi_data9 <=? delay_pipeline9?? *?? coeff9;

multi_data10 <=? delay_pipeline10? *?? coeff10;

multi_data11 <=? delay_pipeline11? *?? coeff11;

multi_data12 <=? delay_pipeline12? *?? coeff12;

multi_data13 <=? delay_pipeline13? *?? coeff13;

multi_data14 <=? delay_pipeline14? *?? coeff14;

multi_data15 <=? delay_pipeline15? *?? coeff15;

multi_data16 <=? delay_pipeline16? *?? coeff16;

multi_data17 <=? delay_pipeline17? *?? coeff17;

end

end

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

FIR_OUT <=? 23'd0;

else

FIR_OUT <=multi_data1+multi_data2+multi_data3+multi_data4+multi_data5+multi_data6+multi_data7

+multi_data8+multi_data9+multi_data10+multi_data11+multi_data12+multi_data13+multi_data14+multi_data15

+multi_data16+multi_data17;

end

rom_1 u_rom_1(

.address (addr_1 ),

.clock (clk ),

.q (data_1 )

);

rom_1 u_rom_2(

.address (addr_2 ),

.clock (clk ),

.q (data_2 )

);

endmodule

仿真結果:FIR_OUT 為濾波后的效果。

7

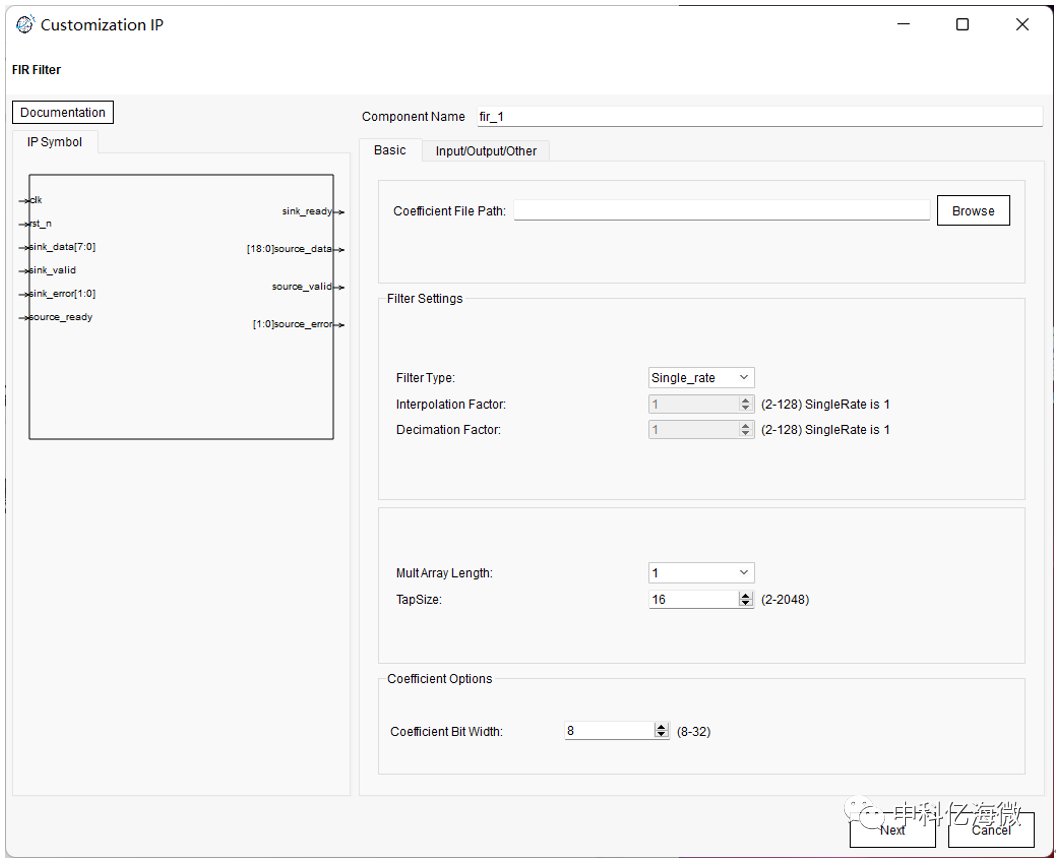

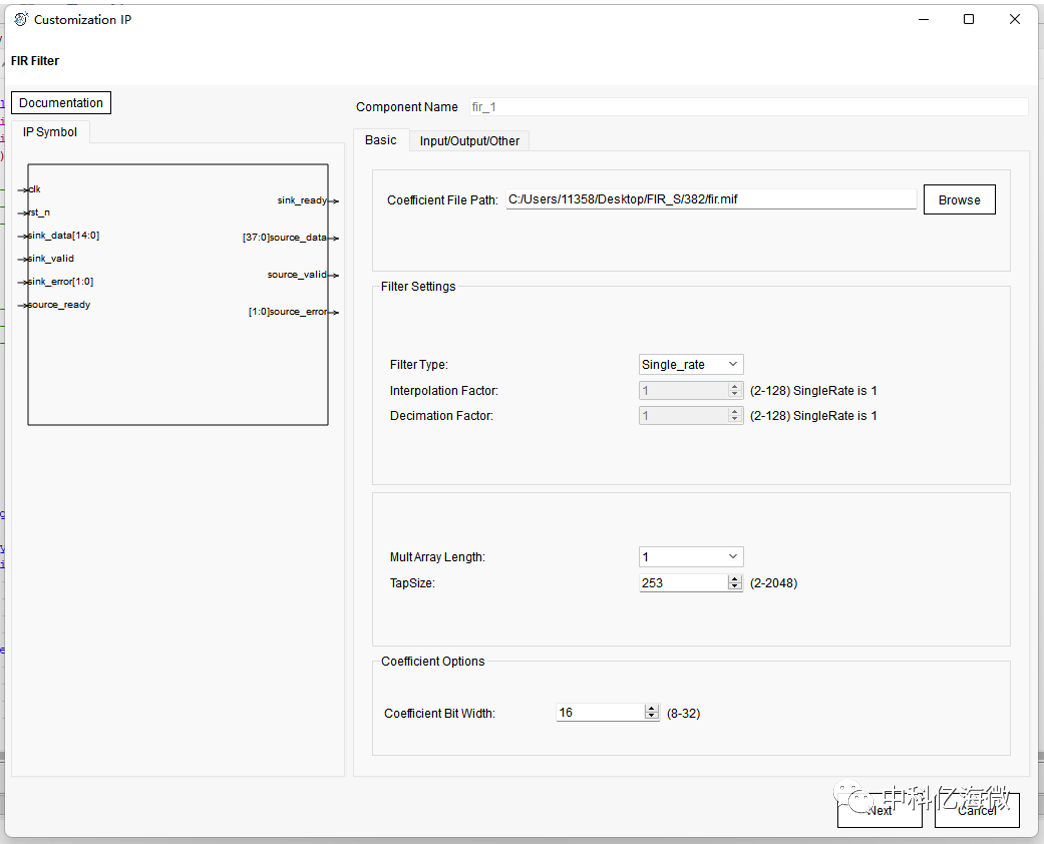

FIR IP核使用

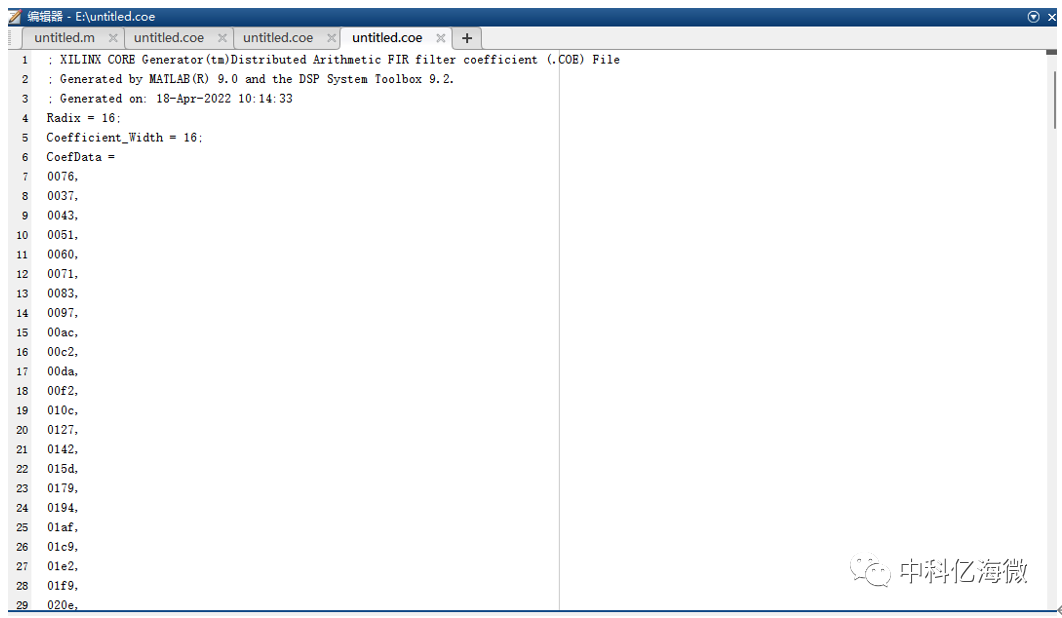

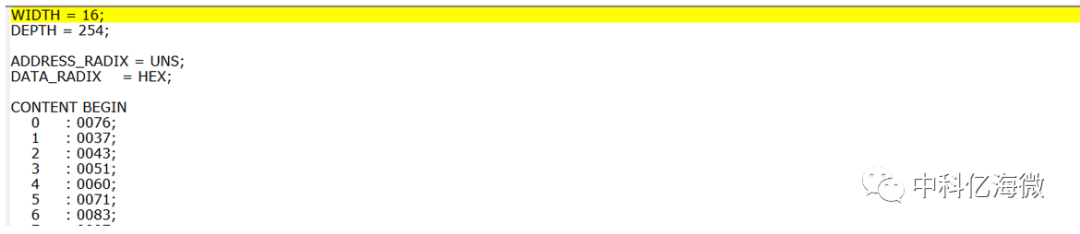

采用IP核的形式完成濾波實驗,需要使用MATLAB配置參數,以MIF格式的文件放置到IP中進行配置。

Docunmentation : FIR的IP核使用手冊。

Coefficient File Path : 防止配置后的MIF文件。

因為可編程邏輯芯片并不支持浮點數的運算,所以需要對抽頭系數進行量化處理,在 Filter arithmetic 中選擇 Fixed-point, Number word length 中可以輸入的是字長,當輸入 8 時,點擊 Apply,可以看到有較大的偏差。所以將數值改為 16。

導出需要配置的數據 :

將數據文件改成.MIF文件格式,給予eLinx軟件使用。

此處存儲為十六進制數據 , 我們建議使用二進制進行存儲,數據更加穩定。

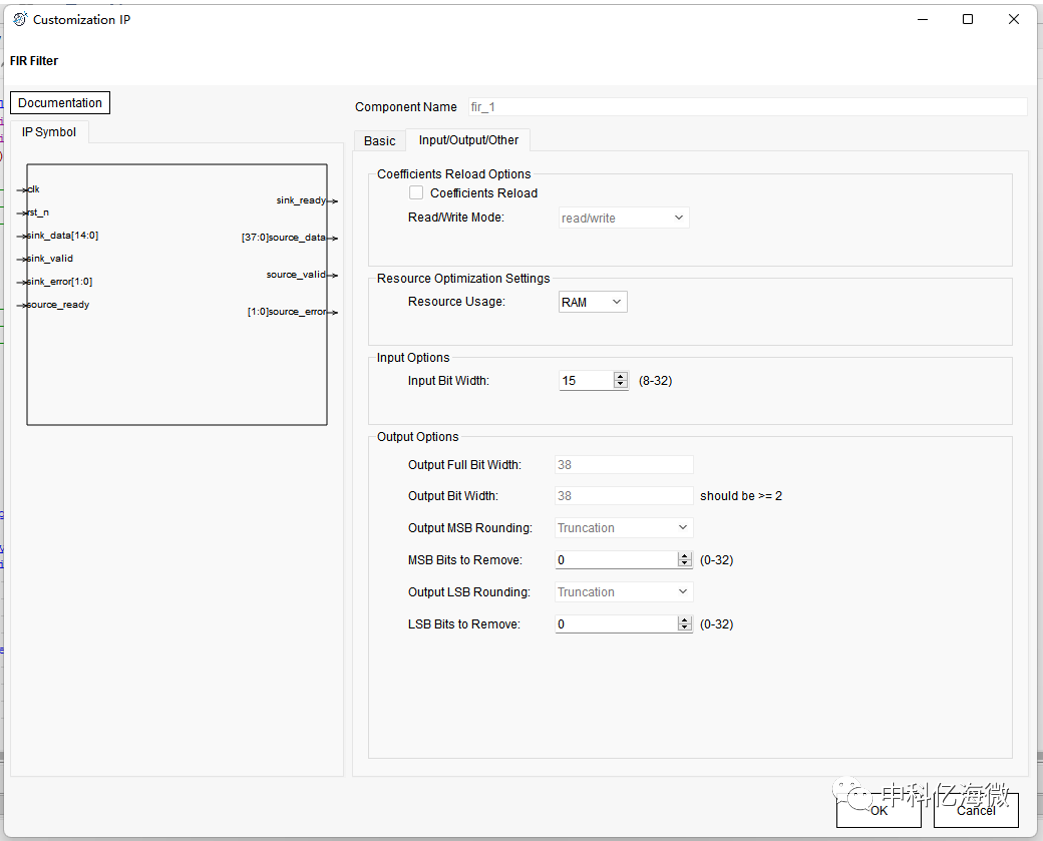

IP核配置頁面 :

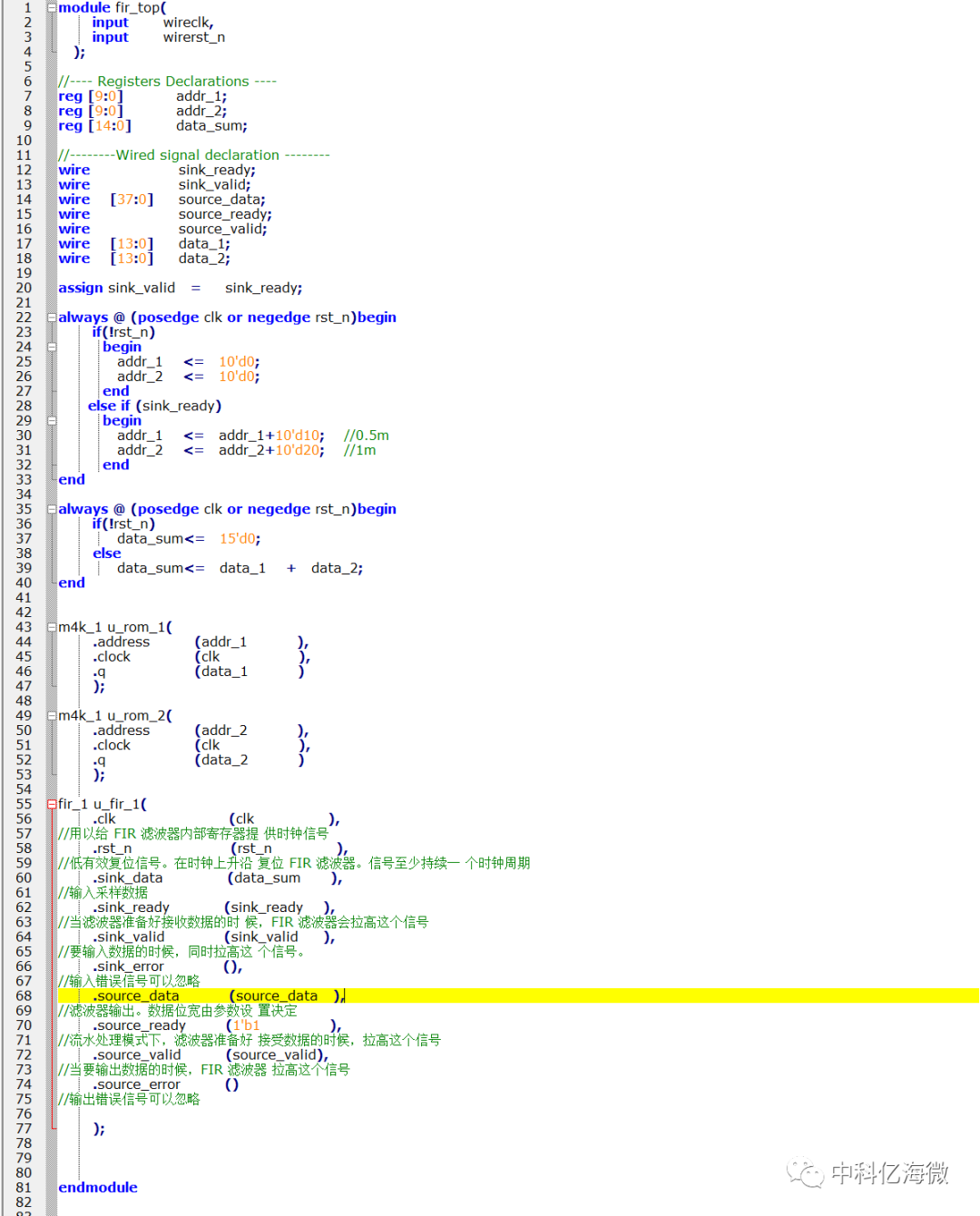

測試程序:

8

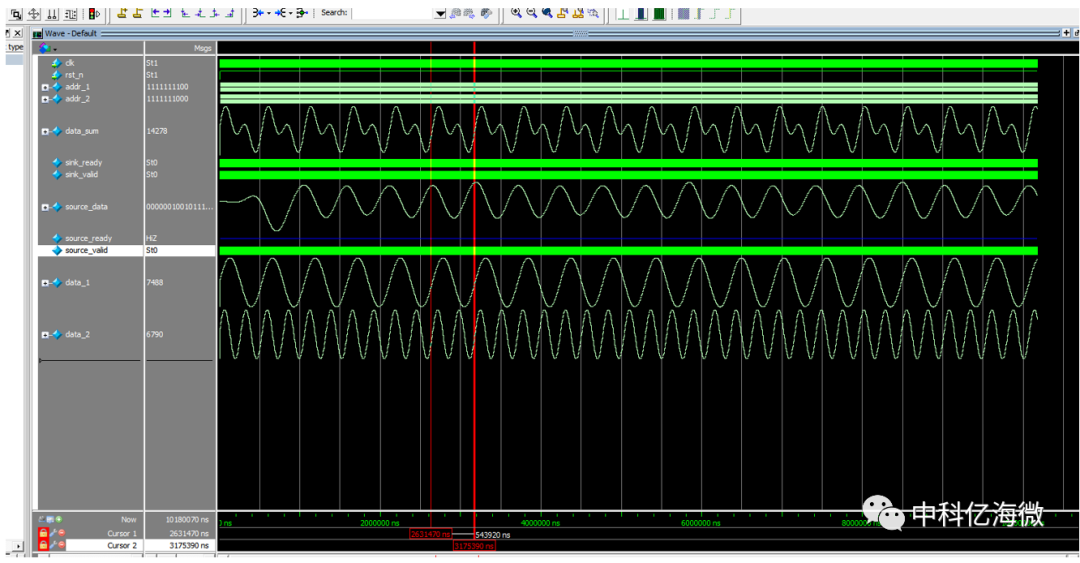

仿真驗證

-

濾波器

+關注

關注

162文章

8066瀏覽量

180993 -

FIR

+關注

關注

4文章

151瀏覽量

34017

發布評論請先 登錄

如何通過高效工程評審EQ流程,實現PCB零缺陷制造?

Vivado FIR IP核實現

6020 Ultimate EQ說明

基于FPGA實現FIR數字濾波器

基于EQ6HL130實現FIR功能測試

基于EQ6HL130實現FIR功能測試

評論