Allegro Package Designer Plus工具在最新的 SPB 17.4版本中迎來了布線技術(shù)中的新變化——廣為人知的“過孔結(jié)構(gòu)”這一概念因為其靈活性不斷提高且適用于許多不同設(shè)計流程,現(xiàn)已改名為“結(jié)構(gòu)”,方便、可重復(fù)使用的布線模塊,可以使工程師快速地扇出最復(fù)雜的組件接口。而且在扇出之后,可以將結(jié)構(gòu)保存到模塊庫中,為后續(xù)類似的設(shè)計節(jié)省更多時間。原本花在開發(fā)結(jié)構(gòu)和建立扇出布線上的時間可以因此節(jié)省下來,用于完成其他不同的設(shè)計任務(wù)。

舊瓶裝新酒——界面熟悉

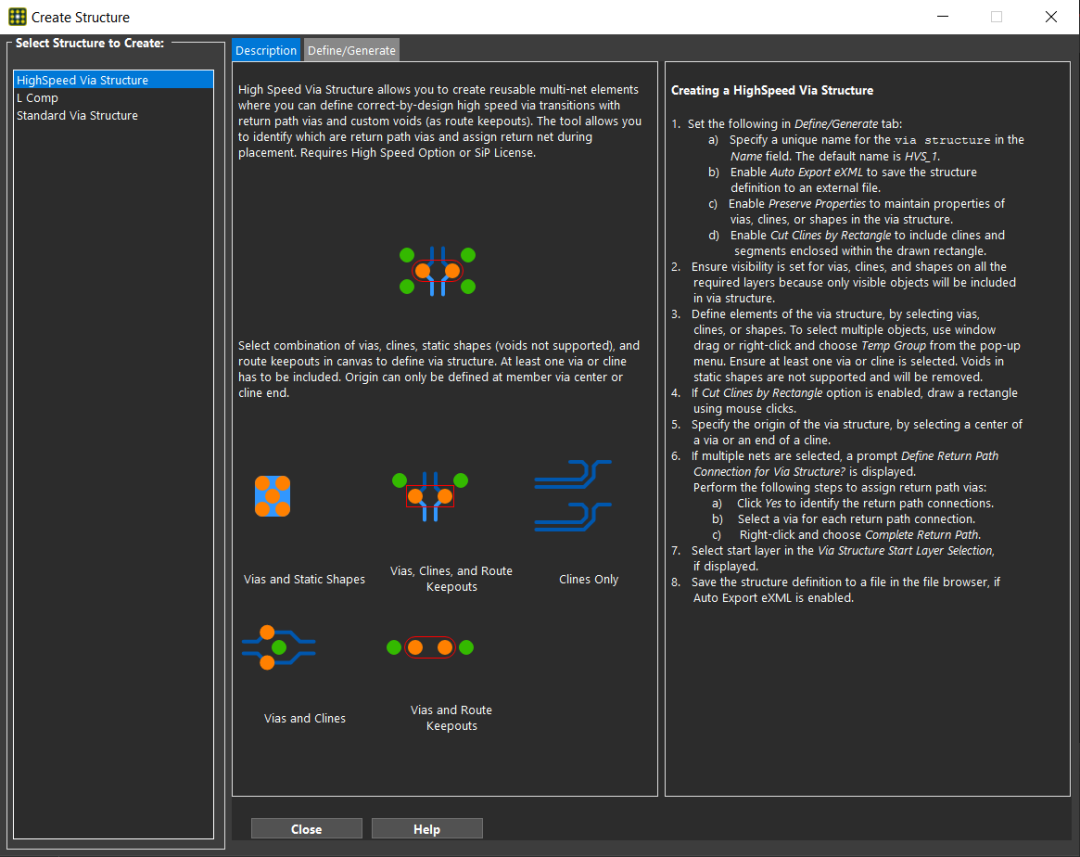

在最新的 SPB 17.4版本中,無論是使用 SiP Layout Option創(chuàng)建高速和 L Comp 結(jié)構(gòu),還是基本工具套件中的標(biāo)準結(jié)構(gòu),創(chuàng)建結(jié)構(gòu)的用戶界面都如下面顯示:

對于高速和標(biāo)準結(jié)構(gòu),首先從有關(guān)的組件上引出一個單一引腳。然后進入該命令,選擇該布線(和任何周圍的參考元素,如回流路徑過孔),形成一個新的結(jié)構(gòu)定義。

當(dāng)完成此操作后,來到放置結(jié)構(gòu)命令,就可以在幾秒鐘內(nèi)放置結(jié)構(gòu),為許多針腳進行逃逸布線。或者,如果已經(jīng)開始使用簡單的過孔逃逸模式,則可以選擇“用結(jié)構(gòu)替換過孔”命令,將占位過孔換成最終的結(jié)構(gòu)扇出。

扇出結(jié)構(gòu)的復(fù)雜性每年都會增加,以上是非常便捷有效的工具,但是都需要提前預(yù)判一些工作型態(tài)。如果我們想要一個特定目標(biāo)和特定設(shè)計的結(jié)構(gòu),該怎么做?設(shè)計工具中是否有任何功能,可以更快地實現(xiàn)這一需求?

創(chuàng)建結(jié)構(gòu)的新方法

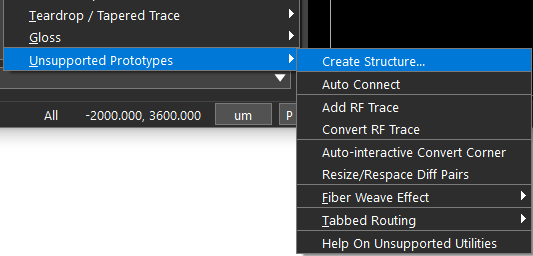

激活 SiP Layout Option時,在 Route - Unsupported Prototypes 菜單下會看到 “Create Structure...”命令。

啟動后,這個新工具可提供為多種用途創(chuàng)建結(jié)構(gòu)的選項,包括蛇形、梳狀、單端結(jié)構(gòu)或帶有返回路徑過孔的差對結(jié)構(gòu)。

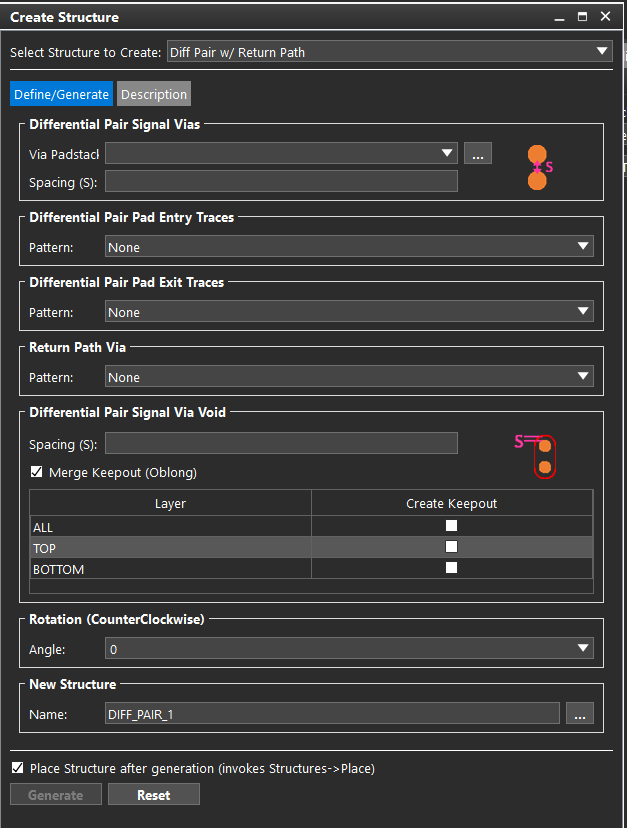

為了提升工作效率,可以把這個表格連接到選項和可見性標(biāo)簽,或者可以在使用雙顯示器時把它移到另一個屏幕上。

與標(biāo)準結(jié)構(gòu)定義流程的明顯區(qū)別是,不再需要預(yù)先進行布線,便可以例子來推導(dǎo)定義。

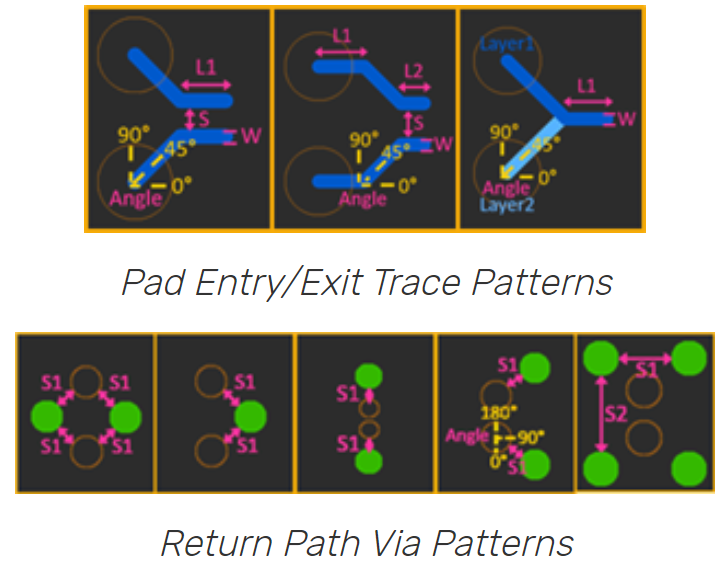

選擇過孔焊盤、焊盤入口/出口模式、返回路徑過孔布局,以及需要凈空來實現(xiàn)過孔上方和下方信號完整屏蔽的層。繼續(xù)完善定義時,圖片將顯示參數(shù)之間的確切關(guān)系,這將非常有幫助。多種樣式可供選擇:

當(dāng)完成結(jié)構(gòu)的參數(shù)化和命名后,只需按一下按鈕就可以提交更改,并直接將其應(yīng)用于設(shè)計!

-

IC

+關(guān)注

關(guān)注

36文章

6099瀏覽量

178481 -

封裝

+關(guān)注

關(guān)注

128文章

8545瀏覽量

144850

發(fā)布評論請先 登錄

IC封裝產(chǎn)線分類詳解:金屬封裝、陶瓷封裝與先進封裝

先進封裝中RDL工藝介紹

石墨烯制備的新方法

大華股份榮獲中國創(chuàng)新方法大賽一等獎

基于遺傳算法的QD-SOA設(shè)計新方法

芯片封裝IC載板

一種降低VIO/VSLAM系統(tǒng)漂移的新方法

大華股份榮獲2024年中國創(chuàng)新方法大賽一等獎

長安汽車榮獲2024年中國創(chuàng)新方法大賽一等獎

利用全息技術(shù)在硅晶圓內(nèi)部制造納米結(jié)構(gòu)的新方法

上海光機所提出強激光產(chǎn)生高能量子渦旋態(tài)電子新方法

保護4-20 mA,±20-mA模擬輸入的新方法

一種無透鏡成像的新方法

從“蓋房子”到“頂竹筍”:我國科學(xué)家首創(chuàng)晶體制備新方法

技術(shù)資訊I IC封裝中快速創(chuàng)建結(jié)構(gòu)的新方法

技術(shù)資訊I IC封裝中快速創(chuàng)建結(jié)構(gòu)的新方法

評論