1、什么是邊沿檢測

邊沿檢測用于檢測信號的上升沿或下降沿,通常用于使能信號的捕捉等場景。

2、采用1級觸發器的邊沿檢測電路設計(以下降沿為例)

2.1、設計方法

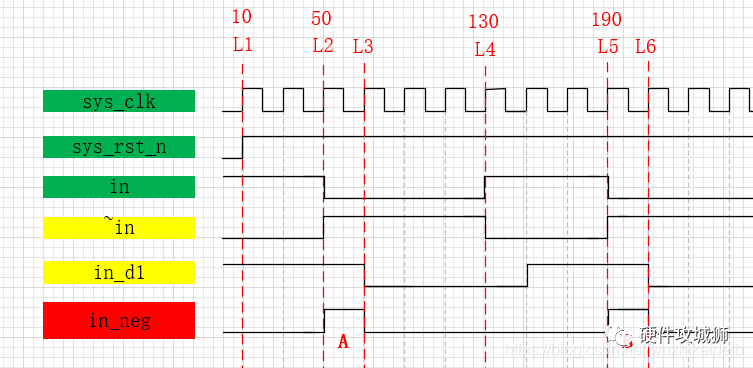

設計波形圖如下所示:

各信號說明如下:

sys_clk:基準時鐘信號(這里設定為50MHz,周期20ns)

sys_rst_n:低電平有效的復位信號

in:輸入信號,需要對其進行下降沿檢測

~in:輸入信號的反相信號

in_d1:對輸入信號寄存一拍

in_neg:得到的下降沿指示信號,該信號為 ind1 && ~in

對上圖進行分析:

信號in是我們需要對其進行下降沿檢測的信號

信號~in是將信號in反向

信號in_d1是使用寄存器寄存in信號,即對其進行打拍,或者說是同步到系統時鐘域下

輸入信號開始為高電平,在L2處變為低電平,產生第1個下降沿,在L5出產生第2個下降沿

A處為產生的第1個下降沿指示信號,B處為產生的第2個下降沿指示信號

由此我們可以推導出邊沿檢測信號產生的一般方法:

將需要檢測的信號寄存一拍,同步到系統時鐘域下,得到信號 in_d1

將需要檢測的信號反向,得到信號 ~in

將信號 in_d1 反向,得到信號 ~in_d1

通過組合邏輯電路可以得到下降沿信號 in_neg:assign in_neg = ~in && in_d1

同樣通過組合邏輯電路可以得到上升沿信號 in_pos:assign in_pos = in && ~in_d1

雙邊沿檢測就是將上兩條加(或運算)起來就可以了,化簡后有:雙邊沿信號 in_both = in ^ ind1

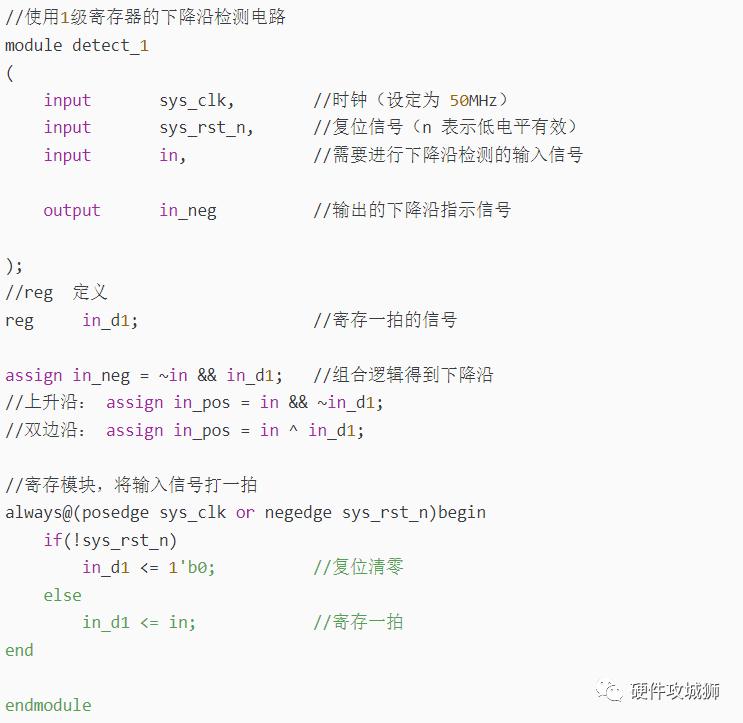

2.2、Verilog實現

根據上文分析不難編寫Verilog代碼如下:

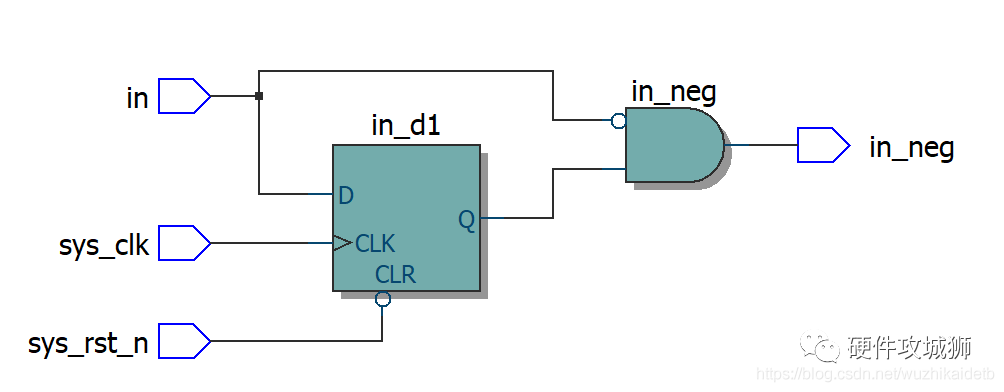

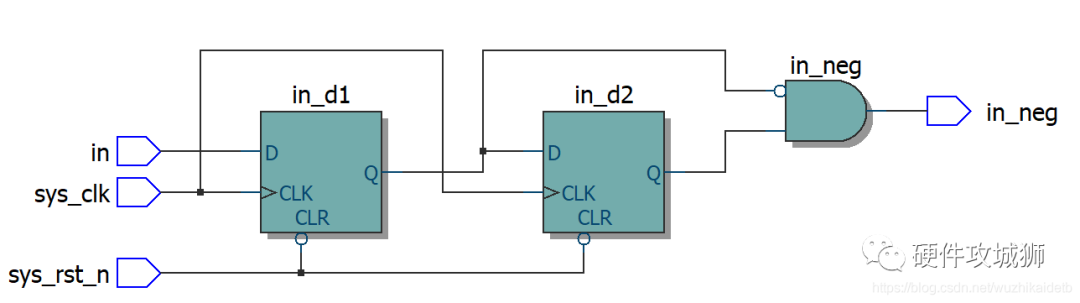

2.3、RTL電路

上圖為生成的RTL電路:該電路由一級D觸發器+與邏輯門構成。

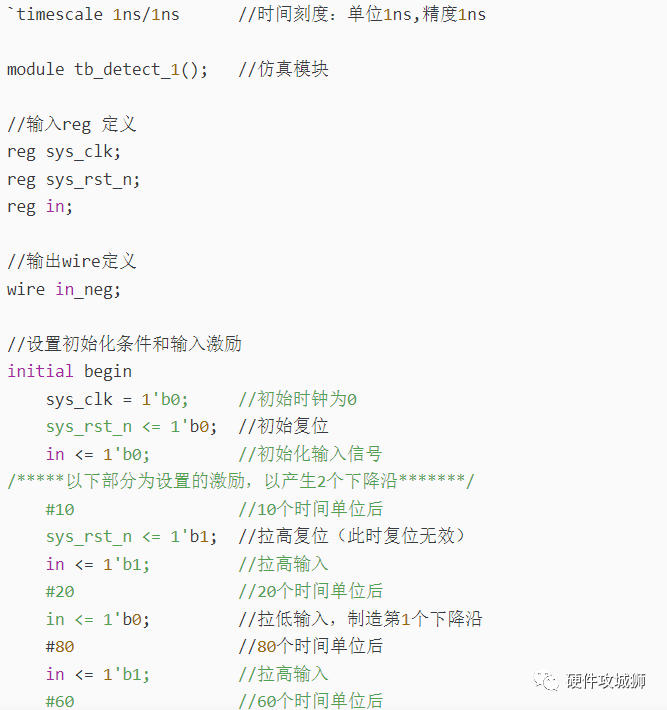

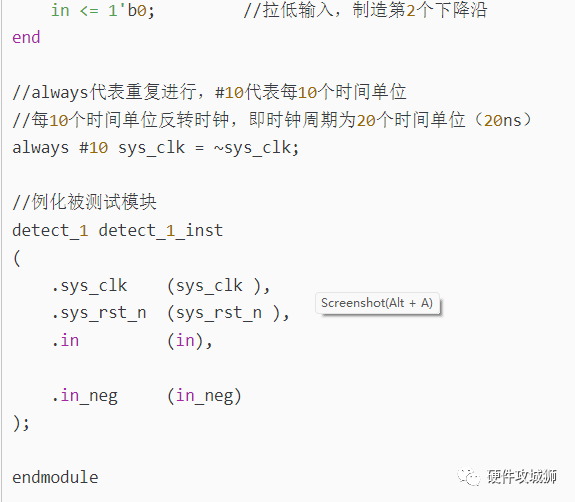

2.4、Testbench

Testbench文件需要例化剛剛設計好的模塊,并設置好激勵。

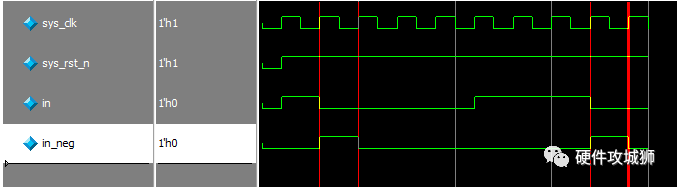

2.5、仿真結果

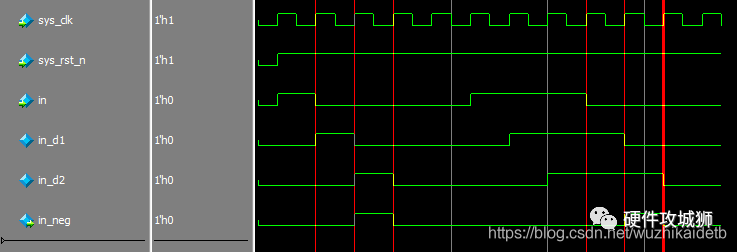

使用ModelSim執行仿真,仿真出來的波形如所示:

從波形圖可以看到:

10ns后停止復位

在第1條參考線處輸入信號 in 產生了第1個下降沿信號

在第3條參考線處輸入信號 in 產生了第2個下降沿信號

在第1條參考線和第2條參考線之間的產生了一個周期的下降沿指示信號 in_neg

在第3條參考線和第4條參考線之間的產生了一個周期的下降沿指示信號 in_neg

3、采用2級觸發器的邊沿檢測電路(以下降沿為例)

3.1、設計方法

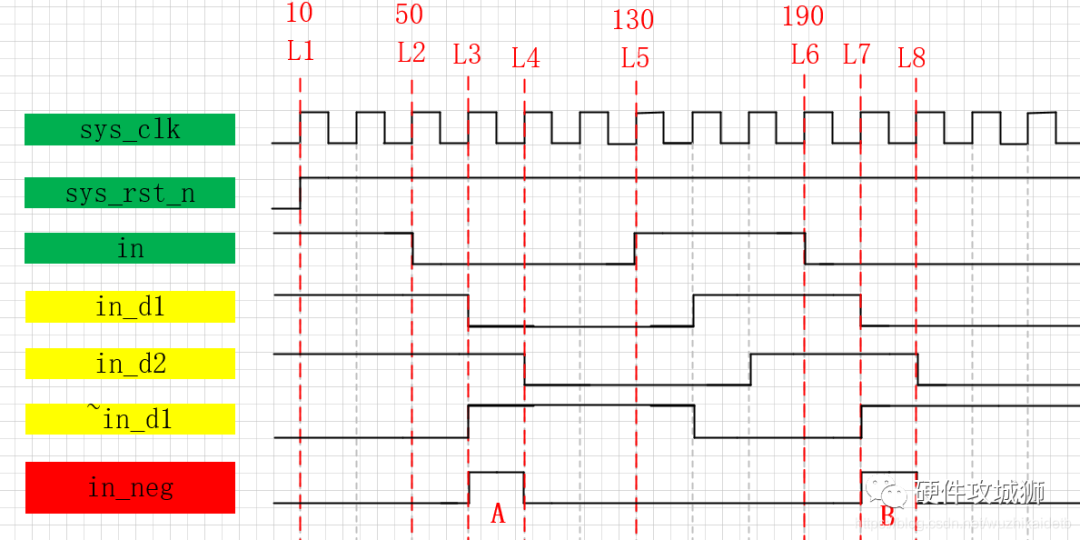

設計波形圖如下所示:

各信號說明如下:

sys_clk:基準時鐘信號(這里設定為50MHz,周期20ns)

sys_rst_n:低電平有效的復位信號

in:輸入信號,需要對其進行下降沿檢測

in_d1:對輸入信號寄存1拍

in_d2:對輸入信號寄存2拍

~in_d1:in_d1信號的反相信號

in_neg:得到的下降沿指示信號,該信號為 ~ind1 && ind2

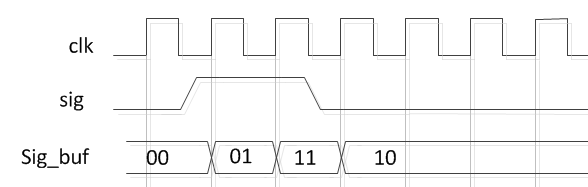

對上圖進行分析:

信號in是我們需要對其進行下降沿檢測的信號

信號in_d1是使用寄存器寄存in信號,即對其打1拍

信號in_d2是使用寄存器寄存in_d1信號,即對其打1拍

信號~in_d1是將信號in_d1反向

輸入信號開始為高電平,在L2處變為低電平,產生第1個下降沿,在L5出產生第2個下降沿

A處為產生的第1個下降沿指示信號,B處為產生的第2個下降沿指示信號

輸出的下降沿指示信號落后下降沿一個時鐘周期,這是因為對輸入信號進行了寄存以消除亞穩態

由此我們可以推導出邊沿檢測信號產生的一般方法:

將需要檢測的信號分別寄存1拍、2拍,同步到系統時鐘域下,得到信號 in_d1、in_d2

將in_d1信號反向,得到信號 ~in_d1

將in_d2信號反向,得到信號 ~in_d2

通過組合邏輯電路可以得到下降沿信號 in_neg:assign in_neg = ~in_d1 && in_d2

同樣通過組合邏輯電路可以得到上升沿信號 in_pos:assign in_pos = in_d1 && ~in_d2

雙邊沿檢測就是將上兩條加(或運算)起來就可以了,化簡后有:雙邊沿信號 in_both = in_d1 ^ in_d2

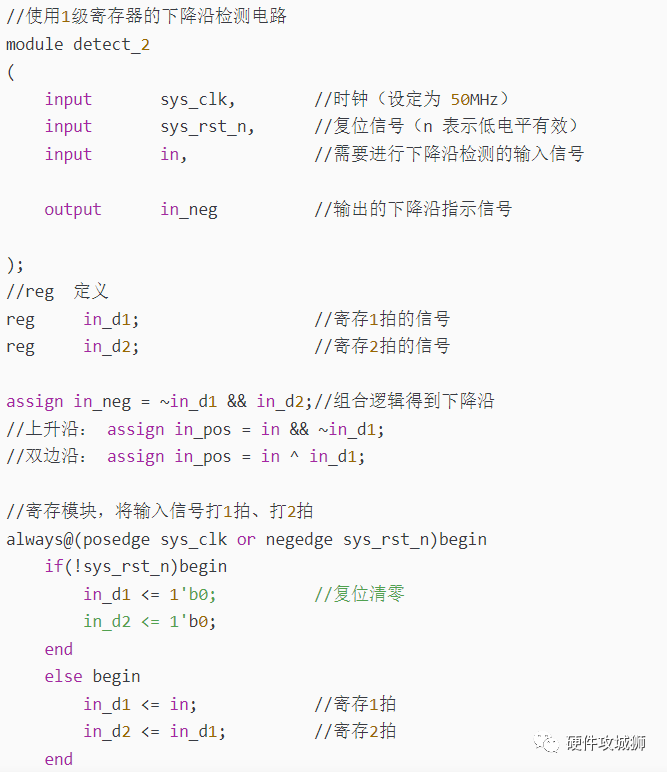

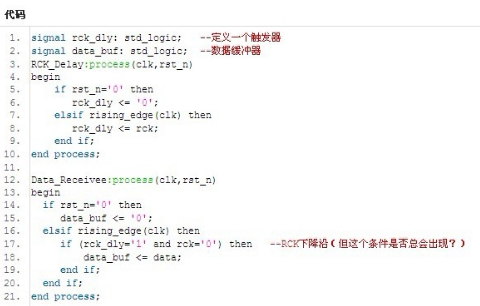

3.2、Verilog實現

根據上文分析不難編寫Verilog代碼如下:

3.3、RTL電路

上圖為生成的RTL電路:該電路由2級D觸發器+與邏輯門構成。

3.4、Testbench

Testbench文件同2.4章。

3.5、仿真結果

使用ModelSim執行仿真,仿真出來的波形如所示:

從波形圖可以看到:

10ns后停止復位

在第1條參考線處輸入信號 in 產生了第1個下降沿信號

在第4條參考線處輸入信號 in 產生了第2個下降沿信號

在第2條參考線和第3條參考線之間的產生了一個周期的下降沿指示信號 in_neg

在第5條參考線和第6條參考線之間的產生了一個周期的下降沿指示信號 in_neg

兩級寄存器構成的邊沿檢測電路可以有效的防止亞穩態的產生,產生的使能信號會落后一個時鐘周期。

責任編輯:彭菁

-

觸發器

+關注

關注

14文章

2039瀏覽量

62138 -

檢測信號

+關注

關注

0文章

8瀏覽量

6396 -

時鐘信號

+關注

關注

4文章

468瀏覽量

29226

原文標題:4、參考

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA設計中的邊沿檢測問題

什么是邊沿檢測

什么是邊沿檢測

評論