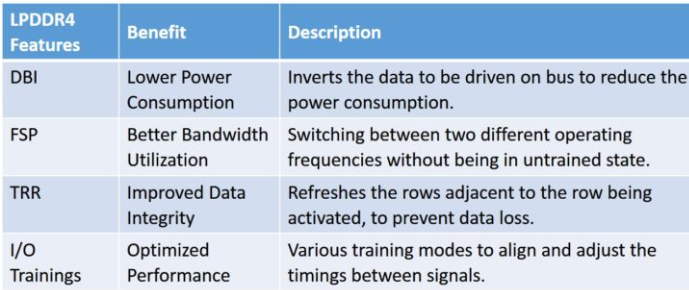

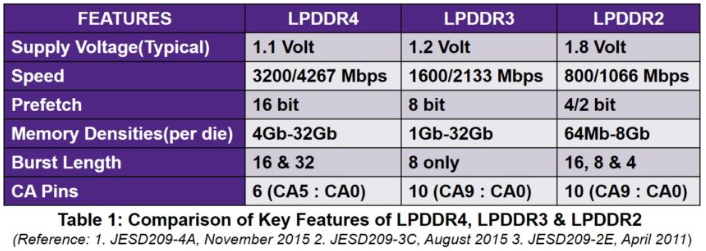

移動行業正在以非常快的速度增長,其對數據和帶寬的永無止境的渴望。我們見證了從撥號盤到觸摸屏,從黑白顯示器到具有數百萬種顏色的QHD 4k顯示器,以及從KB到GB的內存空間在很短的時間內的變化。最大的挑戰是在不影響性能或在功耗列中添加任何重要數字的情況下增加帶寬。應對這一挑戰的解決方案是JEDEC發布的LPDDR或移動DDR標準。該標準已經進行了多次修訂,最新的是LPDDR4。LPDDR4 提供 4266 Mbps 的數據帶寬,幾乎是 LPDDR3 的兩倍。與 LPDDR3 相比,它還顯著降低了功耗。

在本博客中,我們將討論使 LPDDR4 在功耗、帶寬利用率、數據完整性和性能方面高效的功能。

DBI(數據總線反轉)

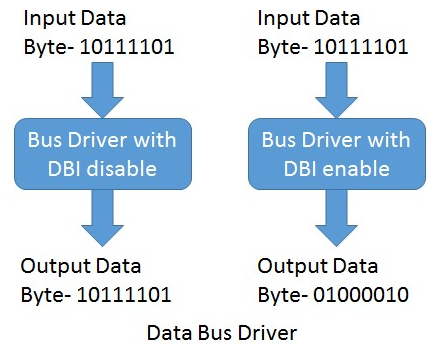

LPDDR4 中引入了一種新的 I/O 信令方案,稱為低壓擺幅端接邏輯 (LVSTL)。LVSTL 使用的電壓電平明顯低于以前版本的 LPDDR 中使用的電壓電平。這種信令方案的另一個優點是,當低電平(0)通過I/O驅動器驅動時,它不消耗終止功率。這意味著如果數據流中有更多的零,則消耗的功率將更少。引入了 DBI 功能,以在數據流中保留比 1 更多的零。DBI 在字節級粒度下工作。每當一個字節包含超過四個位數的位為 <> 時,驅動程序將反轉整個字節并發送相應的數據掩碼反轉 (DMI) 位,以通知接收器相應的字節已反轉。

FSP(頻率設定點)

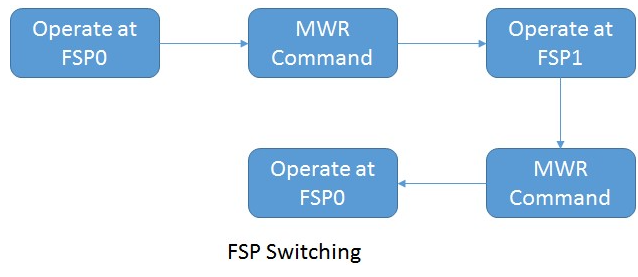

LPDDR4 增加了兩組物理寄存器空間(FSP0 和 FSP1),無需重新訓練即可在兩個不同的工作頻率之間切換。這些寄存器集以兩種不同的頻率存儲DRAM所需的所有操作參數,一種處于有效模式,另一種處于陰影模式。DRAM 將使用兩種頻率進行訓練,參數將在命令總線訓練模式下存儲在寄存器集中。FSP0 和 FSP1 之間的切換,反之亦然,只需在模式寄存器上寫入即可快速完成。

TRR(目標行刷新)

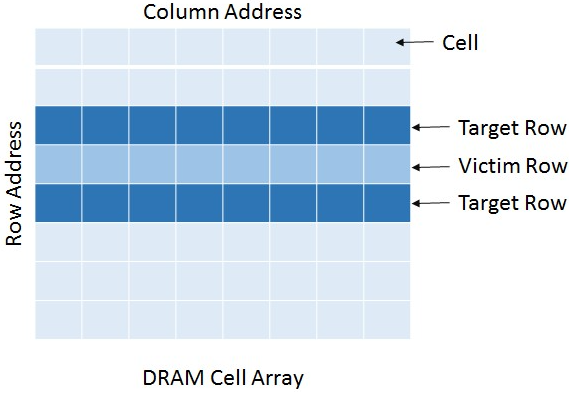

在相同芯片尺寸內,內存密度的增加會導致 DRAM 單元更小。與較大的電池相比,較小的電池可以存儲較小的電荷,這反過來又可以降低噪聲容限,從而使系統更容易出現數據錯誤。此外,密集放置的細胞對串擾干擾的免疫力較低,最終導致數據錯誤。要對行執行任何數據操作,需要先激活它。這里的“激活”意味著將行的電池置于較高的電壓電平,而該行的其他行保持較低的電壓電平。當一行被快速激活時,其電壓電平也會相應變化,最終由于電池的靠近而加速相鄰行電池的放電速率。由于DRAM單元以電荷的形式將數據信息存儲在電容器中,這些電荷往往會在一段時間內放電,因此在刷新周期內需要一個刷新周期來保留存儲的電荷。由于相鄰行電池的放電速率加快,可能會導致數據丟失,因為電容器在下一個刷新周期到來之前已完全放電。為了克服這種情況,LPDDR4 引入了目標行刷新 (TRR) 機制。TRR 限制刷新周期內單行的最大激活次數(MAC 計數)。每當每行的激活計數(目標行)達到 MAC 計數時,TRR 過程將刷新相鄰行(受害行)以避免數據丟失。

I/O 信號培訓

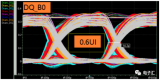

LPDDR4 提供了多種訓練,以對齊或重新調整 I/O 信號相對于 CLK 或其他信號引入的延遲。根據 LPDDR4 的標準物理接口定義,有 CLK、CS、CA、DQ 和 DQS 信號需要正確對齊才能成功傳輸數據。由于CA線在CLK信號處采樣,因此CA和CLK之間應存在適當的相位關系。類似地,DQ在DQS信號上采樣,因此兩者之間應該存在相位關系。為了保持這些階段關系,LPDDR4提出了訓練機制。讓我們看看這些:

指揮總線培訓:這用于將CS和CA信號相對于CLK信號對齊。上電時,接收器配置為低速操作。在高頻下工作時,必須對接收器進行訓練。時序裕量需要根據CBT程序實現的更高時鐘頻率重新調整。CBT 模式的進入和退出由模式寄存器寫入命令控制。在CBT模式下,DRAM將切換到FSP_OP設置,這也需要進行訓練。DRAM 在 CS 信號處對 CA 總線進行采樣,并將采樣信號的反饋提供給控制器,以便對 CS 和 CA 信號進行定時調整。

寫入分級:這用于調整 DQS 輸入信號相對于 CLK 信號的延遲。寫均衡訓練模式的進入和退出由模式寄存器寫入命令控制。DQS 信號由控制器驅動,DRAM 對 DQS 邊緣的 CLK 信號進行采樣。DRAM 通過在 DQ 上提供捕獲的 CLK 級別的反饋來響應控制器。此反饋可識別 DQS 相對于 CLK 的超前或滯后,以便控制器可以相應地重新調整延遲。

寫作訓練(DQS-DQ訓練): 這用于將 DQ 輸入信號延遲與 DQS 輸入信號對齊。進入寫入訓練模式時,MPC WR_DQ_FIFO命令必須由控制器發出。此命令在 DRAM 中寫入用戶定義的數據,然后控制器發出 MPC RD_DQ_FIFO命令從同一位置讀回數據,并比較寫入和讀取的數據以重新調整 DQ 線路上的延遲。

這些功能使 LPDDR4 成為一個完整的封裝,非常適合用作任何移動 SoC 中的 RAM。這些功能必須在基于 LPDDR4 的 SoC 設計的任何驗證計劃中解決。Synopsys 為 LPDDR4 提供了完整的驗證解決方案,包括 JEDEC 和供應商部件的運行時選擇、一組內置協議、時序和數據完整性檢查、可配置的時序參數、內置的功能覆蓋范圍和驗證計劃以及對內存的后門訪問。

審核編輯:郭婷

-

顯示器

+關注

關注

21文章

5058瀏覽量

141348 -

寄存器

+關注

關注

31文章

5421瀏覽量

123303 -

LPDDR4

+關注

關注

1文章

41瀏覽量

23674

發布評論請先 登錄

論手機運行內存 LPDDR 4X在LPDDR4的基礎上有哪些提升

使用了IMX8M Plus+PCA9450C+LPDDR4,如何才能降低SOC和LPDDR4的工作頻率?

lpddr4頻率無法修改怎么解決?

LPDDR4:是什么讓它更快并降低功耗

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部參考時鐘設計指南

LPDDR4是什么意思?LPDDR4X內存是什么意思?

DDR4、LPDDR4和LPDDR4x的區別

LPDDR4:移動SoC RAM的整體封裝

LPDDR4:移動SoC RAM的整體封裝

評論