集成電路進人后摩爾時代以來,安全、可靠的軟硬件協同設計、冗余定制、容錯體系結構和協議、光機電一體化等新的設計趨勢促使片內測試 (On-ChipTest)/片外測試(OIf-Chip Test) 整體測試解決方案趨于復雜化:先進工藝路線的發展,促使集成電路失效故障測試模型不斷演化:芯片尺寸封裝 ( ChipScale Package, CSP)、圓片級封裝( Wafer Level Package, WLP)、硅通孔(Through Silicon Via, TSV)、三維集成等先進封裝工藝,帶來了新的測試工序和復雜光機電集成失效特性:這些技術的演進也導致集成電路測試變得日益復雜。互聯網、物聯網、云計算、大數據等新應用、新業態的出現,不斷推動集成電路測試技術的發展和信息化進程。

集成電路測試既是集成電路設計的組成部分,也是芯片制造的一個環節,集成電路測試的主要作用是檢測電路存在的問題、問題出現的位置和修正問題的方法。如果一個電路未能通過測試。可能的原因包括測試本身、產品設計,制造過程等方面。測試技術研究就是在兼顧品質和經濟性的條件下制定合適的測試方案,即用最低的成本檢出最多的故障。

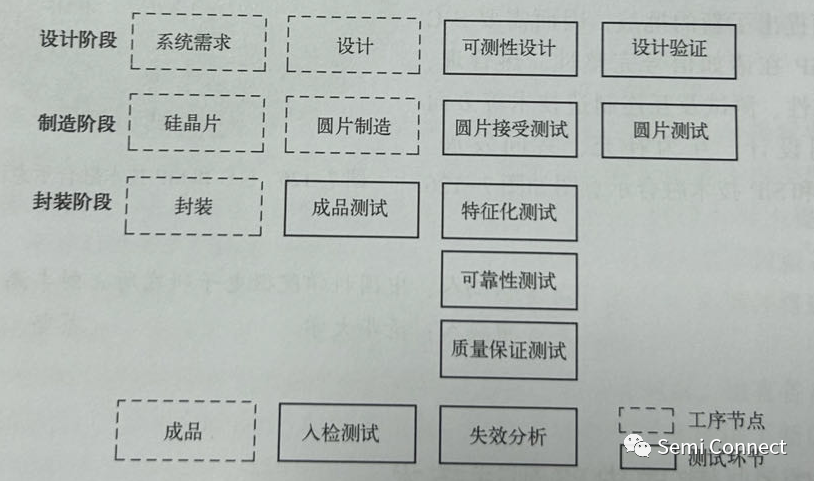

測試貫穿于集成電路生產過程,分為設計驗證、檢測篩選、質量控制等。下圖所示的是集成電路產業鏈中主要的測試環節。由圖可以看出,設計階段的可測性設計和設計驗證,制造階段的圓片接受測試和圓片測試 ( CircuitProbe),以及封裝階段的成品測試、失效分析等,都屬于測試技術領域。

特征化測試是對功能、直流特性、交流特性進行全面的功能/性能檢測,用以表征集成電路各項極限參數,驗證設計的正確性。

圓片級測試是在集成電路制造后進行的園片狀態下的測試,用于最初階段的合格電路的篩選。隨著圓片級封裝、三維異質集成、測試模式演變、電路修調定制等需求的發展,圓片級測試變得更具挑戰性。

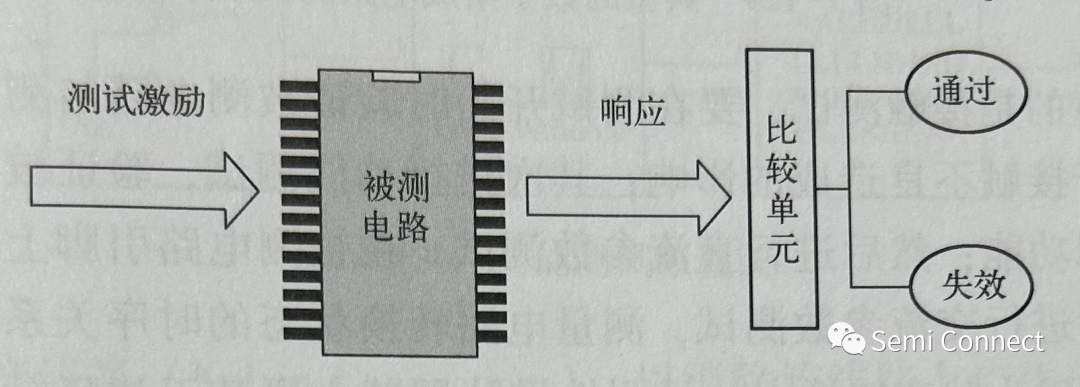

成品測試是封裝后的測試環節,用以檢測集成電路在此階段是否符合規格要求。有時也會加人系統應用級測試,通常會將前面環節中實施成本較高的測試項目放在該測試環節,以避免不合格產品進人最終應用環節下圖所示的是基本的測試原理框圖。由圖可知,基本的測試原理是對被測電路施加一定的激勵條件,觀測被測電路的響應,與期望值進行對比,如果一致,表明電路是好的;如果不一致,則表明電路存在故障。

按測試方案的區位界定,集成電路測試可以分為片內測試和片外測試兩類。片內測試又稱可測性設計 (Design For Testability, DFT)。DFT 技術研究的主要目的是提高故障可觀測性,降低對外部測試儀器儀表性能的要求,減少測試時問,以實現測試品 質和經濟性的均衡。但考慮其帶來電路設計復雜性的增加、芯片面積的增加、額外故障的引 ,以及在模擬/射頻等范圍技術尚不完善等因素,片外測試技術依然是不可忽視的研究重點。

根據被測集成電路類型的不同,集成電路測試可以分為數宇集成電路測試模擬集成電路測試、混合信號集成電路測試、高速信號集成電路測試、射頻集成電路測試、可編程器件測試、存儲器集成電路測武、系統芯片測試、物聯網芯片/微機電系統芯片測試等。

-

芯片

+關注

關注

459文章

52145瀏覽量

435949 -

集成電路

+關注

關注

5417文章

11942瀏覽量

367036 -

封裝

+關注

關注

128文章

8474瀏覽量

144759 -

物聯網

+關注

關注

2927文章

45847瀏覽量

387767 -

封裝工藝

+關注

關注

3文章

64瀏覽量

8112

原文標題:集成電路測試定義,積體電路測試定義,Definition of IC Test

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

什么是小尺寸集成電路CDM測試?

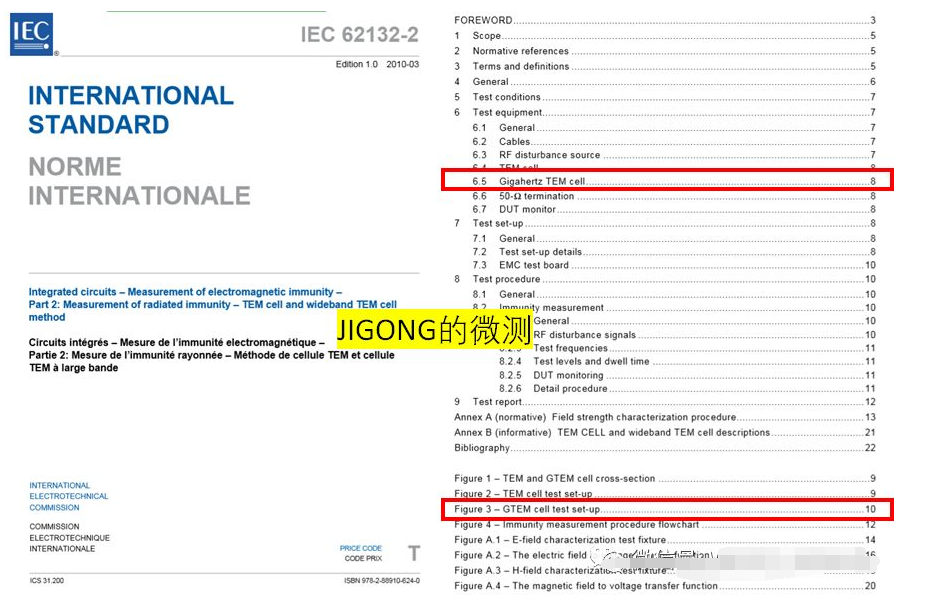

集成電路電磁騷擾測試方法

集成電路測試技術與應用

集成電路IC的EMC測試標準

集成電路測試定義

集成電路測試定義

評論