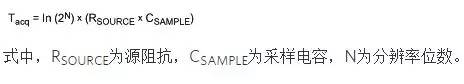

采集時(shí)間

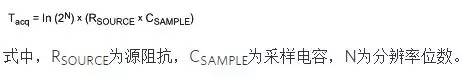

采集時(shí)間是從釋放保持狀態(tài)(由采樣-保持輸入電路執(zhí)行)到采樣電容電壓穩(wěn)定至新輸入值的1 LSB范圍之內(nèi)所需要的時(shí)間。采集時(shí)間(Tacq)的公式如下:

混疊

根據(jù)采樣定理,超過奈奎斯特頻率的輸入信號頻率為“混疊”頻率。也就是說,這些頻率被“折疊”或復(fù)制到奈奎斯特頻率附近的其它頻譜位置。為防止混疊,必須對所有有害信號進(jìn)行足夠的衰減,使得ADC不對其進(jìn)行數(shù)字化。欠采樣時(shí),混疊可作為一種有利條件。

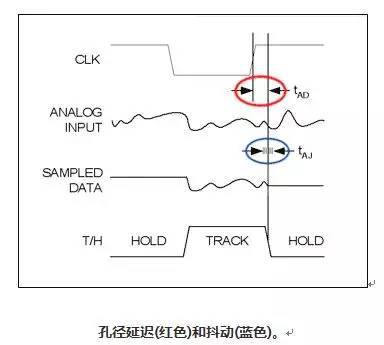

孔徑延遲

ADC中的孔徑延遲(tAD)是從時(shí)鐘信號的采樣沿(下圖中為時(shí)鐘信號的上升沿)到發(fā)生采樣時(shí)之間的時(shí)間間隔。當(dāng)ADC的跟蹤-保持切換到保持狀態(tài)時(shí),進(jìn)行采樣。

孔徑抖動(dòng)

孔徑抖動(dòng) (tAJ) 是指采樣與采樣之間孔徑延遲的變化,如圖所示。典型的ADC孔徑抖動(dòng)值遠(yuǎn)遠(yuǎn)小于孔徑延遲值。

二進(jìn)制編碼(單極性)

標(biāo)準(zhǔn)二進(jìn)制是一種常用于單極性信號的編碼方法。二進(jìn)制碼(零至滿幅)的范圍為從全0 (00...000)到全1的正向滿幅值(11...111)。中間值由一個(gè)1 (MSB)后邊跟全0 (10...000)表示。該編碼類似于偏移二進(jìn)制編碼,后者支持正和負(fù)雙極性傳遞函數(shù)。

雙極性輸入

術(shù)語“雙極性”表示信號在某個(gè)基準(zhǔn)電平上、下擺動(dòng)。單端系統(tǒng)中,輸入通常以模擬地為基準(zhǔn),所以雙極性信號為在地電平上、下擺動(dòng)的信號。差分系統(tǒng)中,信號不以地為基準(zhǔn),而是正輸入以負(fù)輸入為參考,雙極性信號則指正輸入信號能夠高于和低于負(fù)輸入信號。

共模抑制(CMRR)

共模抑制是指器件抑制兩路輸入的共模信號的能力。共模信號可以是交流或直流信號,或者兩者的組合。共模抑制比(CMRR)是指差分信號增益與共模信號增益之比。CMRR通常以分貝(dB)為單位表示。

串?dāng)_(Crosstalk)

串?dāng)_表示每路模擬輸入與其它模擬輸入的隔離程度。對于具有多路輸入通道的ADC,串?dāng)_指從一路模擬輸入信號耦合到另一路模擬輸入的信號總量,該值通常以分貝(dB)為單位表示;對于具有多路輸出通道的DAC,串?dāng)_是指一路DAC輸出更新時(shí)在另一路DAC輸出端產(chǎn)生的噪聲總量。

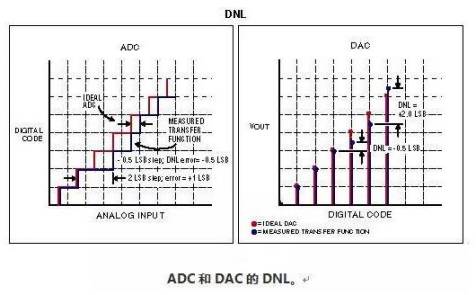

微分非線性(DNL)誤差

對于ADC,觸發(fā)任意兩個(gè)連續(xù)輸出編碼的模擬輸入電平之差應(yīng)為1 LSB (DNL = 0),實(shí)際電平差相對于1 LSB的偏差被定義為DNL。對于DAC,DNL誤差為連續(xù)DAC編碼的理想與實(shí)測輸出響應(yīng)之差。理想DAC響應(yīng)的模擬輸出值應(yīng)嚴(yán)格相差一個(gè)編碼(LSB)(DNL = 0)。(DNL指標(biāo)大于或等于1LSB保證單調(diào)性。)(見“單調(diào)”。)

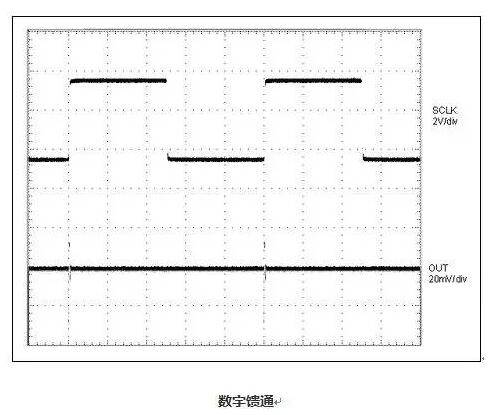

數(shù)字饋通

數(shù)字饋通是指DAC數(shù)字控制信號變化時(shí),在DAC輸出端產(chǎn)生的噪聲。在下圖中,DAC輸出端的饋通是串行時(shí)鐘信號噪聲的結(jié)果。

動(dòng)態(tài)范圍

動(dòng)態(tài)范圍定義為器件本底噪聲至其規(guī)定最大輸出電平之間的范圍,通常以dB表示。ADC的動(dòng)態(tài)范圍為ADC能夠分辨的信號幅值范圍;如果ADC的動(dòng)態(tài)范圍為60dB,則其可分辨的信號幅值為x至1000x。對于通信應(yīng)用,信號強(qiáng)度變化范圍非常大,動(dòng)態(tài)范圍非常重要。如果信號太大,則會(huì)造成ADC輸入過量程;如果信號太小,則會(huì)被淹沒在轉(zhuǎn)換器的量化噪聲中。

有效位數(shù)(ENOB)

ENOB表示一個(gè)ADC在特定輸入頻率和采樣率下的動(dòng)態(tài)性能。理想ADC的誤差僅包含量化噪聲。當(dāng)輸入頻率升高時(shí),總體噪聲(尤其是失真分量)也增大,因此降低ENOB和SINAD(參見“信號與噪聲+失真比(SINAD)”)。

加載-感應(yīng)輸出

一種測量技術(shù),在電路的遠(yuǎn)端點(diǎn)加載電壓(或電流),然后測量(檢測)產(chǎn)生的電流(或電壓)。例如,帶有集成輸出放大器的DAC有時(shí)就包含加載-感應(yīng)輸出。輸出放大器可提供反相輸入用于外部連接,反饋通路必須通過外部形成閉環(huán)。

全功率帶寬(FPBW)

ADC工作時(shí)施加的模擬輸入信號等于或接近轉(zhuǎn)換器的規(guī)定滿幅電壓。然后將輸入頻率提高到某個(gè)頻率,使數(shù)字轉(zhuǎn)換結(jié)果的幅值降低3dB。該輸入頻率即為全功率帶寬。

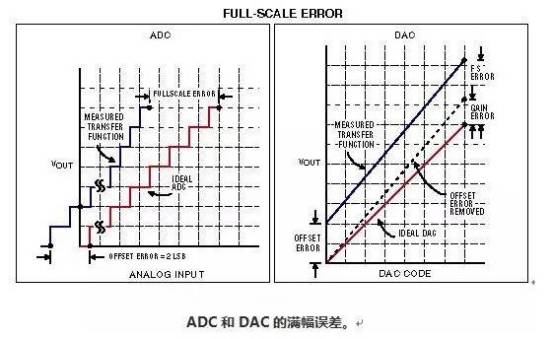

滿幅(FS)誤差

滿幅誤差為觸發(fā)跳變至滿幅編碼的實(shí)際值與理想模擬滿幅跳變值之差。滿幅誤差等于“失調(diào)誤差+增益誤差”,如下圖所示。

FS增益誤差(DAC)

數(shù)/模轉(zhuǎn)換器(DAC)的滿幅增益誤差為實(shí)際與理想輸出跨距之差。實(shí)際跨距為輸入設(shè)置為全1時(shí)與輸入設(shè)置為全0時(shí)的輸出之差。所有數(shù)據(jù)轉(zhuǎn)換器的滿幅增益誤差都與選擇用于測量增益誤差的基準(zhǔn)有關(guān)。

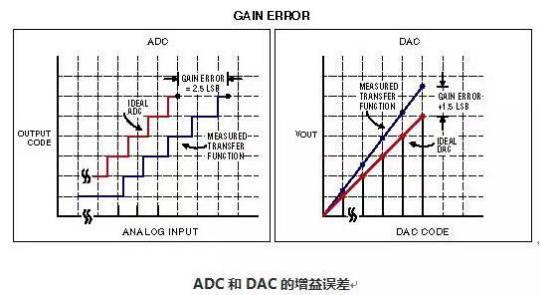

增益誤差

ADC或DAC的增益誤差表示實(shí)際傳遞函數(shù)的斜率與理想傳遞函數(shù)的斜率的匹配程度。增益誤差通常表示為LSB或滿幅范圍的百分比(%FSR),可通過硬件或軟件校準(zhǔn)進(jìn)行消除。增益誤差等于滿幅誤差減去失調(diào)誤差。

增益誤差漂移

增益誤差漂移指環(huán)境溫度引起的增益誤差變化,通常表示為ppm/°C。

增益一致性

增益一致性表示多通道ADC中所有通道增益的匹配程度。為計(jì)算增益的一致性,向所有通道施加相同的輸入信號,然后記錄最大的增益偏差,通常用dB表示。

尖峰脈沖

尖峰脈沖指MSB跳變時(shí)在DAC輸出端產(chǎn)生的電壓瞬態(tài)振蕩,通常表示為nV?s,等于電壓-時(shí)間曲線下方的面積。

諧波

周期信號的諧波為信號基頻整數(shù)倍的正弦分量。

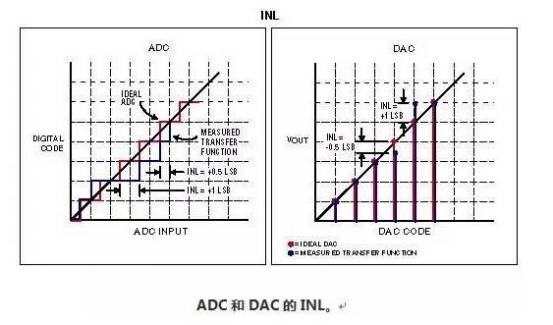

積分非線性(INL)誤差

對于數(shù)據(jù)轉(zhuǎn)換器,積分非線性(INL)是實(shí)際傳遞函數(shù)與傳遞函數(shù)直線的偏差。消除失調(diào)誤差和增益誤差后,該直線為最佳擬合直線或傳遞函數(shù)端點(diǎn)之間的直線。INL往往被稱為“相對精度”。

互調(diào)失真(IMD)

IMD是指由于電路或器件的非線性產(chǎn)生的原始信號中并不存在的新頻率分量的現(xiàn)象。IMD包括諧波失真和雙音失真。測量時(shí),將其作為將所選交調(diào)產(chǎn)物(即IM2至IM5)的總功率與兩個(gè)輸入信號(f1和f2)的總功率之比。2階至5階交調(diào)產(chǎn)物如下:

·2階交調(diào)產(chǎn)物(IM2):f1 + f2、f2 - f1

·3階交調(diào)產(chǎn)物(IM3):2 x f1 - f2、2 x f2 - f1、2 x f1 + f2、2 x f2 + f1

·4階交調(diào)產(chǎn)物(IM4):3 x f1 - f2、3 x f2 - f1、3 x f1 + f2、3 x f2 + f1

·5階交調(diào)產(chǎn)物(IM5):3 x f1 - 2 x f2、3 x f2 - 2 x f1、3 x f1 + 2 x f2、3 x f2 + 2 x f1

最低有效位(LSB)

在二進(jìn)制數(shù)中,LSB為最低加權(quán)位。通常,LSB為最右側(cè)的位。對于ADC或DAC,LSB的權(quán)重等于轉(zhuǎn)換器的滿幅電壓范圍除以2N,其中N為轉(zhuǎn)換器的分辨率。對于12位ADC,如果滿幅電壓為2.5V,則1LSB = (2.5V/212) = 610μV

MSB跳變

MSB跳變(中間刻度點(diǎn))時(shí),MSB由低電平變?yōu)楦唠娖剑渌袛?shù)據(jù)位則由高電平變?yōu)榈碗娖剑换蛘進(jìn)SB由高電平變?yōu)榈碗娖剑渌鼣?shù)據(jù)位由低電平變?yōu)楦唠娖健@纾?1111111變?yōu)?0000000即為MSB跳變。MSB跳變往往產(chǎn)生最嚴(yán)重的開關(guān)噪聲(見尖峰脈沖)。

/b>單調(diào)

在序列中,如果對于每個(gè)n,Pn + 1總是大于或等于Pn,則說該序列單調(diào)增大;類似地,如果對于每個(gè)n,Pn + 1總是小于或等于Pn,則說該序列單調(diào)減小。對于DAC,如果模擬輸出總是隨DAC編碼輸入的增大而增大,則說該DAC是單調(diào)的;對于ADC,如果數(shù)字輸出編碼總是隨模擬輸入的增大而增大,則說該ADC是單調(diào)的。如果轉(zhuǎn)換器的DNL誤差不大于±1LSB,則能夠保證單調(diào)。

最高有效位(MSB)

在二進(jìn)制數(shù)中,MSB為最高加權(quán)位。通常,MSB為最左側(cè)的位。

乘法DAC (MDAC)

乘法DAC允許將交流信號施加至基準(zhǔn)輸入。通過將感興趣的信號連接至基準(zhǔn)輸入,并利用DAC編碼縮放信號,DAC可用作數(shù)字衰減器。

無丟失編碼

當(dāng)斜線上升信號施加至ADC的模擬輸入端時(shí),如果ADC產(chǎn)生所有可能的數(shù)字編碼,則該ADC無丟失編碼。

奈奎斯特頻率

奈奎斯特定理說明:ADC的采樣率必須至少為信號最大帶寬的兩倍才能無失真地完整恢復(fù)模擬信號。該最大帶寬被稱為奈奎斯特頻率。

偏移二進(jìn)制編碼

偏移二進(jìn)制是一種常用于雙極性信號的編碼方法。在偏移二進(jìn)制編碼中,負(fù)向最大值(負(fù)向滿幅值)用全0 (00...000)表示,正向最大值(正向滿幅值)用全1 (11...111)表示。零幅由一個(gè)1 (MSB)后邊跟全0 (10...000)表示。該方法與標(biāo)準(zhǔn)二進(jìn)制類似,后者常用于單極性信號(參見二進(jìn)制編碼,單極性)。

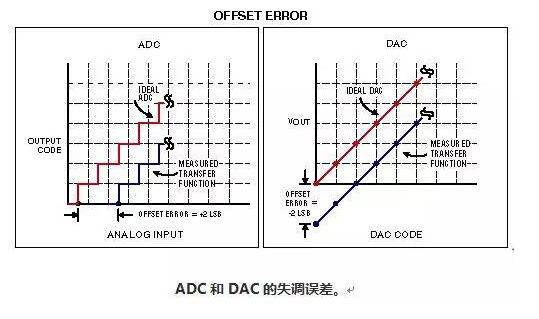

失調(diào)誤差(雙極性)

雙極性轉(zhuǎn)換器失調(diào)誤差的測量與單極性轉(zhuǎn)換器失調(diào)誤差的測量類似,但在雙極性傳遞函數(shù)的中間點(diǎn)測量零幅處的誤差(參見失調(diào)誤差單極性)

失調(diào)誤差(單極性)

失調(diào)誤差常稱為“零幅”誤差,指在某個(gè)工作點(diǎn),實(shí)際傳遞函數(shù)與理想傳遞函數(shù)的差異。對于理想數(shù)據(jù)轉(zhuǎn)換器,第一次跳變發(fā)生在零點(diǎn)以上0.5LSB處。對于ADC,向模擬輸入端施加零幅電壓并增加,直到發(fā)生第一次跳變;對于DAC,失調(diào)誤差為輸入編碼為全0時(shí)的模擬輸出。

失調(diào)誤差漂移

失調(diào)誤差漂移指環(huán)境溫度引起的失調(diào)誤差變化,通常表示為ppm/°C。

過采樣

對于ADC,如果采樣模擬輸入的頻率遠(yuǎn)遠(yuǎn)高于奈奎斯特頻率,則稱為過采樣。過采樣有效降低了噪底,所以提高ADC的動(dòng)態(tài)范圍。提高動(dòng)態(tài)范圍又進(jìn)而提高了分辨率。過采樣是Σ-Δ ADC的基礎(chǔ)。

相位匹配

相位匹配表示施加至多通道ADC所有通道的完全相同信號的相位匹配程度。相位匹配指所有通道中的最大相位偏移,通常用度表示。

電源抑制比(PSRR)

電源抑制比(PSRR)指電源電壓變化與滿幅誤差變化之比,以dB表示。

量化誤差

對于ADC,量化誤差定義為實(shí)際模擬輸入與表示該值的數(shù)字編碼之間的差異(參見“量化”)。

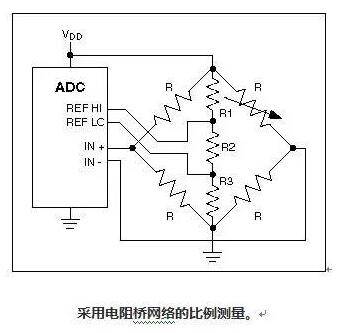

比例測量

施加至ADC電壓基準(zhǔn)輸入的電壓不是恒定電壓,而是與施加至變送器(即負(fù)載單元或電橋)的信號成比例。這種類型的測量稱為比例測量,它消除了基準(zhǔn)電壓變化引起的所有誤差。下圖中使用電阻橋的方法就是比例測量的一個(gè)例子。

分辨率

ADC分辨率為用于表示模擬輸入信號的位數(shù)。為了更準(zhǔn)確地復(fù)現(xiàn)模擬信號,就必須提高分辨率。使用較高分辨率的ADC也降低量化誤差。對于DAC,分辨率與此類似:DAC的分辨率越高,增大編碼時(shí)在模擬輸出端產(chǎn)生的步進(jìn)越小。

有效值(RMS)

交流波形的RMS值為有效直流值或該信號的等效直流信號。計(jì)算交流波形的RMS值時(shí),先對交流波形進(jìn)行平方以及時(shí)間平均,然后取其平方根。對于正弦波,RMS值為峰值的 2/2 (或0.707)倍,也就是峰-峰值的0.354倍。

采樣率/頻率

采樣率或采樣頻率以“采樣/秒”(sps)表示,指ADC采集(采樣)模擬輸入的速率。對于每次轉(zhuǎn)換執(zhí)行一次采樣的ADC(如SAR、Flash ADC或流水線型ADC),采樣速率也指吞吐率。對于Σ-Δ ADC,采樣率一般遠(yuǎn)遠(yuǎn)高于數(shù)據(jù)輸出頻率。

建立時(shí)間

對于DAC,建立時(shí)間是從更新(改變)其輸出值的命令到輸出達(dá)到最終值(在規(guī)定百分比之內(nèi))之間的時(shí)間間隔。建立時(shí)間受輸出放大器的擺率和放大器振鈴及信號過沖總量的影響。對于ADC,采樣電容電壓穩(wěn)定至1 LSB所需的時(shí)間小于轉(zhuǎn)換器的捕獲時(shí)間至關(guān)重要。

信納比(SINAD)

SINAD是正弦波(ADC的輸入,或DAC恢復(fù)的輸出)的RMS值與轉(zhuǎn)換器噪聲加失真(無正弦波)的RMS值之比。RMS噪聲加失真包括奈奎斯特頻率以下除基波和直流失調(diào)以外的所有頻譜成分。SINAD通常表示為dB。

信噪比(SNR)

信噪比(SNR)是給定時(shí)間點(diǎn)有用信號幅度與噪聲幅度之比,該值越大越好。對于由數(shù)字采樣完美重構(gòu)的波形,理論上的最大SNR為滿幅模擬輸入(RMS值)與RMS量化誤差(剩余誤差)之比。理想情況下,理論上的最小ADC噪聲僅包含量化誤差,并直接由ADC的分辨率(N位)確定:

(除量化噪聲外,實(shí)際ADC也產(chǎn)生熱噪聲、基準(zhǔn)噪聲、時(shí)鐘抖動(dòng)等。)

帶符號二進(jìn)制編碼

帶符號二進(jìn)制編碼方法中,MSB表示二進(jìn)制數(shù)的符號(正或負(fù))。所以,-2的8位表示法為10000010,+2的表示法為00000010。

擺率

擺率是DAC輸出變化的最大速率,或者不會(huì)造成ADC數(shù)字輸出錯(cuò)誤的輸入變化的最大速率。對于帶有輸出放大器的DAC,規(guī)定擺率通常是放大器的擺率。

小信號帶寬(SSBW)

為測量小信號帶寬,向ADC施加一個(gè)幅值足夠小的模擬輸入信號,其擺率不會(huì)限制ADC的性能。然后,掃描輸入頻率,直到數(shù)字轉(zhuǎn)換結(jié)果的幅值降低3dB。小信號帶寬往往受限于相關(guān)采樣-保持放大器的性能。

無雜散動(dòng)態(tài)范圍(SFDR)

無雜散動(dòng)態(tài)范圍(SFDR)是基波(信號成分最大值)RMS幅值與第二大雜散成份(不包含直流失調(diào))的RMS值之比。SFDR以相對于載波的分貝(dBc)表示。

總諧波失真(THD)

THD測量信號的失真成分,用相對于基波的分貝(dB)表示。對于ADC,總諧波失真(THD)是所選輸入信號諧波的RMS之和與基波之比。測量時(shí),只有在奈奎斯特限值之內(nèi)的諧波被包含在內(nèi)。

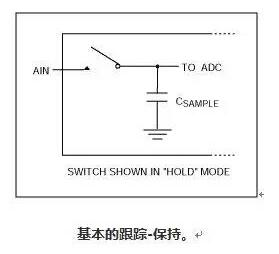

跟蹤-保持

跟蹤-保持往往也被稱為“采樣-保持”,指ADC的輸入采樣電路。跟蹤-保持輸入的最基本表示形式是模擬開關(guān)和電容(見圖)。開關(guān)閉合時(shí),電路處于“跟蹤”模式;開關(guān)開路時(shí),采樣電容保持輸入的最后瞬態(tài)值,電路處于“保持”模式。

轉(zhuǎn)換噪聲

轉(zhuǎn)換噪聲指引起ADC輸出在相鄰輸出編碼之間切換的輸入電壓變化范圍。當(dāng)增大模擬輸入電壓時(shí),由于相關(guān)瞬態(tài)噪聲的原因,觸發(fā)每個(gè)編碼發(fā)生跳變(編碼邊緣)的電壓是不確定的。

二進(jìn)制補(bǔ)碼編碼

二進(jìn)制補(bǔ)碼編碼方法用于正數(shù)和負(fù)數(shù)編碼,簡化加法和減法計(jì)算。該編碼方法中,-2的8位表示法為11111110,+2的表示法為00000010。

欠采樣

欠采樣技術(shù)中,ADC采樣率低于模擬輸入頻率,該條件下將引起混疊。根據(jù)奈奎斯特定理,自然知道欠采樣將丟失信號信息。然而,如果對輸入信號進(jìn)行正確濾波,以及正確選擇模擬輸入和采樣頻率,則可將包含信號信息的混疊成分從較高頻率搬移至較低頻率,然后進(jìn)行轉(zhuǎn)換。該方法有效地將ADC用作下變頻器,將較高帶寬信號搬移到ADC的有效帶寬。要想該技術(shù)取得成功,ADC跟蹤-保持電路的帶寬必須能夠處理預(yù)期的最高頻率信號。

單極性

對于單端模擬輸入ADC,單極性信號輸入范圍為零幅(通常為地)至滿幅(通常為基準(zhǔn)電壓);對于差分輸入ADC,信號輸入范圍為零幅至滿幅,以正輸入相當(dāng)于負(fù)輸入測量輸入范圍。

零幅誤差

參見失調(diào)誤差(單極性)。

審核編輯:劉清

-

dac

+關(guān)注

關(guān)注

43文章

2379瀏覽量

193037 -

LSB

+關(guān)注

關(guān)注

0文章

39瀏覽量

13432 -

CMRR

+關(guān)注

關(guān)注

0文章

85瀏覽量

15184 -

時(shí)鐘信號

+關(guān)注

關(guān)注

4文章

465瀏覽量

29078 -

ADC采樣

+關(guān)注

關(guān)注

0文章

134瀏覽量

13124

原文標(biāo)題:ADC和DAC常用的56個(gè)技術(shù)術(shù)語

文章出處:【微信號:射頻問問,微信公眾號:射頻問問】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

DAC和ADC的56個(gè)常用技術(shù)術(shù)語解析

ADC和DAC常用的技術(shù)術(shù)語

ADC和DAC常用技術(shù)術(shù)語

DAC和ADC的介紹

ADC和DAC常用的56個(gè)技術(shù)術(shù)語分享

ADC和DAC常用術(shù)語匯總

ADAU1401 :SigmaDSP 28/56位音頻處理器,內(nèi)置2個(gè)ADC和4個(gè)DAC

ADAU1701:帶兩個(gè)ADC和四個(gè)DAC的SigmaDSP 28/56位音頻處理器產(chǎn)品手冊

ADAU1401A:帶兩個(gè)ADC和四個(gè)DAC的SigmaDSP 28/56位音頻處理器產(chǎn)品手冊

ADC和DAC常用的56個(gè)技術(shù)術(shù)語

模/數(shù)轉(zhuǎn)換器和數(shù)/模轉(zhuǎn)換的技術(shù)術(shù)語

模數(shù)轉(zhuǎn)換器和DAC的類型

(建議收藏)56個(gè)常用的ADC和DAC技術(shù)術(shù)語

serdes串行發(fā)送和接收是怎么實(shí)現(xiàn)的?serdes就是用56G的ADC和DAC嗎?

如何使用FPGA驅(qū)動(dòng)并行ADC和DAC芯片,使用不同編碼方式的ADC與DAC時(shí)的注意事項(xiàng)

ADC和DAC常用的56個(gè)技術(shù)術(shù)語介紹

ADC和DAC常用的56個(gè)技術(shù)術(shù)語介紹

評論