USB轉(zhuǎn)串口:

CH340C/N/K/E/B/G/T

CH341F/B/C/T/A

USB轉(zhuǎn)打印口:

CH340H/S

CH341F/B/A

USB轉(zhuǎn)I2C:CH341F/B/C/T/A

USB轉(zhuǎn)SPI:CH341F/B/A/H

USB轉(zhuǎn)并口/GPIO:CH341F/B/A

芯片供電注意事項

CH340/CH341等 USB 芯片都支持 5V 和 3.3V 電源電壓,5V 供電時芯片 V3 引腳需要接一個 104 電容到地,3.3V 供電時需要注意以下幾點(diǎn):

★ 與 USB 芯片相連接的所有電路的電源電壓都必須不高于 3.3V。

★ USB 芯片的 VCC 引腳與 V3 引腳必須短接,必須同時輸入 3.3V 電源電壓。

★ 如果使用 ESD 保護(hù)器件/瞬變電壓抑制器件,那么其正電壓應(yīng)該是 3.3V。

芯片電平匹配問題

CH340/CH341 芯片支持 5V與 3.3V 供電,轉(zhuǎn)換的接口為 TTL 電平,輸出高電平與供電電壓保持一致。因此在實(shí)際使用的時候,和相連的對端設(shè)備間要注意電壓匹配的問題。

★ 與芯片相連的 IO 引腳電壓不得超過芯片供電電壓,否則可能會損壞芯片;

★ 在 5V 供電模式下,兼容 3.3V 系統(tǒng),可以直接與 5V 或 3.3V 系統(tǒng)連接,與 1.8V 系統(tǒng)連接時需要外加電平轉(zhuǎn)換電路;

★ 在 3.3V 供電模式下,可以與 3.3V 系統(tǒng)連接,與 1.8V 系統(tǒng)連接時需要外加電平轉(zhuǎn)換電路;

★ 降壓電路可以使用簡單的電阻分壓法,如串聯(lián)1.6K與3.3K電阻可以得到接近3.3V電壓;升壓電路可以參考 boost 升壓電路原理進(jìn)行搭建;當(dāng)然除了上面的方法,也可以直接采用升降壓芯片;

防止電流倒灌問題

在串口應(yīng)用中,當(dāng) CH340/CH341 與其他 IC 譬如 MCU 等芯片相互連接時,若有一方不需要供電工作時,要注意電流倒灌導(dǎo)致未供電的芯片開始工作或工作異常的情況,或者是通過串口下載程序時,MCU 需要復(fù)位以實(shí)現(xiàn)下載時,發(fā)現(xiàn)復(fù)位不成功,原因可能相同。解決辦法:可在 CH340/CH341芯片的 發(fā)送引腳 TXD 上接一個反向二極管,然后再連接到對端 IC。在接收引腳上加一個限流電阻來防止對端 IC 對CH340/CH341倒灌電。

晶體以及電容的選用

對于 CH340/CH341系列需要外接晶振的芯片,在選用晶振時如果選擇 12MHz 的石英晶體,那么旁路電容一般選擇 33pF 的獨(dú)石或高頻瓷片電容。如果選用的低成本陶瓷晶體,那么旁路電路的容量必須用該晶體廠家的推薦值,一般情況下是 47pF。對起振困難或者起振不穩(wěn)定的晶體可以適當(dāng)調(diào)整旁路電容值進(jìn)行測試。

芯片CH340的V3引腳作用

V3 的引腳除了在不同電壓供電模式下接法不同,對于電容數(shù)值選用也是需要注意的。V3 引腳的電容用于內(nèi)部電源節(jié)點(diǎn)退耦,來改善 USB 傳輸過程中的 EMI,通常容量在 4700pF 到 0.1uF 范圍,建議容量為 0.1uF,即 104 電容。

如何提高工作穩(wěn)定性和抗干擾能力

USB 信號屬于模擬信號,所以在 CH340/CH341 等 USB 芯片內(nèi)部包含數(shù)字電路和一些模擬電路,另外,USB 芯片中還包含時鐘震蕩及 PLL 倍頻電路,電路的公共地端在芯片內(nèi)部已經(jīng)連接在一起并連接到芯片的 GND 引腳。

如果 USB 芯片有時工作不正常、或者 USB 數(shù)據(jù)傳輸隨機(jī)性失敗、或者抗干擾能力差,那么就應(yīng)該考慮 USB 芯片是否穩(wěn)定工作。影響 USB 芯片工作穩(wěn)定性的幾大因素及解決辦法如下:

1. 時鐘信號不穩(wěn)定

時鐘信號不穩(wěn)定通常是 PCB 布線中 GND 走線不佳。參考下圖,該圖適用于 USB 類芯片,圖中有 6個接地點(diǎn),分別是 A、B、C、D、E、F,設(shè)計電路及 PCB 時應(yīng)該盡量避免這 6 個 GND 點(diǎn)之間存在電壓差(主要是指數(shù)字電路中的高頻毛刺電壓,也就是數(shù)字噪聲)。

★ 盡量縮短這 6 個點(diǎn)之間的距離;

★ 類似模擬電路設(shè)計中的單點(diǎn)接地;

★ 大面積 GND 鋪銅及 GND 多點(diǎn)過孔 VIA 降低高頻信號阻抗。圖中最關(guān)鍵的是 E 點(diǎn)、F 點(diǎn)與 D 點(diǎn)之間不能存在高頻毛刺電壓差,可以用示波器探頭接 D 點(diǎn)測量時鐘輸入端 XI 引腳的 12MHz 時鐘波形是否有抖動。

2. 時鐘信號受干擾

★ PCB 設(shè)計時盡量不在晶體及震蕩電容附近走線,尤其是不要走繼電器、電動機(jī)等帶有瞬時沖擊電流的電源線和強(qiáng)信號線、時鐘信號線、頻率較高的開關(guān)信號線等;

★ 使晶振、外部電容與IC之間的信號線盡可能保持最短;

★ 在晶體及震蕩電容周邊布置 GND 鋪銅屏蔽干擾;

★ 將晶體外殼接地(任何需要晶體工作的電路都可以這樣設(shè)計);

★ 使用有源晶振等。

3. USB信號受干擾

★ USB 信號線 D+ 與 D- 盡量對稱平行布線,保證兩根差分線緊耦合,避免 90度走線,弧形或45度走線均可;

★ 在元件布局時,盡量使差分線路最短,布線優(yōu)先繪制差分線,一對差分線上盡量不要超過兩對過孔,且過孔需對稱放置;

★ 最好在兩側(cè)布置 GND 鋪銅,減少干擾,在空間允許情況下,其他信號網(wǎng)絡(luò)及地離差分線的間距至少 20mil,距離過近會對差分線阻抗產(chǎn)生影響;

★ 可以在 USB 信號線 D+ 和 D- 上串接共模電感以抑制EMI;

★ USB 外殼地串接一個 100K 到 1M 級的電阻到地,同時電阻上并聯(lián)一個0.01uF電容;

★ 使用符合 USB 規(guī)范的帶屏蔽層的傳輸線,不能使用普通排線或者非 USB 線纜。

除以上幾種原因與解決方法外,還可以通過使用屏蔽罩在復(fù)雜應(yīng)用環(huán)境中減小EMI干擾。

接入主機(jī)無反應(yīng)或者出現(xiàn)無法識別的USB設(shè)備

★ 首先需要檢查芯片供電是否正常,3.3V和5V供電注意事項參考上面說明;

★ 查看芯片是否為內(nèi)置晶振版本,若為外置晶振版本,用示波器測量晶振是否起振,晶振與旁路電容參數(shù)是否匹配;

★ 檢查電路原理圖設(shè)計是否正確無誤且滿足規(guī)范;

★ 檢查使用的線纜是否符合 USB 規(guī)范,線纜是否過長以及有無屏蔽層;

★ 檢查電路板是否存在焊接問題,導(dǎo)致局部電路短路;

★ 控制芯片焊接最高溫度與持續(xù)時間,務(wù)必控制低于 300 攝氏度且高溫持續(xù)時間低于 2 分鐘;

Windows 設(shè)備管理器出現(xiàn)感嘆號設(shè)備

設(shè)備管理器出現(xiàn)感嘆號設(shè)備說明硬件已經(jīng)被系統(tǒng)枚舉到了,但是驅(qū)動未安裝或者驅(qū)動不匹配,此時需要做以下操作:

★ 從官網(wǎng)上下載最新的芯片驅(qū)動,鏈接地址為:http://www.wch.cn/download/CH341SER_EXE.html,安裝時先點(diǎn)擊卸載將可能存在的老版本驅(qū)動卸載刪除,之后再點(diǎn)擊安裝新驅(qū)動;

★ 如果使用新驅(qū)動后問題仍然無法解決,那么查看系統(tǒng)驅(qū)動安裝日志查看具體報錯原因。日志系統(tǒng)路徑為:C:Windowsinfsetupapi.dev.log。打開日志,查找CH341 字樣可以看到失敗原因,之后再進(jìn)行對應(yīng)問題的解決;

不同系統(tǒng)下面如何使用和判斷設(shè)備是否正常工作

在不同的系統(tǒng)環(huán)境下要分別使用相應(yīng)的芯片驅(qū)動,所有驅(qū)動可以從官網(wǎng)搜索下載到

★ Linux 系統(tǒng)下面使用首先需要確保系統(tǒng)中沒有老驅(qū)動存在,系統(tǒng)的默認(rèn)驅(qū)動目錄為:/lib/modules/$(uname -r)/kernel/drivers,老驅(qū)動完整路徑為 /lib/modules/$(uname -r)/kernel/drivers/usb/serial/ch341.ko。如果存在該文件,那么需要手動刪除。之后編譯下載的 Linux 驅(qū)動源碼,將生成的新驅(qū)動文件 ch34x.ko 拷貝到原驅(qū)動路徑下,然后執(zhí)行 depmod 重啟即可。插入設(shè)備后,可以通過 dmesg 查看設(shè)備是否枚舉成功,以及驅(qū)動加載是否正常,成功會在 /dev 路徑下產(chǎn)生 ttyUSB 開頭的設(shè)備文件。

★ Android 系統(tǒng)下直接使用免驅(qū)APP就可以了,官網(wǎng)提供了芯片操作庫以及 demo 工程源碼方便二次開發(fā),設(shè)備連接 Android 設(shè)備時,要使用 OTG 線并確保 Android 系統(tǒng)的 host 權(quán)限已經(jīng)打開;

★ MacOS 下使用時首先要從官網(wǎng)下載最新芯片驅(qū)動,在系統(tǒng)上雙擊安裝。當(dāng)設(shè)備插入后,如果在系統(tǒng) /dev 路徑下產(chǎn)生 /dev/tty.wchusbserial 關(guān)鍵字說明設(shè)備正常工作;

Windows 系統(tǒng)下如何確定 COM 口為 CH340/CH341 設(shè)備

★ 使用軟件查詢法,依次打開系統(tǒng)的 COM 口,并以 300bps 向 COM 口發(fā)送特殊字符串 "$CH341Ser?",如果回復(fù)字符 'W'那么表明為 CH340/CH341 設(shè)備;

★ 使用CH341PT.DLL動態(tài)庫,應(yīng)用程序可以直接調(diào)用DLL中相應(yīng)的API識別 CH340/CH341 串口,識別速度快,效率高。注意,CH341PT.DLL在INF中定義為可選安裝,默認(rèn)是安裝的;

串口通訊亂碼

如果 CH340/CH341 在與其他器件進(jìn)行串口通訊時出現(xiàn)亂碼,首先需要確保雙方串口設(shè)置完全相同,包括波特率、數(shù)據(jù)位、停止位、校驗位等。其次需要明確雙方收發(fā)誤差率允許范圍以及實(shí)際通訊時波特率誤差。CH340/CH341 串口接收信號的允許波特率誤差不小于 2%,CH340G/CH340T/CH340R 串口發(fā)送信號的波特率誤差小于 0.3%,CH340C/CH340E/CH340B 小于 1%,明確范圍后測量實(shí)際通訊波特率誤差是否滿足此條件。另外需要注意,如果實(shí)際通訊模型是 TTL 轉(zhuǎn) RS232 通訊,那么需要測量最終通訊接口誤差,因為信號經(jīng)過電平轉(zhuǎn)換芯片后誤差會放大。

審核編輯黃宇

-

芯片

+關(guān)注

關(guān)注

459文章

52128瀏覽量

435677 -

usb

+關(guān)注

關(guān)注

60文章

8136瀏覽量

270571 -

串口

+關(guān)注

關(guān)注

14文章

1582瀏覽量

78565

發(fā)布評論請先 登錄

國產(chǎn)芯片解析:無線充電管理芯片CH246跟CH247對比詳細(xì)

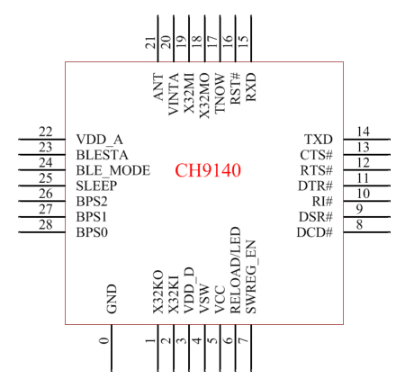

沁恒微藍(lán)牙轉(zhuǎn)接芯片系列解析:CH9140/CH9141/CH9142/CH9143

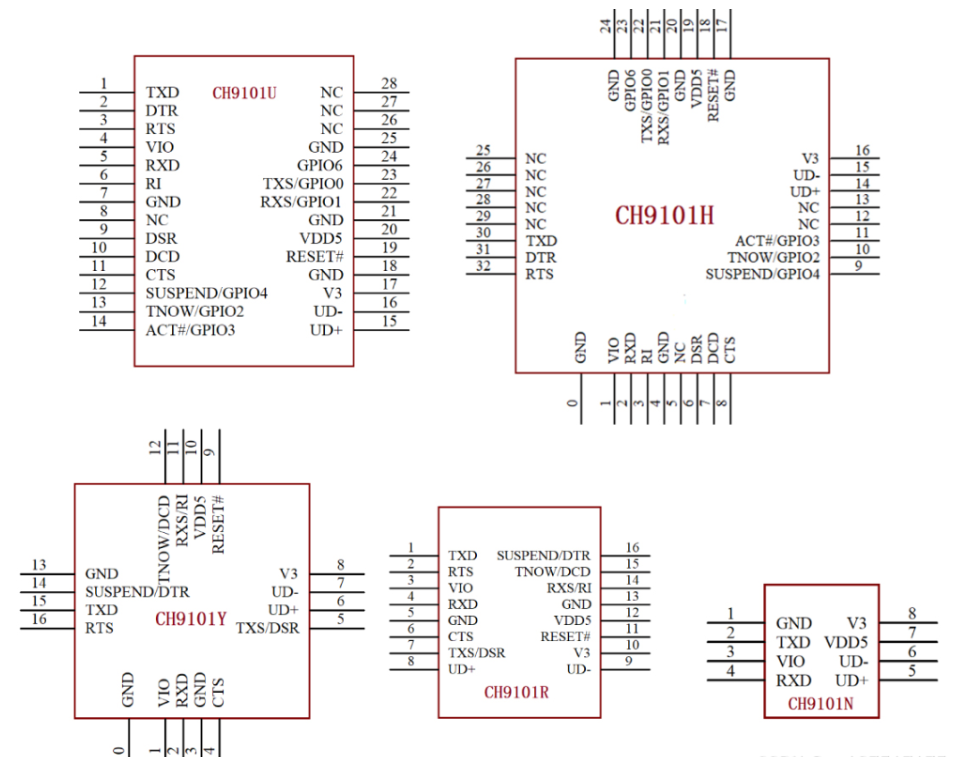

USB轉(zhuǎn)串口芯片CH9101介紹

USB轉(zhuǎn)串口芯片CH340與CH341使用問題匯總

USB轉(zhuǎn)串口芯片CH340與CH341使用問題匯總

評論