1.前言

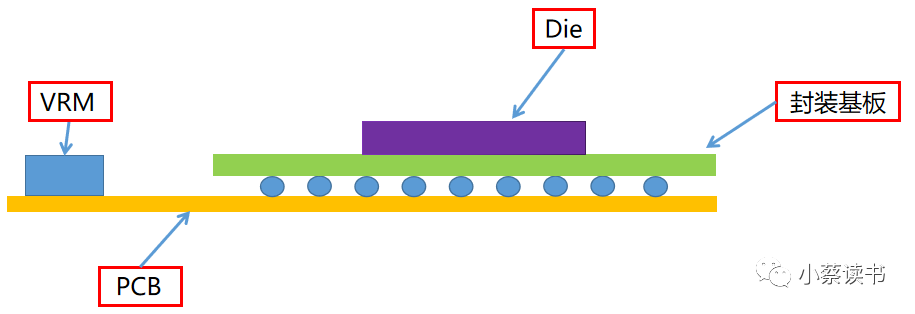

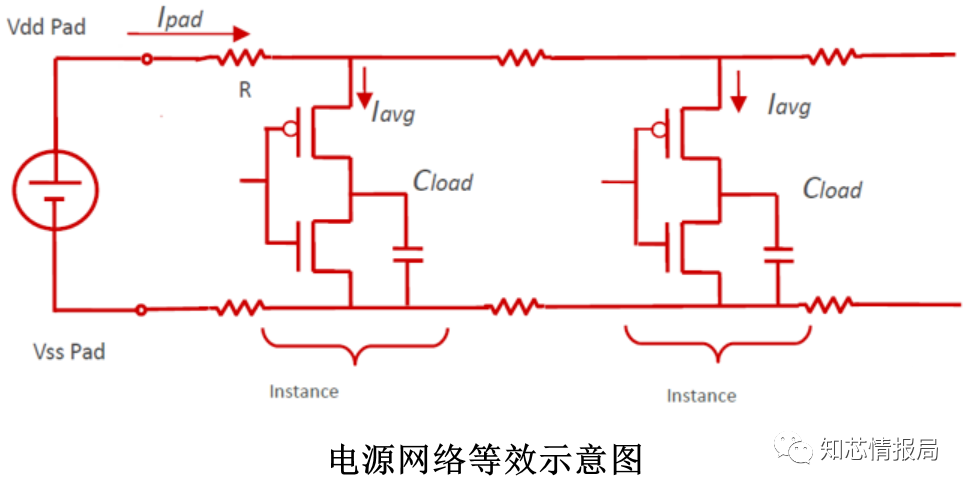

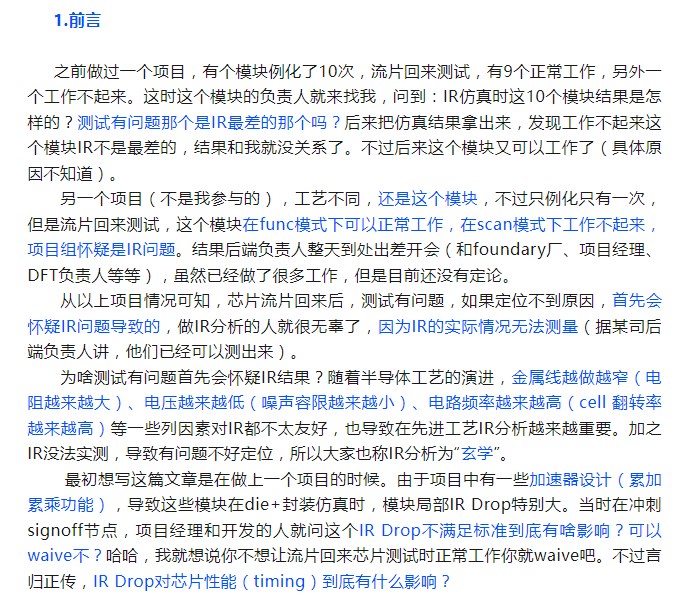

大部分從事后端設(shè)計(jì)的同行應(yīng)該沒(méi)有接觸過(guò)帶封裝的IR Drop分析(模塊級(jí)別的IR分析不需要考慮封裝),一般只有PA工程師、后端項(xiàng)目經(jīng)理、封裝同事等才會(huì)接觸這一部分內(nèi)容。為啥要聊這一塊呢?首先看下完整的供電路徑(如下圖):板級(jí)電源模塊(VRM:Voltage Regulator Module)的電流經(jīng)過(guò)PCB上的引線到達(dá)PCB的電源平面,通過(guò)Bump到達(dá)封裝的管腳,再通過(guò)封裝基板到芯片的PAD,再通過(guò)芯片內(nèi)的電源網(wǎng)絡(luò)到達(dá)晶體管電源的端口,地的回路和電源類(lèi)似,電源和地的電流路徑形成了完整的供電路徑。

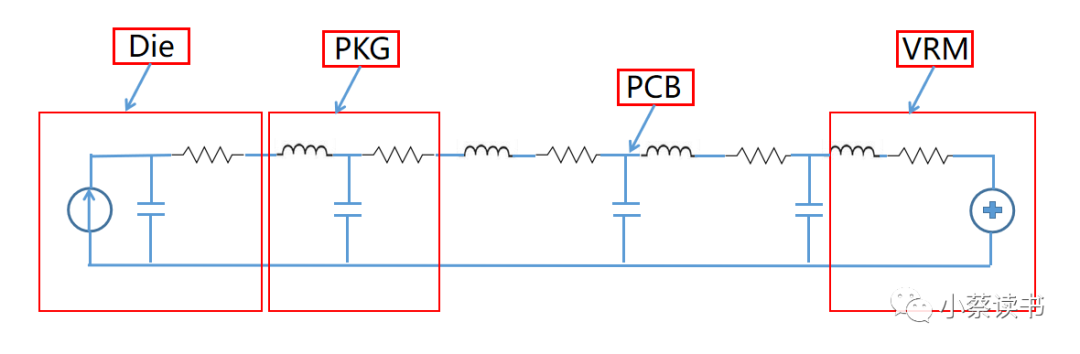

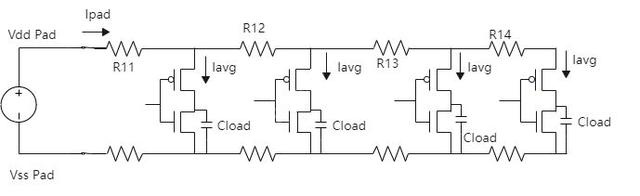

上圖的供電路徑等效電路圖如下圖所示,可見(jiàn)在VRM對(duì)晶體管供電的過(guò)程中,由于每一段供電路徑都有等效的電阻、電感、電容,所以每一段也都有相應(yīng)的電壓降。

當(dāng)整體考慮電源分布時(shí),實(shí)際上涉及芯片上和芯片外的問(wèn)題,這些問(wèn)題從直流到直流轉(zhuǎn)換器開(kāi)始,包括PCB,電源分布(power plane),封裝、插槽、電源管腳或焊接塊等,最后是與門(mén)的連接。正確的電源網(wǎng)格設(shè)計(jì)需要系統(tǒng)設(shè)計(jì)工程師、熱學(xué)設(shè)計(jì)師、系統(tǒng)架構(gòu)設(shè)計(jì)師、電路板設(shè)計(jì)師和芯片設(shè)計(jì)者的共同工作。

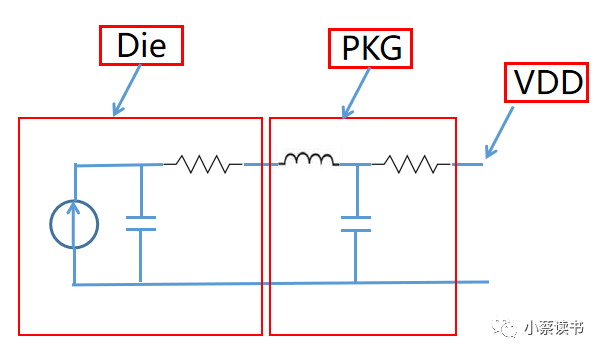

這個(gè)問(wèn)題需要整體優(yōu)化而不僅是局部的芯片級(jí)優(yōu)化。 后端工程師只需要分析Die+PKG部分(但是應(yīng)該記住這僅是整個(gè)設(shè)計(jì)問(wèn)題的一部分),整體電源網(wǎng)絡(luò)仿真分析應(yīng)由封裝或者系統(tǒng)的同事完成,因此本文討論的范圍限于Die+PKG部分,如下圖:

2.封裝上的電壓降

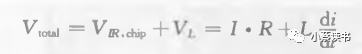

在納米尺寸設(shè)計(jì)中,除了計(jì)算芯片的電壓降外,還要考慮與封裝相關(guān)的電壓降。總電壓降的大小Vtotal 由電源凸點(diǎn)到邏輯門(mén)單元之間等效電阻R及封裝導(dǎo)線的電感值L決定,并由歐姆定律決定Vir,chip = I*R,I為通路電流,Vl = L*di/dt,則Vtotal值如下所示。

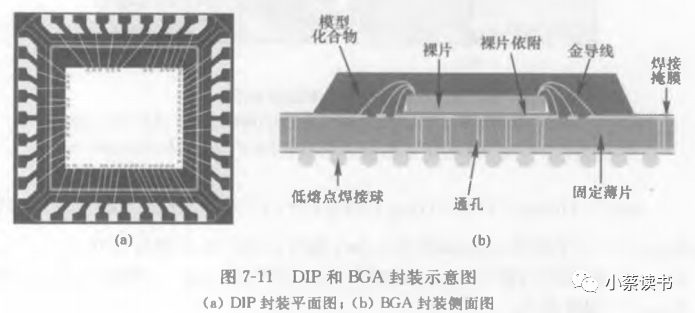

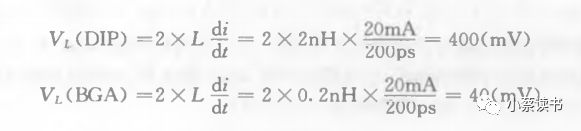

封裝電感對(duì)電壓降的影響,如下圖所示的兩種封裝形式,其中圖(a)為DIP(dual in-line)封裝,圖(b)為BGA(ball grid array)封裝,前者的封裝電感為1-2nH,而后者的封裝電感為0.1-0.2nH.

假設(shè)20mA的電流在200ps內(nèi)通過(guò)電源網(wǎng)絡(luò)給內(nèi)部節(jié)點(diǎn)供電時(shí),其消耗在DIP和BGA封裝導(dǎo)線上的電壓降和地彈的總值(作用于兩條線路)分別計(jì)算得400mV和40mV:

由此可見(jiàn),隨著工藝的發(fā)展,core供電電壓在下降,從0.9V(65nm) 0.8V(16nm)0.75V(7nm),封裝導(dǎo)線所產(chǎn)生的電壓降變得尤其突出,需要通過(guò)封裝形式的改進(jìn)減小電壓降的值。在數(shù)模混合芯片中尤其要注意,數(shù)字core邏輯部分不管是die內(nèi)電源走線還是PKG上的走線,都要保證足夠強(qiáng)壯,不能認(rèn)為數(shù)字邏輯部分instance比較少只要連起來(lái)就可以了。

3. CPA(Chip Package Analysis)

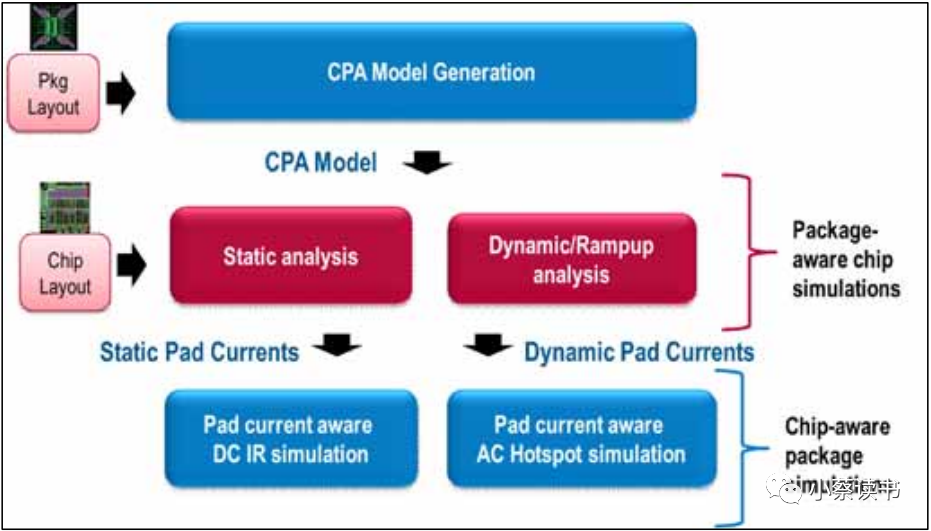

如下圖所示,CPA model是Pkg Layout(封裝基板設(shè)計(jì))通過(guò)工具提取出來(lái)的一個(gè)模型,主要包括封裝基板中的RLC參數(shù)。CPA可以提供每個(gè)bump的寄生參數(shù),可以用來(lái)做chip+package的協(xié)同仿真。

chip+package可以做static分析,仿真可以得到每個(gè)pad的電流,可以為pad的過(guò)流能力是否超標(biāo)做參考,這種方式屬于直流仿真;當(dāng)做dynamic仿真時(shí),屬于交流仿真。

4.問(wèn)題

1.在抽取CPA model時(shí),根據(jù)pin group不同,可以分為L(zhǎng)umped Grouping/Group by Each Pin/Group by X-Y Grid三種方式,這三種方式IR結(jié)果相差比較大,每個(gè)公司根據(jù)自己的經(jīng)驗(yàn)選取方式不統(tǒng)一。Lumped Grouping所有pin一起抽,IR最小;GroupbyEachPin每個(gè)pin單獨(dú)抽,IR最大,但是工具計(jì)算量大,run time長(zhǎng);Group by X-Y Grid 介于兩者之間。

2.帶CPA和不帶CPA仿真,結(jié)果相差大嗎?Static IR相差不大,Dynamic IR相差較大(尤其翻轉(zhuǎn)率高的地方),為啥呢?自己思考下.

3.封裝上的走線不均勻,連接弱的地方IR會(huì)比較大。另外GUI界面可以看到每個(gè)bump的電阻和電感。

審核編輯:劉清

-

PCB板

+關(guān)注

關(guān)注

27文章

1465瀏覽量

52985 -

直流轉(zhuǎn)換器

+關(guān)注

關(guān)注

0文章

278瀏覽量

21437 -

PAD

+關(guān)注

關(guān)注

1文章

101瀏覽量

31017 -

晶體管

+關(guān)注

關(guān)注

77文章

9975瀏覽量

140564 -

VRM

+關(guān)注

關(guān)注

0文章

31瀏覽量

12853

原文標(biāo)題:IR Drop與封裝

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

IR推出IR3588 ChiL數(shù)字控制IC及IR3552、IR3546

談?wù)勑酒O(shè)計(jì)中的IR-drop

什么是DC IR Drop?DC IR Drop仿真有何意義?

#硬聲創(chuàng)作季 Allegro Tips IR Drop 整合分析

quick drop

mos管漏極出現(xiàn)drop現(xiàn)象

什么是ADM (Add/Drop Multiplexer)

IR推出采用PQFN封裝技術(shù)的MOSFET硅器件

IR推出新款PQFN封裝功率MOSFET PQFN2x2

IR Drop對(duì)芯片性能及功能的影響

Sigrity PowerDC是如何計(jì)算IR Drop Margin?

IR Drop對(duì)芯片性能及功能的影響

IR Drop與封裝(一)

IR Drop與封裝(二)

IR Drop與封裝分析

IR Drop與封裝分析

評(píng)論