作者:

Coventor(泛林集團旗下公司)半導體工藝與整合(SPI)高級工程師王青鵬博士

摘要:虛擬DOE能夠降低硅晶圓測試成本,并成功降低DED鎢填充工藝中的空隙體積

實驗設計(DOE)是半導體工程研發中一個強大的概念,它是研究實驗變量敏感性及其對器件性能影響的利器。如果DOE經過精心設計,工程師就可以使用有限的實驗晶圓及試驗成本實現半導體器件的目標性能。然而,在半導體設計和制造領域,DOE(或實驗)空間通常并未得到充分探索。相反,人們經常使用非常傳統的試錯方案來挖掘有限的實驗空間。這是因為在半導體制造工藝中存在著太多變量,如果要充分探索所有變量的可能情況,需要極大的晶圓數量和試驗成本。在這種情況下,虛擬工藝模型和虛擬DOE可謂是探索巨大潛在解空間、加速工藝發展的同時減少硅實驗成本的重要工具。本文將說明我們在高深寬比通孔鎢填充工藝中,利用虛擬DOE實現了對空隙的有效控制和消除。示例中,我們使用原位沉積-刻蝕-沉積 (DED) 法進行鎢填充工藝。

基于硅的掃描電鏡圖像和每個填充步驟的基本行為,使用SEMulator3D?虛擬工藝建模,重建了通孔鎢填充工藝。

建模工藝包括:

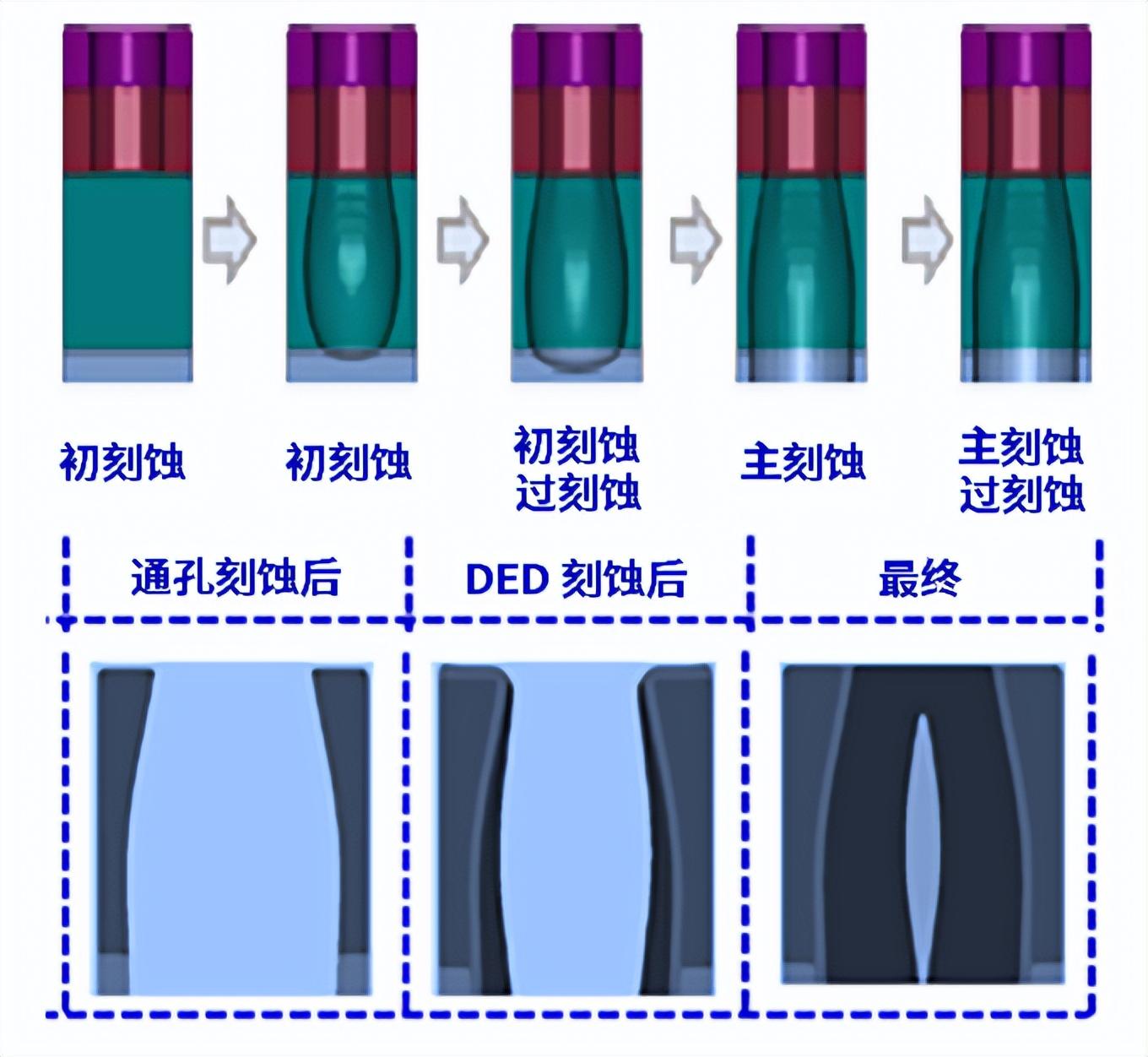

1. 前置溝槽刻蝕(初刻蝕、初刻蝕過刻蝕、主刻蝕、過刻蝕)

2. DED工藝(第一次沉積、第一次深度相關刻蝕、第二次沉積工藝)

3. 空隙定位和空隙體積的虛擬測量

為了匹配實際的硅剖面,工藝模型中的每個步驟都經過校準。

使用SEMulator3D生成的模擬3D輸出結構與硅的圖像進行對比,它們具有相似的空隙位置和空隙體積(見圖1)。圖1顯示了SEMulator3D和實際硅晶圓中的相應工藝步驟。使用新校準的模型,完成了3次虛擬DOE和500多次模擬運行,以了解不同工藝變量對空隙體積和彎曲關鍵尺寸的影響。

圖1:DED工藝校準

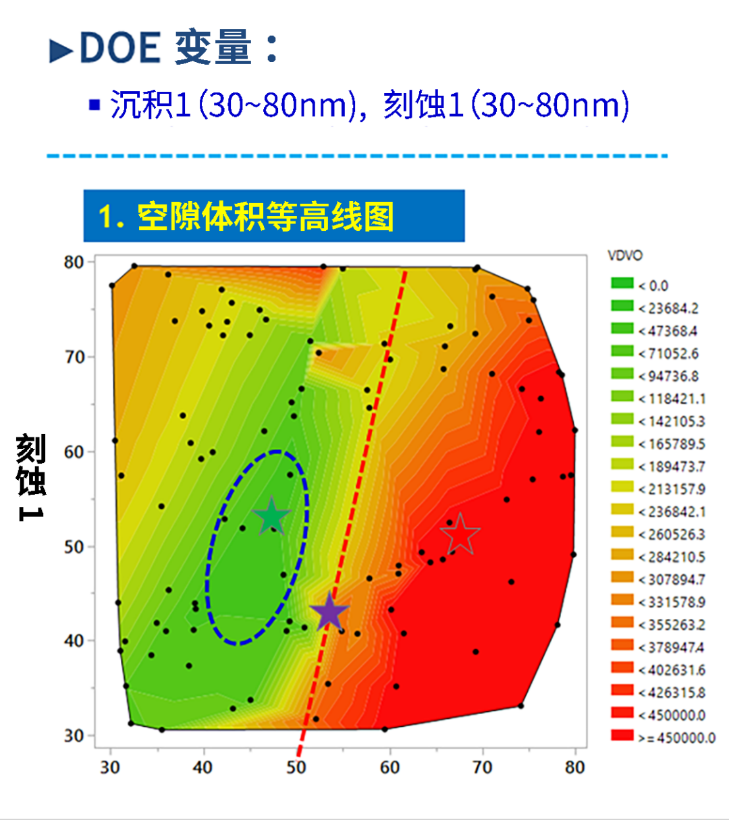

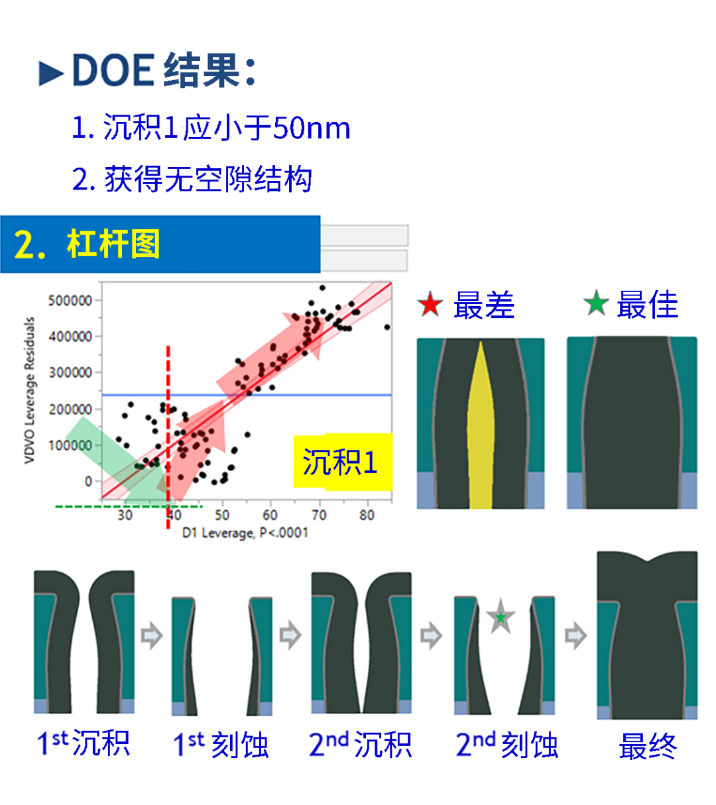

l第一次DOE

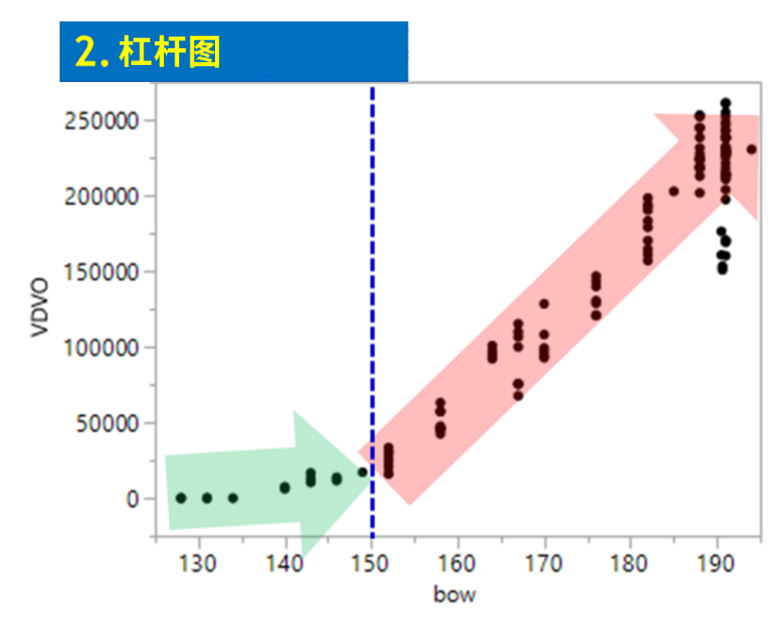

在第一次DOE中,我們使用DED工藝步驟進行了沉積和刻蝕量的實驗。在我們的測試條件下,空隙體積可以減小但永遠不能化零,并且沉積層不應超過頂部關鍵尺寸的45%(見圖 2)。

圖2:DED等高線圖、杠桿圖、DOE1的輸出結構

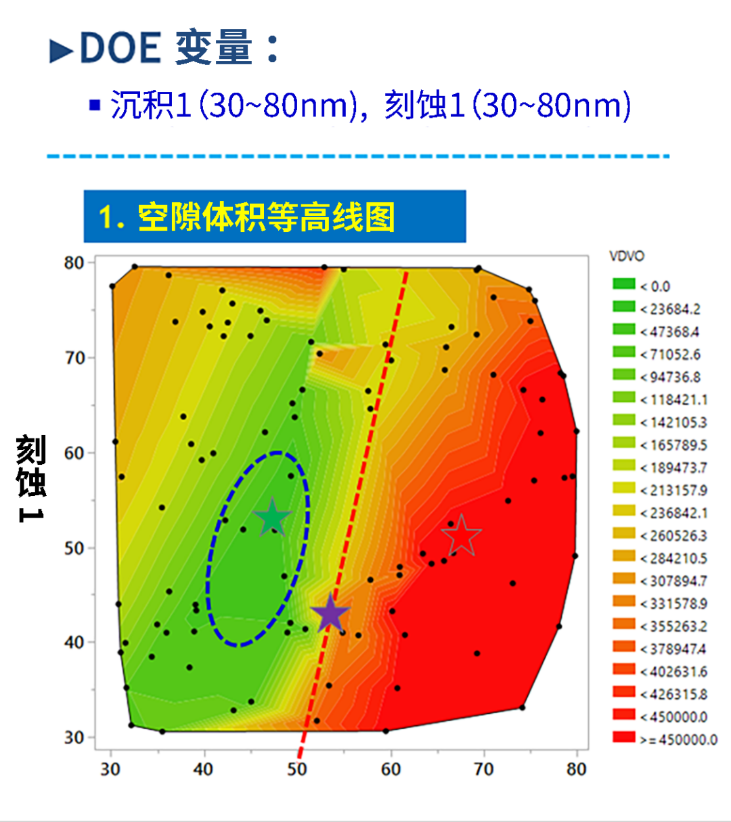

l第二次DOE

在第二次DOE中,我們給校準模型(DEDED工藝流程的順序)加入了新的沉積/刻蝕工藝步驟。這些新的沉積和刻蝕步驟被設置了與第一次 DOE相同的沉積和刻蝕范圍(沉積1和刻蝕1)。沉積1(D1)/刻蝕1(E1)實驗表明,在D1和E1值分別為47nm和52nm時可以獲得無空隙結構(見圖 3)。需要注意,與第一次DOE相比,DEDED工藝流程中加入了新的沉積和刻蝕步驟。與之前使用的簡單DED工藝相比,這意味著工藝時間的增加和生產量的降低。

圖3:DEDED等高線圖、杠桿圖、DOE2的輸出結構

l第三次DOE

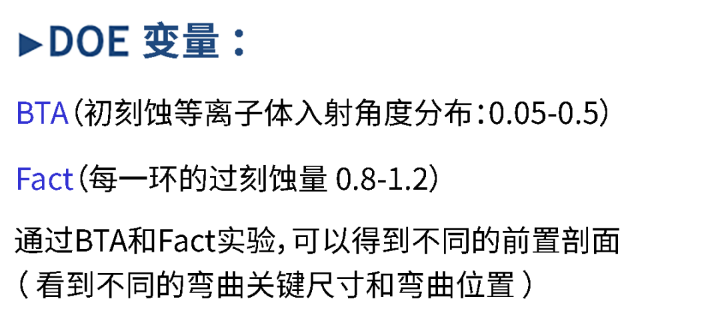

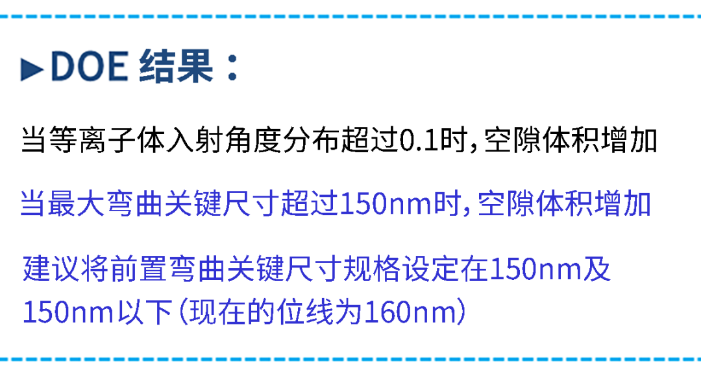

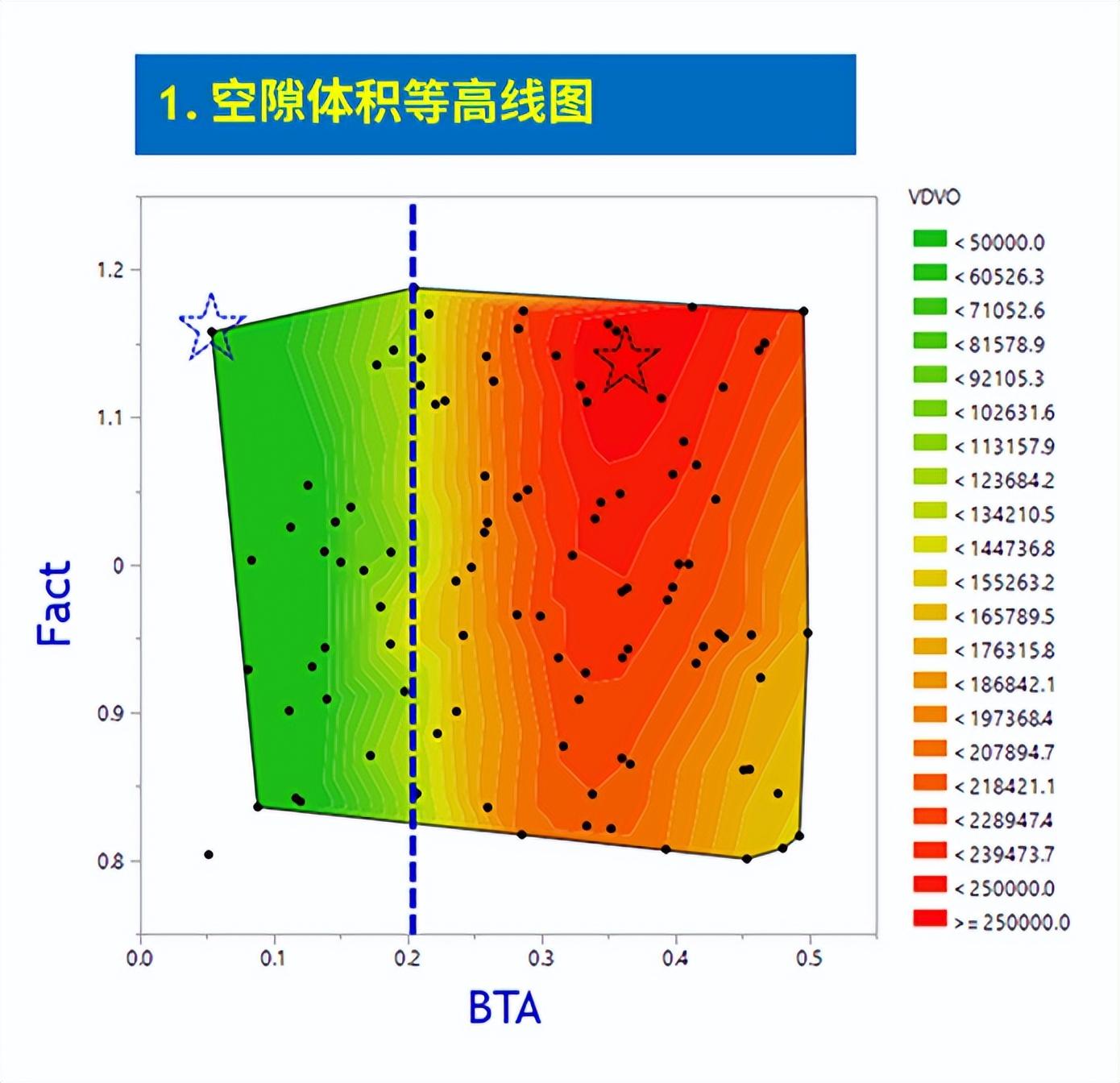

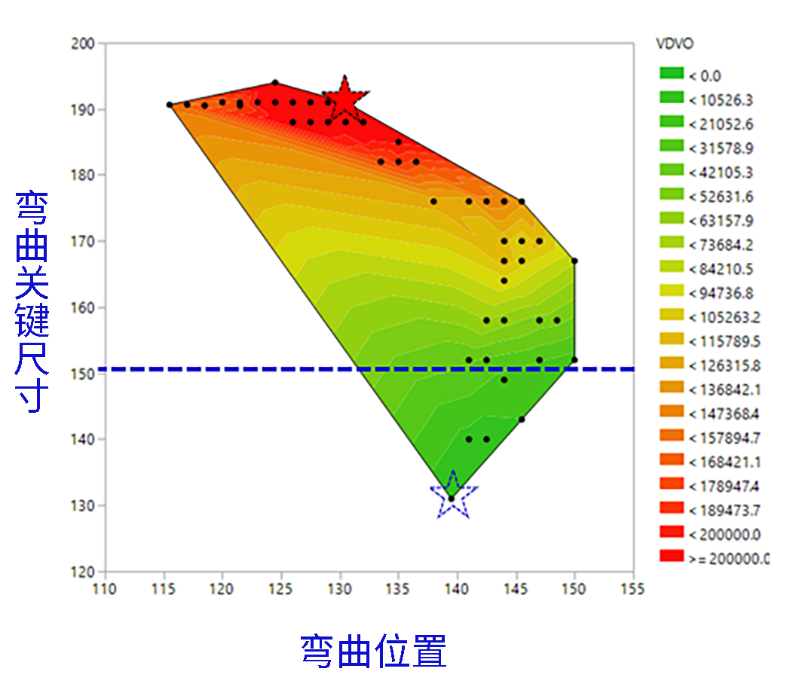

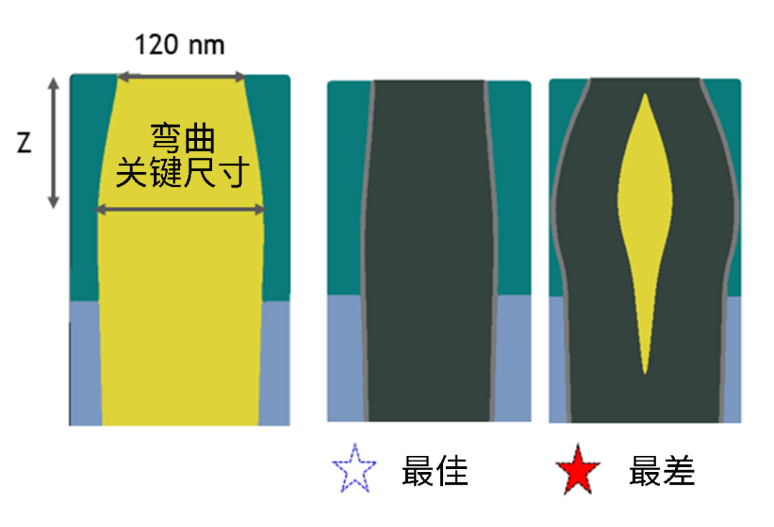

在第三次DOE中,我們通過調整BT(初刻蝕)刻蝕行為參數進行了一項前置通孔剖面的實驗。在BT刻蝕實驗中,使用SEMulator3D的可視性刻蝕功能進行了工藝建模。我們在虛擬實驗中修改的是等離子體入射角度分布(BTA)和過刻蝕因子(Fact)這兩個輸入參數。完成虛擬通孔刻蝕后,使用虛擬測量來估測每次模擬運行的最大彎曲關鍵尺寸和位置。這個方法使用BTA(初刻蝕等離子體入射角度分布)和Fact(過刻蝕量)實驗實驗生成了虛擬結構,同時測量和繪制了彎曲關鍵尺寸和位置。第三次DOE的結果表明,當彎曲關鍵尺寸足夠小時,可以獲得無空隙的結構;當彎曲關鍵尺寸大于150nm時,空隙體積將急劇增加(見圖4)。因此,可以利用最佳的第三次DOE結果來選擇我們的制造參數并進行硅驗證。

圖4:前置通孔剖面實驗等高線圖、杠桿圖、DOE3的輸出結構

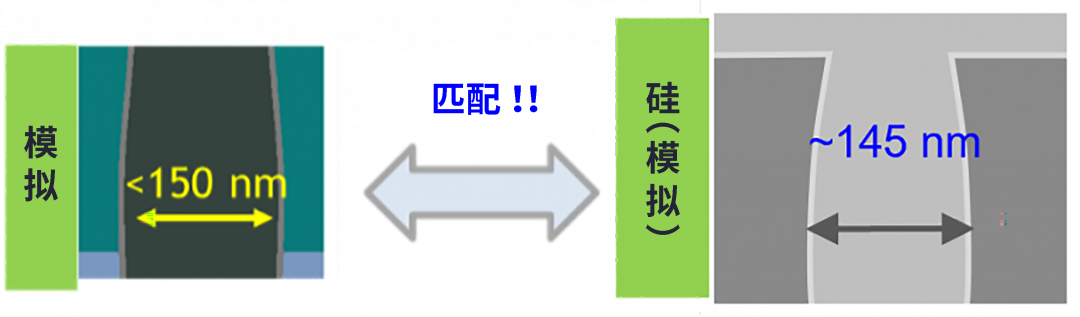

通過將前置通孔彎曲規格設置在150nm以下(圖5中的145nm),我們在最終的硅工藝中獲得了無空隙結構。此次,硅結果與模型預測相符,空隙問題得到解決。

圖5:當彎曲關鍵尺寸小于150nm時,SEMulator3D預測的結果與實際的硅結果

此次演示中,我們進行了SEMulator3D建模和虛擬DOE來優化DED鎢填充,并生成無空隙結構,3次DOE都得到了空隙減小或無空隙的結構。我們用DOE3的結果進行了硅驗證,并證明我們解決了空隙問題。硅結果與模型預測相匹配,且所用時間比試錯驗證可能會花費的短很多。該實驗表明,虛擬DOE在加速工藝發展并降低硅晶圓測試成本的同時,也能成功降低DED鎢填充工藝中的空隙體積。

審核編輯黃宇

-

半導體

+關注

關注

335文章

28563瀏覽量

232233 -

虛擬實驗

+關注

關注

0文章

14瀏覽量

7957 -

DOE

+關注

關注

0文章

38瀏覽量

13181

發布評論請先 登錄

半導體制冷機chiller在半導體工藝制程中的高精度溫控應用解析

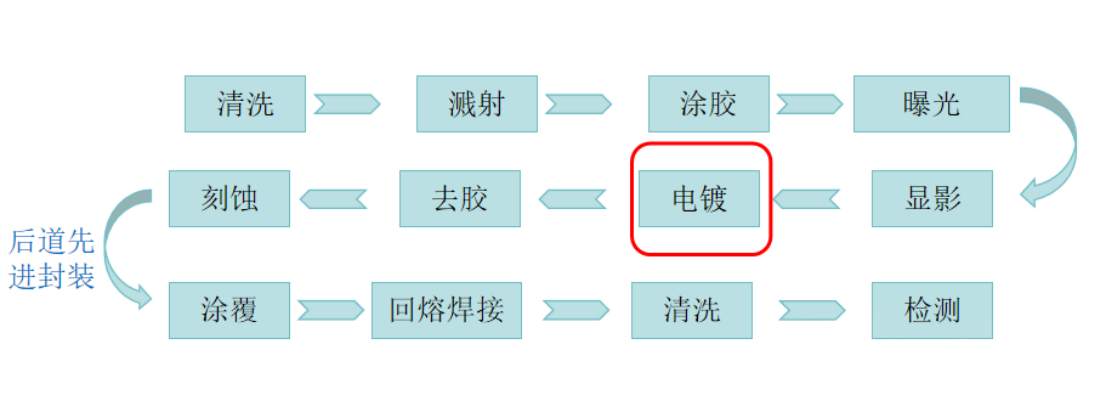

揭秘半導體電鍍工藝

提供半導體工藝可靠性測試-WLR晶圓可靠性測試

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

芯和半導體將參加重慶半導體制造與先進封測產業發展論壇

半導體封裝革新之路:互連工藝的升級與變革

半導體固晶工藝深度解析

倒裝封裝(Flip Chip)工藝:半導體封裝的璀璨明星!

長江存儲正加速轉向國產半導體設備

走進半導體重點實驗室,感受科技前沿的震撼

使用虛擬實驗設計加速半導體工藝發展

使用虛擬實驗設計加速半導體工藝發展

評論