第1節(jié) 什么是 FPGA

FPGA 的全稱為 Field-Programmable Gate Array ,即現(xiàn)場可編程門陣列。FPGA 是在 PAL、 GAL、 CPLD 等可編程器件的基礎(chǔ)上進一步發(fā)展的產(chǎn)物, 是作為專用集成電路( ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。簡而言之, FPGA 就是一個可以通過編程來改變內(nèi)部結(jié)構(gòu)的芯片 。

FPGA 功能實現(xiàn) :需要通過編程即設(shè)計硬件描述語言,經(jīng)過 EDA 工具編譯、綜合、布局布線成后轉(zhuǎn)換為可燒錄的文件,

最終加載到 FPGA 器件中去,改變 FPGA 內(nèi)部的連線,最終完成所實現(xiàn)的功能。

FPGA 性能對比 :FPGA 相比于單片機、 CPU 等集成電路芯片擁有效率更高、功耗更低的特點,但是易于開發(fā)程度遠(yuǎn)遠(yuǎn)不如單片機、 CPU;在數(shù)字芯片設(shè)計領(lǐng)域, FPGA 雖然相比 ASIC 具有更短的開發(fā)周期與開發(fā)難度, 但是其存在著成本過高、性能較差并且在資源的利用率上遠(yuǎn)不及 ASIC 等問題,不能真正的替代 ASIC。

第2節(jié) FPGA 的基本結(jié)構(gòu)

FPGA 可編程的特性決定了其實現(xiàn)數(shù)字邏輯的結(jié)構(gòu)不能像專用 ASIC 那樣通過固定的邏輯門電路來完成,而只能采用一種可以重復(fù)配置的結(jié)構(gòu)來實現(xiàn), 而查找表(LUT)可以很好地滿足這一要求, 目前主流的 FPGA 芯片仍是基于 SRAM 工藝的查找表結(jié)構(gòu) 。

FPGA 芯片參數(shù)指標(biāo) :包含可編程邏輯模塊的數(shù)量、固定功能邏輯模塊(如乘法器)的數(shù)目及存儲器資源(如嵌入式 RAM)的大小。

在 最底層的可配置邏輯模塊 (如片上的邏輯單元) 上,存在著基本的兩種部件:觸發(fā)器和查找表( LUT) , 而觸發(fā)器和查找表的組合方式不同,是各個 FPGA 家族之間區(qū)別的重要依據(jù), 并且查找表本身的結(jié)構(gòu)也可能各不相同( 有 4 輸入或 6 輸入或其他)。

查找表( Look-Up-Table)簡稱為 LUT, 其本質(zhì)上就是一個 RAM。目前 FPGA 內(nèi)部中多使用 4輸入的 LUT,每一個 LUT 可以看成一個有 4 位地址線的 RAM。

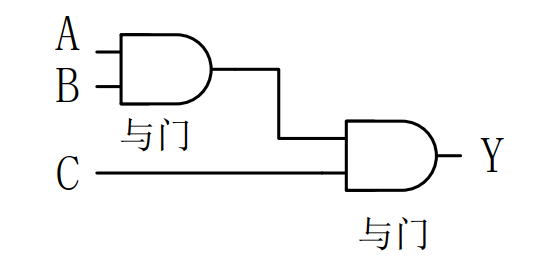

當(dāng)用戶在 EDA 工具上通過原理圖或 硬件描述語言設(shè)計了一個邏輯電路以后, FPGA 開發(fā)軟件會自動計算邏輯電路的所有可能結(jié)果,并把真值表(即結(jié)果)事先寫入 RAM 中。這樣,每輸入一個信號進行邏輯運算就等于輸入一個地址進行查找表操作, 通過地址找到對應(yīng)的 RAM 中的結(jié)果, 最后將其輸出。以實現(xiàn)數(shù)字邏輯 Y=A&B&C 的功能為例。如果是在專用 ASIC 中,為了實現(xiàn)該邏輯,邏輯門都已經(jīng)事先確定好, Y 的輸出值為兩個邏輯與運算后的結(jié)果,其基本的實現(xiàn)結(jié)構(gòu)如下圖所示:

與門示意圖

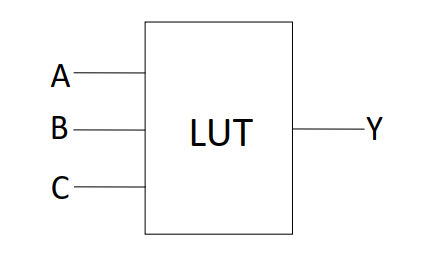

對Y=A&B&C 的 利用FPGA 實現(xiàn)基本結(jié)構(gòu) :

示意圖

第3節(jié) 更為復(fù)雜的 FPGA 架構(gòu)

隨著技術(shù)的發(fā)展和工藝節(jié)點的進步, FPGA 的容量和性能在不斷提高的同時, 其功耗卻不斷的優(yōu)化減少。2006 年以前四輸入查找表一直被廣泛使用, 在一些 高端器件可能會用上六輸入、八輸入或更多輸入端口的查找表 。而一個多輸入的查找表又可以分解成較小輸入的查找表, 即能夠分裂成許多更小的功能。例如一個八輸入的查找表可以分解成兩個四輸入的查找表或分解成一個三輸入加一個五輸入的查找表。 在實際的高端器件中,這種可編程構(gòu)造可以描述相當(dāng)于百萬級(有時甚至千萬級)的原始邏輯門 。

在 FPGA 內(nèi)部,利用 FPGA 的可編程性在芯片內(nèi)部構(gòu)造實現(xiàn)了一個計數(shù)器邏輯,有著“軟內(nèi)核”與“硬內(nèi)核”之分。

軟內(nèi)核(軟功能) :在構(gòu)造計數(shù)器邏輯過程中使用到的功能便可以被稱為軟功能。

硬內(nèi)核(硬功能) :功能若是直接利用芯片實現(xiàn)的,則是利用了芯片內(nèi)部的硬功能。

軟內(nèi)核與硬內(nèi)核之間優(yōu)勢互補,軟內(nèi)核的優(yōu)勢在于可以在利用芯片資源的基礎(chǔ)上利用編程設(shè)計讓其完成需要實現(xiàn)的任何功能(注意是數(shù)字功能,不包括模擬功能)。而硬內(nèi)核由于是實現(xiàn)固定功能的器件,因此其優(yōu)勢在于資源利用率高且功耗較低, 占用硅片的面積也較小, 并具有較高的性能。最重要的區(qū)別在于:與軟內(nèi)核相比硬內(nèi)核可用于實現(xiàn)模擬功能, 例如鎖相環(huán)的倍頻功能,這個功能需要在模擬電路下實現(xiàn),所以這一部分是在 FPGA 內(nèi)部用硬件來實現(xiàn)的 。

第4節(jié) 帶嵌入式處理器的 FPGA

利用 FPGA 的可編程構(gòu)造實現(xiàn)的事情之一即為使用其中的一部分?jǐn)?shù)字邏輯資源制作一個或多個軟處理器內(nèi)核, 當(dāng)然, 也可以實現(xiàn)不同規(guī)模的處理器。

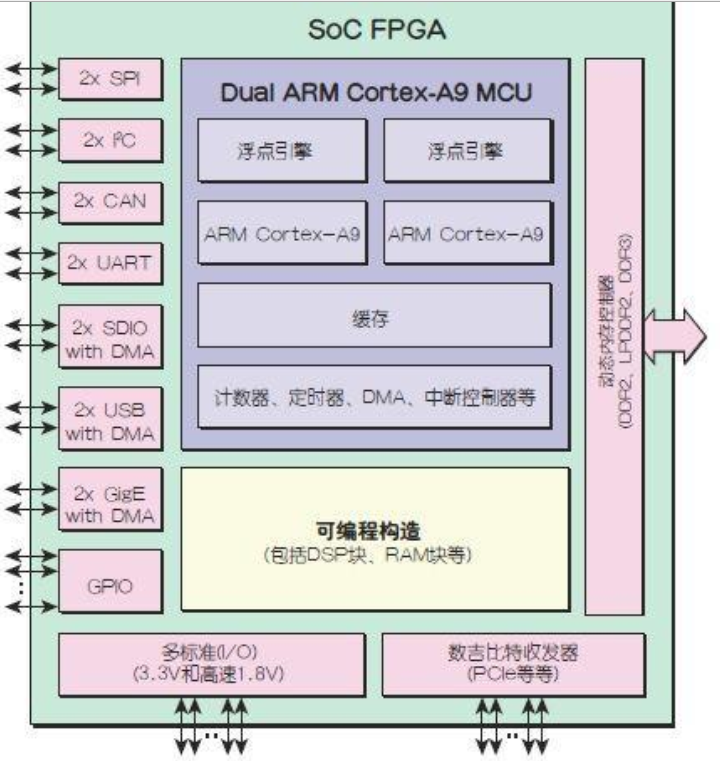

image-20211026193942002

這個芯片是一種新的SoC(System on Chip,系統(tǒng)級芯片) FPGA,完全以硬內(nèi)核方式實現(xiàn)的雙路 ARM Cortex-A9 微控制器子系統(tǒng)(運行時鐘高達 1GHz,包含浮點引擎,片上緩存,計數(shù)器,定時器等)以及種類廣泛的硬內(nèi)核接口功能( SPI, I2C, CAN等),還有一個硬內(nèi)核的動態(tài)內(nèi)存控制器,所有這些組件都 利用大量傳統(tǒng)的可編程構(gòu)造和大量的通用輸入輸出( GPIO)引腳進行了性能增強 。

第5節(jié) 數(shù)據(jù)存儲以及配置方式

在 FPGA 內(nèi)部存在著存儲單元片內(nèi) RAM 塊,數(shù)據(jù)是存放在 RAM 中并由其來設(shè)置工作狀態(tài)的,若想要 FPGA 進行工作,就需要對片內(nèi) RAM 進行編程 。而如果外部有大量數(shù)據(jù)交互時,就要通過增加外設(shè)來對數(shù)據(jù)進行暫時性的存儲,如 SDRAM 存儲器或者 DDR3 存儲器,暫存在外設(shè)中的數(shù)據(jù)最終也是要通過 FPGA 內(nèi)部的 RAM 進行存儲與處理。當(dāng)在 EDA 工具上將程序設(shè)計完成之后,便需要將軟件上的程序燒錄進 FPGA 內(nèi)部。通過不同的配置模式, FPGA 便會有不同的編程方式。

常用的幾種配置模式 :

- 并行模式 :通過并行 PROM(Programmable read-only memory,可編程只讀存儲器)、 Flash (Macromedia Flash。多媒體軟件平臺)配置 FPGA;

- 主從模式 :使用一片 PROM 配置多片 FPGA;

- 串行模式 :串行 PROM 配置 FPGA;

- 外設(shè)模式 :將 FPGA 作為微處理器的外設(shè),由微處理器對其編程。

目前, 主流的 FPGA 都是基于 SRAM (Static Random-Access Memory,靜態(tài)隨機存取存儲器)工藝的, 在 大部分的 FPGA 開發(fā)板上,使用的都是串行配置模式 。由于 SRAM 掉電就會丟失內(nèi)部數(shù)據(jù) ,因此往 往都會外接一個能夠掉電保存數(shù)據(jù)的片外存儲器以保存程序 。這樣一來, 上電時 FPGA 便將外部存儲器中的數(shù)據(jù)讀入片內(nèi) RAM 以完成配置, 對 FPGA 編程完成后便進入工作狀態(tài);掉電后 FPGA 內(nèi)部 SRAM 中存儲的數(shù)據(jù)丟失,邏輯清零。以這種方式配置 FPGA 不僅能反復(fù)使用,還無需重復(fù)的手動配置。完成一次主動配置之后每次上電便會自動的實現(xiàn) FPGA 的內(nèi)部編程。

FPGA在芯片制造大廠會有比較多的崗位,一般的嵌入式消費公司崗位很少,我有認(rèn)識一個同學(xué),從大學(xué)就開始學(xué)習(xí)FPGA,我們那年電賽就是用的FPGA來完成的,現(xiàn)在他也還一直從事FPGA開發(fā)。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21952瀏覽量

613817 -

集成電路

+關(guān)注

關(guān)注

5417文章

11940瀏覽量

366948 -

asic

+關(guān)注

關(guān)注

34文章

1242瀏覽量

121953 -

pal

+關(guān)注

關(guān)注

1文章

43瀏覽量

27532

發(fā)布評論請先 登錄

FPGA入門:FPGA設(shè)計者入門必備!

FPGA如何從入門到高手?

求FPGA入門資料

Xilinx FPGA無痛入門,海量教程免費下載

FPGA快速入門經(jīng)驗談(part2)

FPGA硬件基礎(chǔ)之FPGA時鐘資源的工程文件免費下載

FPGA硬件基礎(chǔ)之FPGA的邏輯單元的工程文件免費下載

FPGA硬件基礎(chǔ)之FPGA的RAM存儲課件和工程文件

FPGA入門之什么是FPGA

FPGA入門之什么是FPGA

評論