芯東西3月8日消息,世界頂級先進半導體研究機構比利時微電子研究中心(imec)近日發(fā)布一篇深度好文,詳細解讀了下一代EUV***成像技術短期和長期的挑戰(zhàn)及創(chuàng)新方向。

imec長期與全球***霸主阿斯麥(ASML)以及臺積電、英特爾、三星等芯片制造巨頭深度合作,是這些大廠背后的頂級智囊,也是EUV(極紫外)***的幕后功臣之一。

隨著先進制程爭霸賽挺進2nm賽點,High NA(高數(shù)值孔徑)EUV***成為搶抓時間窗口、保障高良品率的關鍵設備,為此各大芯片制造巨頭眼巴巴地守在ASML門前排隊,都想先下手為強。

但imec先進成像、工藝和材料高級副總裁斯蒂芬·希爾(Steven Scheer)在接受采訪時非常理性地指出,要經(jīng)濟高效地引入High NA EUV***,還需翻越“四堵墻”,包括改進EUV光刻膠的厚度、底層材料的屬性、3D掩膜效應對成像的影響,以及與新型邏輯晶體管、存儲芯片組件進行協(xié)同設計。

引入High NA的優(yōu)先事項是什么?如何克服EUV光刻膠相關挑戰(zhàn)?imec計劃通過探索哪些技術路徑來造出更強***?未來兩到五年,哪些其他技術的發(fā)展會影響到光刻成像?斯蒂芬·希爾對這些備受關注的問題一一作出解答。

據(jù)他介紹,imec和ASML正在建立一個High NA EUV實驗室,以滿足芯片制造商的早期開發(fā)需求。imec還與成像設備和材料供應商廣泛合作,以便制備EUV光刻膠材料、底層、干法蝕刻、光掩膜、分辨率增強技術(RET)和計量技術。

01 引入High NA的首要任務:開發(fā)EUV光刻膠

斯蒂芬·希爾說,引入High NA最關鍵的事是考慮High NA工具的可用性。

ASML和德國鏡片生產(chǎn)商蔡司公司(Carl Zeiss AG)在集成模塊和光學組件方面取得了驚人的進展。盡管這兩大公司已經(jīng)為引入Low NA EUV***提供了許多與過程相關的突破性解決方案,但仍需進一步的改進才能使High NA EUV***運用得更為高效。

除了High NA工具外,EUV光刻膠的開發(fā)仍然是imec與生態(tài)系統(tǒng)合作伙伴的主要任務之一。

High NA EUV***的出現(xiàn)將進一步提高分辨率并縮小金屬間距,從而降低焦點深度。這固然會導致薄膜厚度尺度縮小,故需要采用新的EUV光刻膠和底層,以優(yōu)化蝕刻過程中EUV的吸收和圖案轉移。

此外,他們需要推動隨機粗糙度的持續(xù)改進。從過去看,光刻膠成像性能通過分辨率、線邊緣粗糙度(LER)或局部關鍵尺寸均勻性(LCDU)和靈敏度(也稱為RLS參數(shù))來表示。今天,鑒于隨機性的重要性,imec在早期開發(fā)階段已經(jīng)用RLS參數(shù)評估了成像性能,該參數(shù)反映了隨機性限制的工藝窗口。

他們相信這些解決方案可以緩解光刻膠系統(tǒng)引起的隨機缺陷,并擴大工藝窗口,同時降低NA值,imec打算與合作伙伴合作,在High NA實驗室演示這些新技術。

特征尺寸和EUV光刻膠厚度的減少也會影響計量。除打印性能外,急劇的尺寸微縮可能會影響準確性和精度,從而影響計量和檢測性能。

02 迎接EUV光刻膠挑戰(zhàn)imec開發(fā)新的工具箱Attolab

EUV光刻膠在光刻過程中具有重要作用,它不僅能保護襯底基座,還具備抗腐蝕的性能。關于克服與EUV光刻膠相關的挑戰(zhàn),imec提供了諸多幫助。斯蒂芬·希爾談道,為解決傳統(tǒng)多組分混合光刻膠系統(tǒng)引起的化學隨機性(即散粒噪聲以外的隨機性)問題,他們正在開發(fā)新的材料,例如含金屬的光刻膠或單組分光刻膠。imec將繼續(xù)和材料供應商開發(fā)新概念,并處理污染風險和流程集成挑戰(zhàn)等關鍵問題。

新型High NA EUV光刻膠系統(tǒng)不能在孤立的貯倉中開發(fā),而是需要與底層、新型光刻膠和高度選擇性蝕刻工藝進行共同優(yōu)化,以獲得最佳性能。

此外,為進一步了解EUV曝光下光刻膠和底層的行為、加快材料開發(fā),imec最近開發(fā)了一個名為Attolab的新工具箱用來匹配光刻膠和底層屬性。通過材料篩選、表面能量匹配研究、材料物理表征和界面工程,新的工具箱可以與光刻膠一起開發(fā)旋涂或沉積的底層薄膜,以實現(xiàn)優(yōu)化的LER、靈敏度的EUV圖案縮小。同時,涂膜的吸收系數(shù)和圖層特性可以通過輻射測量和反射測量來研究,imec將把這些技術提供給Attolab的合作伙伴。

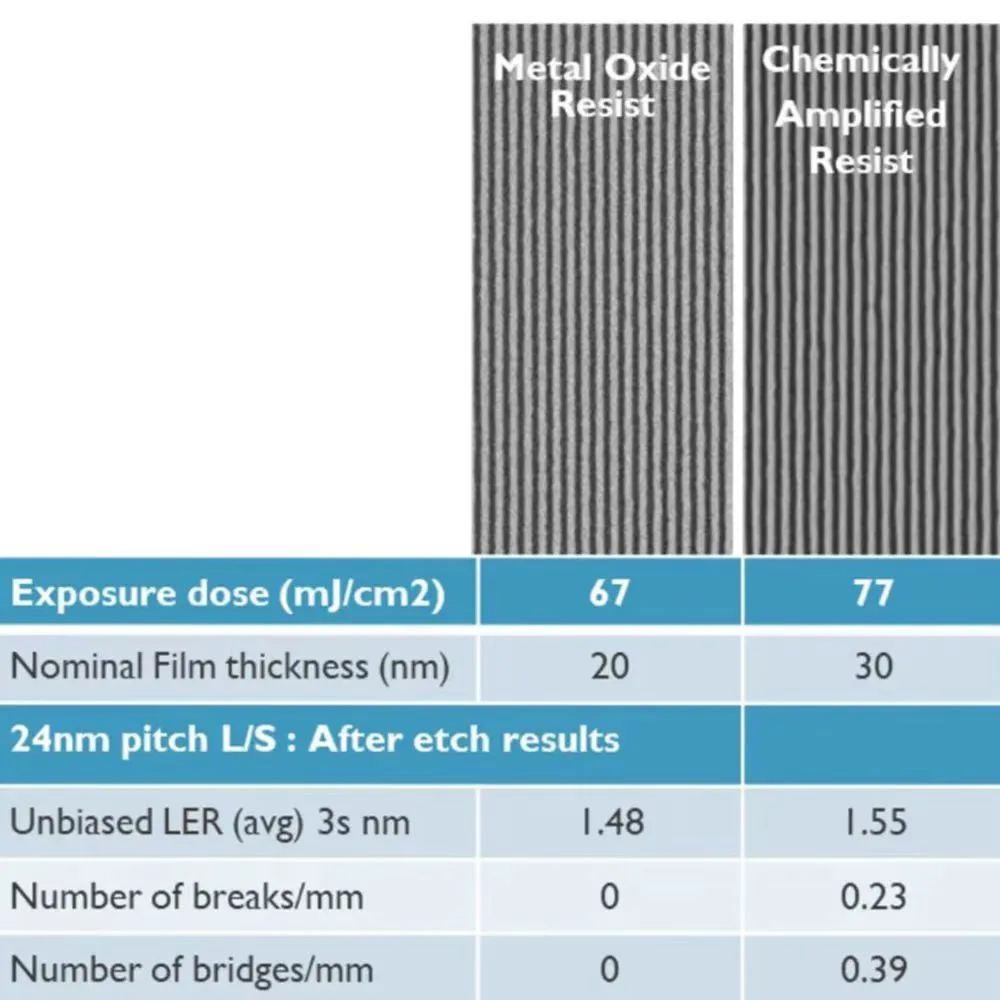

▲24nm間距線和空間:金屬氧化物光刻膠(MOR)和化學放大光刻膠(CAR)的成像開發(fā)。盡管薄膜厚度小,但MOR的劑量更低、LER和缺陷性更小。(圖源:imec官網(wǎng))

03 匯集完整的掩膜研發(fā)生態(tài)系統(tǒng)imec朝下一個光刻節(jié)點進軍

為迎來下一個光刻節(jié)點,imec正在持續(xù)探索中。斯蒂芬·希爾說,掩膜的開發(fā)正在進行新的演變。

為了滿足減少EUV曝光劑量的要求,imec正在對帶有Low-n吸收劑的掩膜進行大量調(diào)查,因為這些掩膜在低曝光劑量的狀態(tài)下會產(chǎn)生高對比度(或NILS)的空中強度分布。

同時,他們還關注晶圓隨機指數(shù)和掩膜3D效果。

晶圓的隨機缺陷由許多因素導致,其中掩膜可變性是其中之一。為了解決這個問題,他們研究了哪些類型的掩膜可變性(包括不同的粗糙度)在晶圓上更容易增加隨機性,其目的是提出更新的掩膜和blank規(guī)格。

此外,High NA EUV***將使用變形鏡頭,在x和y方向提供不等的放大倍率。這種變形意味著晶圓將進行場拼接,以實現(xiàn)與其他傳統(tǒng)光學光刻相同的晶圓場尺寸。晶圓場拼接在掩膜層面上更重視掩膜場邊緣的質量。

imec了解到掩膜與EUV照明的相互作用越來越重要,因此,他們匯集了完整的掩膜研發(fā)生態(tài)系統(tǒng),與供應商一起支持掩膜創(chuàng)新(如新型吸收器)的工業(yè)化,并在imec-ASML High NA EUV實驗室中通過建模探索掩膜復雜性(如可變性或拼接)。

斯蒂芬·希爾還談道,以上問題都不是引入High NA EUV***的根本問題。為了順利、及時和高效引入具有最大性能的High NA EUV***,最關鍵問題應該是積極應對這些挑戰(zhàn),并為生態(tài)系統(tǒng)的關鍵參與者提供有效的協(xié)作平臺。imec和ASML圍繞第一臺High NA***建立High NA EUV實驗室的主要動機,也是希望促進High NA EUV***的迅速引進和升級。

04 存儲和邏輯新設備概念興起未來2-5年內(nèi)將影響成像領域

談到未來兩到五年內(nèi)影響成像領域的其他發(fā)展,斯蒂芬·希爾提出,除了EUV***的創(chuàng)新外,越來越多利用3D的存儲和邏輯新設備概念的興起也帶來了獨特的成像機會。

互補場效應晶體管技術(CFET)是超越全環(huán)繞柵極(GAA)納米片的未來器件,它將一個FET通道堆疊在另一個FET設備上。設備制造需要高縱橫比的成像流程,以實現(xiàn)有源部分、柵極、源極/漏極凹槽以及中線M0A接觸的形成。此外,還需要大量的材料,如金屬或絕緣體。

自下而上沉積或區(qū)域選擇性沉積(ASD)的創(chuàng)新,可以在降低CFET的工藝復雜性方面發(fā)揮重要作用。

接下來,為了讓基于CFET的標準單元從5軌擴展到4軌,CFET設備可能會與背面功率傳輸集成。這種新的布線選擇方案需要具有高縱橫比的通孔開口和良好選擇性的空間間隔物來自對準成像。

在內(nèi)存中,DRAM目前依賴于一個窄而高的電容器作為位單元。當縮小間距以增加密度時,電容器的橫向臨界尺寸(CD)將繼續(xù)縮小,為保持電容恒定,電容器需要做得越來越高。這不僅會導致制造問題和產(chǎn)量損失,2D DRAM也將達到基本材料極限。

為了克服這些問題,imec正在考慮各種3D DRAM流程,并在模塊層面應對關鍵挑戰(zhàn)。

人們可能會看到半導體氧化物等新材料的引入,輔之以使用幾個高縱橫比蝕刻和橫向凹槽,接著,用襯里、電介質和金屬填充垂直孔和側空腔,要成功完成這幾項步驟,會像今天在3D-NAND-Flash技術中遇到的難題一樣具有挑戰(zhàn)性。

05 imec重視可持續(xù)發(fā)展技術、環(huán)境缺一不可

今天,芯片制造產(chǎn)生的二氧化碳估計約占全球二氧化碳排放量的0.1%。然而,由于先進技術節(jié)點的復雜性日益增加,與制造邏輯技術相關的二氧化碳排放量預計將在未來10年內(nèi)還將翻一番。

據(jù)斯蒂芬·希爾預計,晶圓的總產(chǎn)量將每年增長約8%。如果他們什么都不做,與芯片制造相關工業(yè)排放量將在未來十年內(nèi)翻兩番。

根據(jù)《巴黎協(xié)定》,所有工業(yè)部門都應每十年將排放量減半。換句話說,在“不作為”的情況下,imec將偏離目標八倍。

斯蒂芬·希爾說,可持續(xù)性是imec研究的關鍵。他們啟動了可持續(xù)半導體技術和系統(tǒng)(SSTS)計劃,聚合供應鏈,共同實現(xiàn)芯片制造的零排放目標。

為了量化半導體工廠對環(huán)境的影響,他們正在構建一個名為imec.netzero的虛擬工廠。imec通過與設備和材料供應商合作,不斷對開發(fā)的模型進行基準測試和驗證。

在即將舉行的SPIE高級光刻和成像會議上,他們將對先進芯片制造過程中圖案對碳排放的影響進行定量評估。在他們的實際工廠中,imec已經(jīng)確定了污染物高排放區(qū)域,并針對環(huán)境問題提供了解決方案,包括減少使用氟化蝕刻氣體、減少用水、回收稀有材料、回收氫氣和采用低劑量光刻工藝。

在開發(fā)未來技術的同時應對環(huán)境影響似乎是一項無比艱巨的任務。但斯蒂芬·希爾相信imec可以盡最大努力做到減少對環(huán)境的影響。

06 結語:光刻技術任重道遠

隨著半導體技術的不斷革新,芯片制程一路微縮,目前由于物理限制,芯片制程的演進已臨近瓶頸期。imec把創(chuàng)新目標放在改進高性能半導體技術上,其中光刻成像作為輔助芯片制造的關鍵技術,需要不斷應對未來發(fā)展的挑戰(zhàn)和創(chuàng)新。

作為全球先進微電子研究中心imec的高管,斯蒂芬·希爾提出了很多有建設性意義的思考,包括High NA技術的引入、EUV光刻膠相關的挑戰(zhàn)等。除此之外,斯蒂芬·希爾對于環(huán)境生態(tài)問題也頗為重視,為此,imec不僅減少了污染物的排放,還回收可用物,采取環(huán)境友好型技術。

未來幾年里,imec將繼續(xù)致力于研究光刻技術,而該技術的不斷進步將是推動芯片制造挺進埃米時代的關鍵,為此,還需要整個半導體生態(tài)系統(tǒng)共同創(chuàng)新和協(xié)作。

審核編輯 :李倩

-

光刻機

+關注

關注

31文章

1163瀏覽量

48017 -

光刻技術

+關注

關注

1文章

149瀏覽量

16089 -

EUV

+關注

關注

8文章

609瀏覽量

86827

原文標題:下一代EUV光刻機,關鍵技術拆解!

文章出處:【微信號:算力基建,微信公眾號:算力基建】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

電機系統(tǒng)節(jié)能關鍵技術及展望

下一代高速銅纜鐵氟龍發(fā)泡技術

納米壓印技術:開創(chuàng)下一代光刻的新篇章

百度李彥宏談訓練下一代大模型

使用下一代GaNFast和GeneSiC Power實現(xiàn)電氣化我們的世界

下一代機器人技術:工業(yè)自動化的五大趨勢

通過電壓轉換啟用下一代ADAS域控制器應用說明

實現(xiàn)具有電平轉換功能的下一代無線信標

通過下一代引線式邏輯IC封裝實現(xiàn)小型加固型應用

日產(chǎn)汽車與本田推進下一代軟件平臺技術的共同研發(fā)項目

IaaS+on+DPU(IoD)+下一代高性能算力底座技術白皮書

24芯M16插頭在下一代技術中的潛力

下一代EUV***,關鍵技術拆解!

下一代EUV***,關鍵技術拆解!

評論