一.Vt 簡介

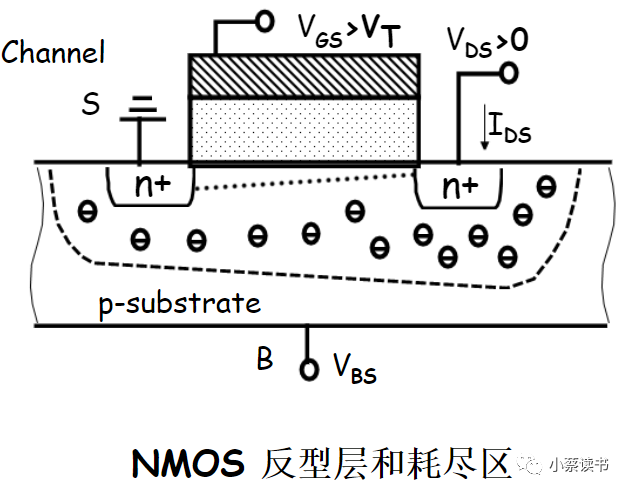

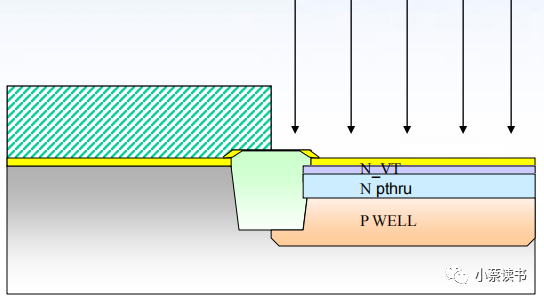

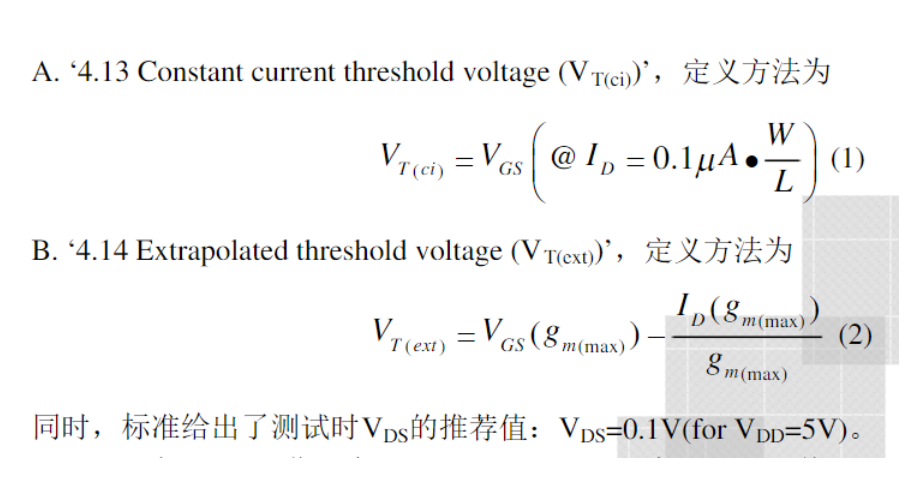

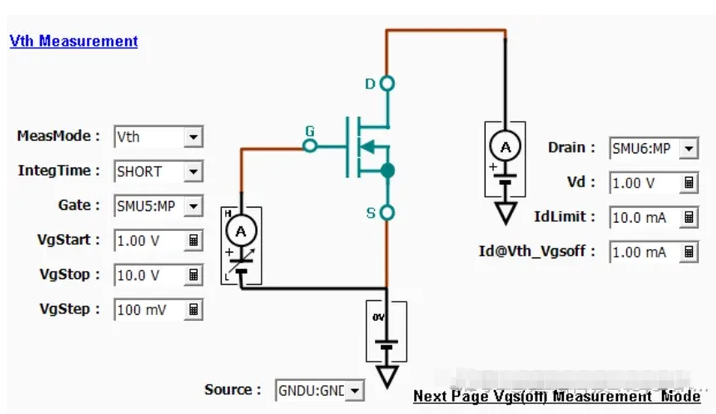

Vt指的是MOS管的閾值電壓(threshold voltage)。具體定義(以下圖NMOS為例):當柵源電壓(Vgs)由0逐漸增大,直到MOS管溝道形成反型層(圖中的三角形)所需要的電壓為閾值電壓。

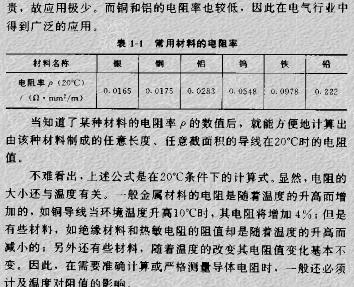

二.閾值電壓和哪些因素有關系

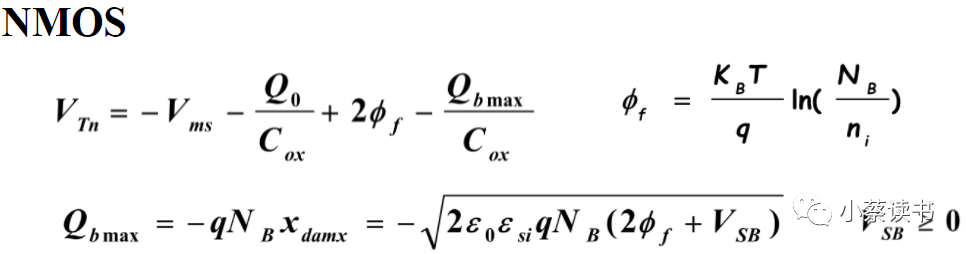

首先看閾值電壓的公式(以NMOS為例),具體推導過程不再介紹。

相關因素

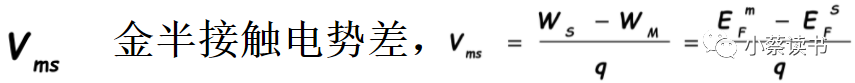

1.金半接觸電勢差:和柵極金屬方塊電阻以及襯底摻雜濃度有關。

2.氧化層中的電荷密度

3.半導體費米勢

4.柵氧化層厚度

5.襯底摻雜濃度

6.源襯電壓

三.不同Vt cell工藝是怎么實現的?

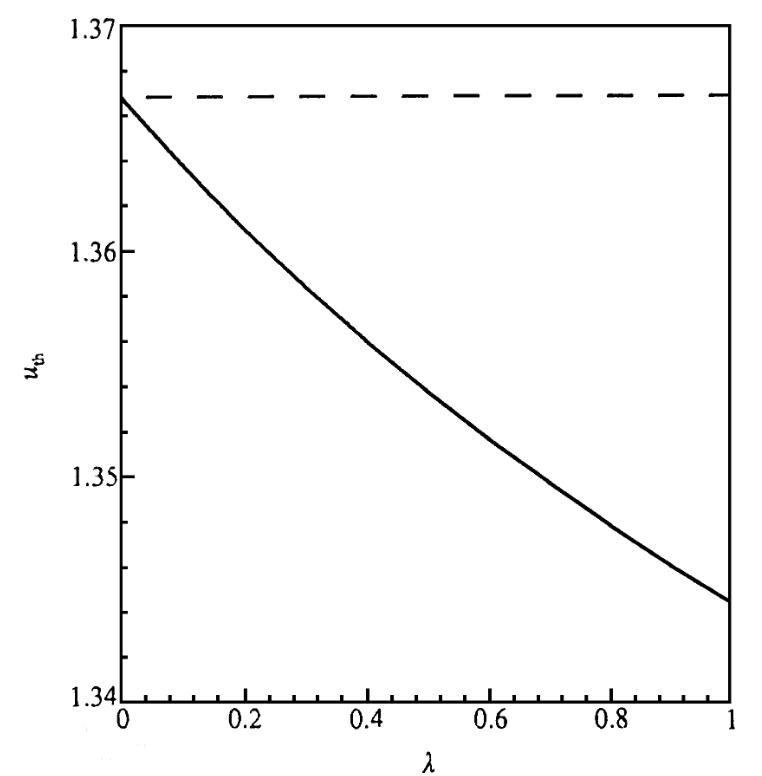

上面提到了這么多影響Vt的因素,那么實際中不同的Vt cell是通過控制哪個變量來實現的呢?襯底摻雜濃度。現在有的先進工藝有7、8種Vt cell,看到比較老的工藝資料(如下圖)介紹是通過控制襯底摻雜濃度來控制閾值電壓,可能先進工藝會用到更多手段。簡單的理解就是:溝通摻雜濃度越高(以NMOS為例),越容易形成反型層,所以閾值電壓越小;或者可以反的理解為假如不做溝道摻雜,閾值電壓應該是最大的。

摻雜工藝需要控制的三個變量:氣體類型(帶B或者P)、注入劑量、注入能量。

四.功耗與性能(時序)的tradeoff

foundary提供這么多種Vt cell,就是為了讓用戶根據不同設計的電路做出最好的功耗與性能的tradeoff。首先要說的是:Vt越大(比如HVT),cell功耗越小,延時越大;相應的Vt越小(比如ULVT),cell功耗越大,延時越小。所以對于一個design來說,性能要求比較高的模塊,可能需要ULVT cell多一點,比如CPU;對于性能要求低一些的cell,不需要那么多ULVT cell就可以省功耗。當然cell的延時不僅和Vt類型有關,也和溝道寬長比有關(比如寬度7T,9T,長度C30,C35)。

1.時序與Vt

還記得剛入行的時候,跑完place,時序有些違例,然后就想知道是繼續往下跑還是調整floorplan。找young master過來看了一下,打開時序報告,看了下最大違例路徑launch上的cell類型,很多是LVT或者SVT,說可以往下跑,還可以換ULVT以滿足時序。這就是使用ULVT來減小延時滿足setup的案例。

2.功耗與Vt

在綜合、PnR、STA階段都可以采取一些措施減小功耗,看了下原理:在時序路徑setup滿足且有余量的情況下,把這些路徑下的cell 換成更高閾值的cell,這樣最少可以減小leakage power;現在innovus也可以在PnR階段讀saif文件去優化dynamic power。

在IR/EM signoff階段,有一種違例類型就是:功耗太大的cell(驅動太大和Vt太小),然后會讓block負責人去報這條路徑下的setup余量,假如有,可以換功耗小的cell(小驅動和高Vt),這也是一種fix IR/EM的方式。

3.LVT cell做時鐘樹一定比SVT做時鐘樹功耗大嗎?

這里只討論時鐘樹的功耗,之前的實驗結果顯示:LVT cell做時鐘樹并不一定比SVT做時鐘樹功耗大。首先從leakage power的角度講,假如時鐘樹的buffer/invert級數一定,LVT cell leakage power肯定比SVT大;但是SVT換成LVT,時鐘樹的級數一定不變嗎(怎么變?)?dynamic power(transition,load)也會變小嗎?

編輯:黃飛

-

MOS管

+關注

關注

108文章

2518瀏覽量

69806 -

Cell

+關注

關注

0文章

19瀏覽量

17512

原文標題:搞芯片不懂cell別亂用!看看Vt cell都是啥?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

lcd的顯示速度跟哪些因素有關呢?

MOS管閾值電壓與溝長和溝寬的關系

如何突破EDA封鎖 卷起來的閾值電壓

NMOS晶體管的閾值電壓公式 nmos晶體管的閾值電壓與哪些因素有關

影響MOSFET閾值電壓的因素

什么是MOS管亞閾值電壓?MOSFET中的閾值電壓是如何產生的?

淺談影響MOSFET閾值電壓的因素

MOSFET閾值電壓是什么?影響MOSFET閾值電壓的因素有哪些?

不同Vt cell工藝是怎么實現的?閾值電壓和哪些因素有關系?

不同Vt cell工藝是怎么實現的?閾值電壓和哪些因素有關系?

評論