always @ (posedge inputs)

begin

...

end

因為這個時鐘inputs很有問題。如果begin ... end語句段涉及到多個D觸發器,你無法保證這些觸發器時鐘輸入的跳變沿到達的時刻處于同一時刻(準確的說是相差在一個很小的可接受的范圍)。因此,如果寫出這樣的語句,EDA工具多半會報clock skew > data delay,造成建立/保持時間的沖突。本人曾經也寫出過這樣的語句,當時是為了做分頻,受大二學的數字電路的影響,直接拿計數器的輸出做了后面模塊的時鐘。當初用的開發工具是max+plusII,編譯也通過了,燒到板子上跑倒也能跑起來(估計是因為時鐘頻率較低, 6M ),但后來拿到QuartusII中編譯就報clock skew > data delay。大家可能會說分頻電路很常見的啊,分頻輸出該怎么用呢。我一直用的方法是采用邊沿檢測電路,用HDL語言描述大概是這樣:always @ (posedge Clk)

begin

inputs_reg <= inputs;

if (inputs_reg == 1'b0 && inputs == 1'b1)

begin

...

end

...

end

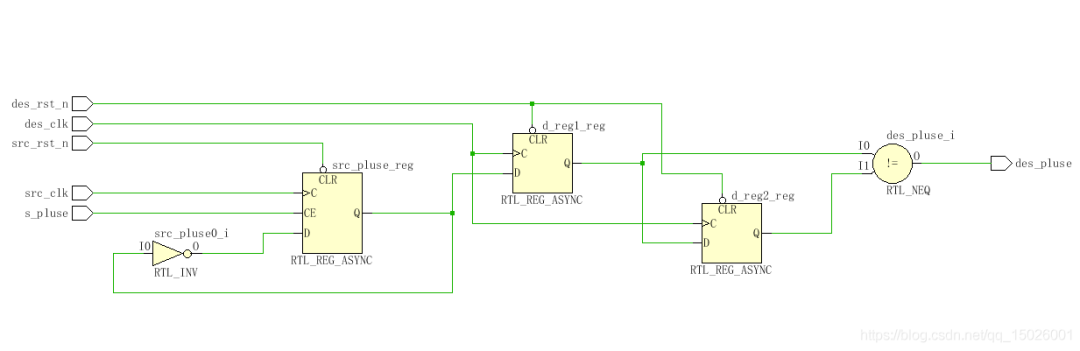

這是上跳沿檢測的電路,下跳沿電路大家依此類推。 2.異步時鐘域信號的處理 這個問題也得分單一信號和總線信號來討論 2.1單一信號(如控制信號)的處理 如果這個輸入信號來自異步時鐘域(比如FPGA芯片外部的輸入),一般采用同步器進行同步。最基本的結構是兩個緊密相連的觸發器,第一拍將輸入信號同步化,同步化后的輸出可能帶來建立/保持時間的沖突,產生亞穩態。需要再寄存一拍,減少(注意是減少)亞穩態帶來的影響。這種最基本的結構叫做電平同步器。 如果我們需要用跳變沿而不是電平又該怎樣處理呢,還記得1里面講的邊沿檢測電路么?在電平同步器之后再加一級觸發器,用第二級觸發器的輸出和第三級觸發器的輸出來進行操作。這種結構叫做邊沿同步器。

always @ (posedge Clk)

begin

inputs_reg1 <= inputs;

inputs_reg2 <= inputs_reg1;

inputs_reg3 <= inputs_reg2;

if (inputs_reg2 == 1'b1 && inputs_reg3 == 1'b0)

begin

...

end

...

end

以上兩種同步器在慢時鐘域信號同步入快時鐘域時工作的很好,但是反過來的話,可能就工作不正常了。舉一個很簡單的例子,如果被同步的信號脈沖只有一個快時鐘周期寬,且位于慢時鐘的兩個相鄰跳變沿之間,那么是采不到的。這時就需要采用脈沖同步器。這種同步器也是由3個觸發器組成。 脈沖同步器 由于脈沖在快時鐘域傳遞到慢時鐘域時,慢時鐘有時無法采樣的信號奈奎是特采樣定理,因此需要對信號進行處理,可以讓慢信號采樣到。脈沖同步器的結果如圖: ?

? 2.2總線信號的處理

如果簡單的對異步時鐘域過來的一組信號分別用同步器的話,那么對這一組信號整體而言,亞穩態出現的幾率將大大上升。基于這一觀點,對于總線信號的處理可以有兩種方式。

如果這組信號只是順序變化的話(如存儲器的地址),可以將其轉換為格雷碼后再發送,由于格雷碼相鄰碼字只相差一個比特,上面說的同步器可以很好的發揮作用

但是如果信號的變化是隨機的(如存儲器的數據),這種方法便失效了,這時可以采用握手的方式或者采用FIFO或DPRAM進行緩存。RAM緩存的方式在突發數據傳輸中優勢比較明顯,現在高檔一點的FPGA中都有不少的BlockRAM資源,且支持配置為DPRAM或FIFO,這種處理方法在通信電路中非常常用。

?

? 2.2總線信號的處理

如果簡單的對異步時鐘域過來的一組信號分別用同步器的話,那么對這一組信號整體而言,亞穩態出現的幾率將大大上升。基于這一觀點,對于總線信號的處理可以有兩種方式。

如果這組信號只是順序變化的話(如存儲器的地址),可以將其轉換為格雷碼后再發送,由于格雷碼相鄰碼字只相差一個比特,上面說的同步器可以很好的發揮作用

但是如果信號的變化是隨機的(如存儲器的數據),這種方法便失效了,這時可以采用握手的方式或者采用FIFO或DPRAM進行緩存。RAM緩存的方式在突發數據傳輸中優勢比較明顯,現在高檔一點的FPGA中都有不少的BlockRAM資源,且支持配置為DPRAM或FIFO,這種處理方法在通信電路中非常常用。

精彩推薦 至芯科技12年不忘初心、再度起航2月11日北京中心FPGA工程師就業班開課、線上線下多維教學、歡迎咨詢! 基于FPGA的千兆以太網ARP和UDP的實現 FPGA學習-基于FPGA的圖像處理掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:FPGA同步轉換FPGA對輸入信號的處理

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1645文章

22033瀏覽量

617769

原文標題:FPGA同步轉換FPGA對輸入信號的處理

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AMD FPGA異步模式與同步模式的對比

進群免費領FPGA學習資料!數字信號處理、傅里葉變換與FPGA開發等

使用FPGA控制ADS8365模數轉換,沒有EOC輸出,FPGA無法讀取數據,為什么?

ADC344X的外部同步輸入SYSREF范圍是-0.3~(AVDD + 0.3 = 2.1)V,是否可以通過FPGA輸出1.8V信號來直接驅動?

FPGA 實時信號處理應用 FPGA在圖像處理中的優勢

FPGA 與微控制器優缺點比較

在FPGA里面例化了8個jesd204B的ip核同步接收8塊AFE芯片的信號,怎么連接設備時鐘和sysref到AFE和FPGA?

FPGA在數據處理中的應用實例

實現下一代具有電壓電平轉換功能的處理器、FPGA 和ASSP

FPGA同步轉換FPGA對輸入信號的處理

FPGA同步轉換FPGA對輸入信號的處理

評論