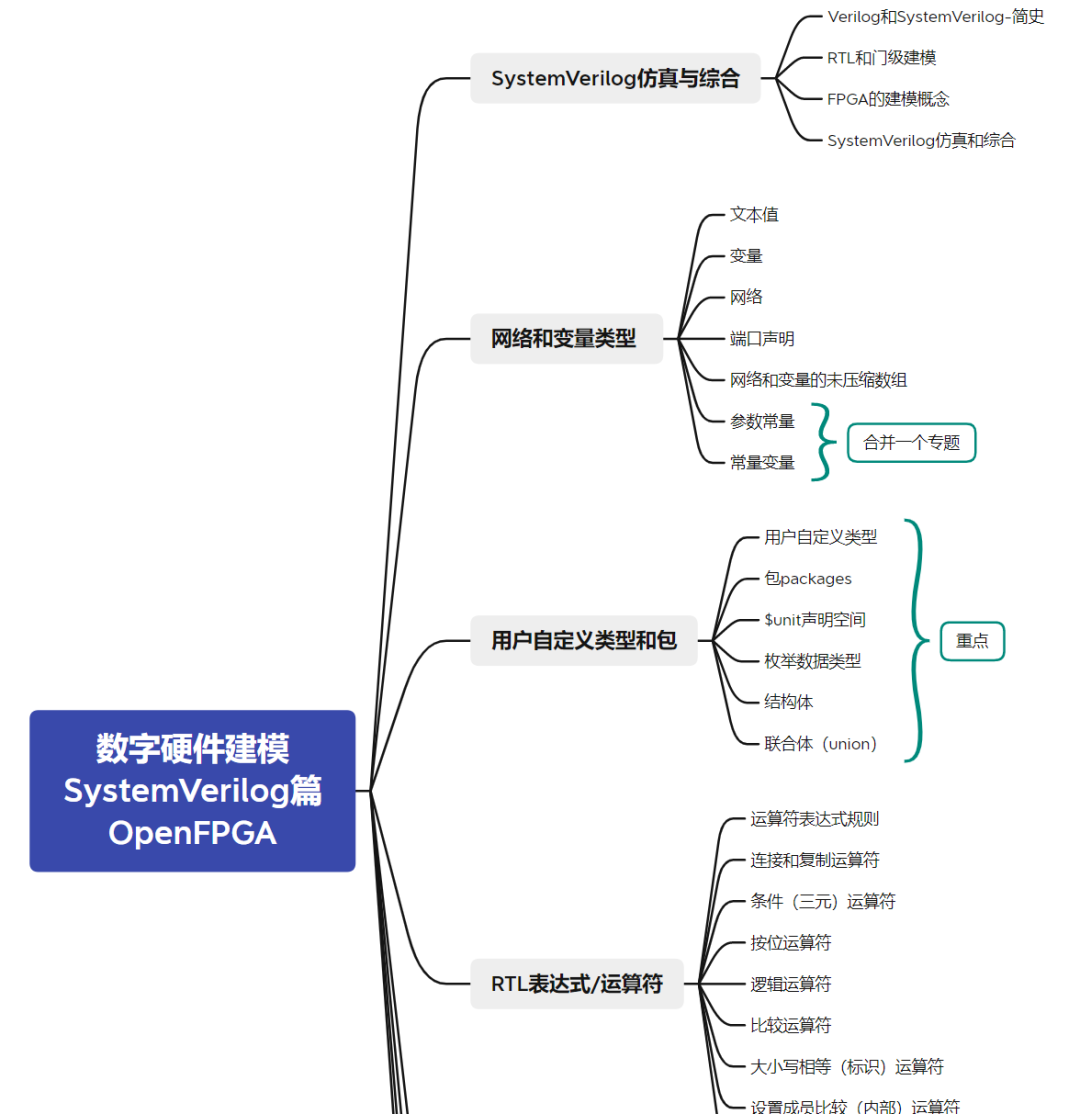

數(shù)字硬件建模SystemVerilog-條件(三元)運(yùn)算符

經(jīng)過(guò)幾周的更新,SV核心部分用戶自定義類型和包內(nèi)容已更新完畢,接下來(lái)就是RTL表達(dá)式和運(yùn)算符。

馬上HDLBits-SystemVerilog版本也開(kāi)始準(zhǔn)備了,基本這一部分完成后就開(kāi)始更新~

介紹

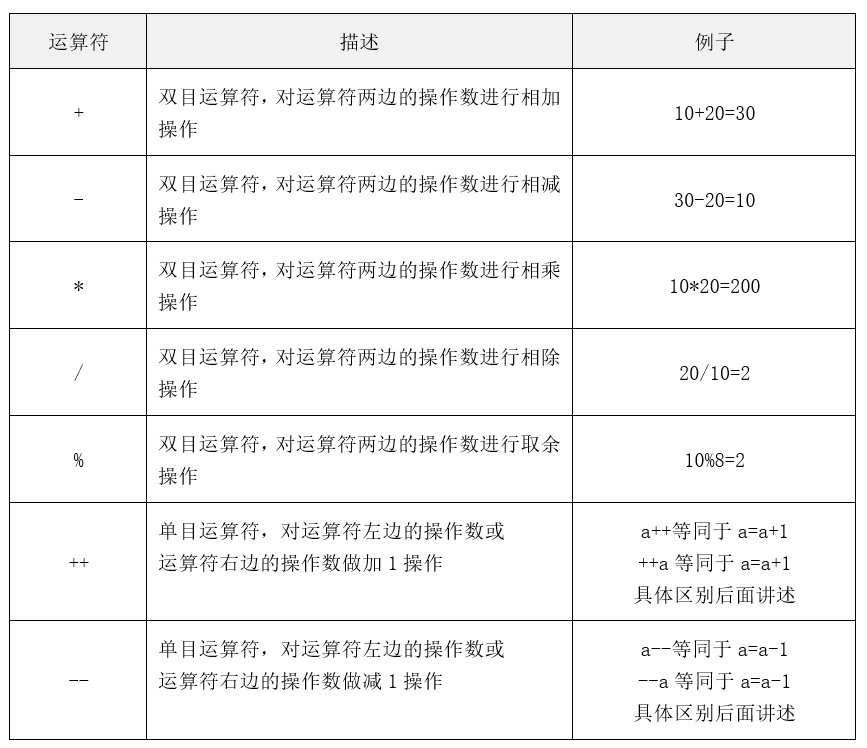

RTL建模中廣泛使用的運(yùn)算符是條件運(yùn)算符,也稱為三元運(yùn)算符,該運(yùn)算符用于在兩個(gè)表達(dá)式之間進(jìn)行選擇——表5-2列出了用于表示條件運(yùn)算符的重點(diǎn)。

表5-2:RTL建模的條件(三元)運(yùn)算符| 運(yùn)算符 | 示例用法 | 描述 |

| -------- | ---------- | ------------------------------------------------------------------------------- |

| ?: | s?m:n | 如果s為真,則選擇m;如果s為假,則選擇n,否則(s不為真不為假)對(duì)m和n進(jìn)行按位比較 |

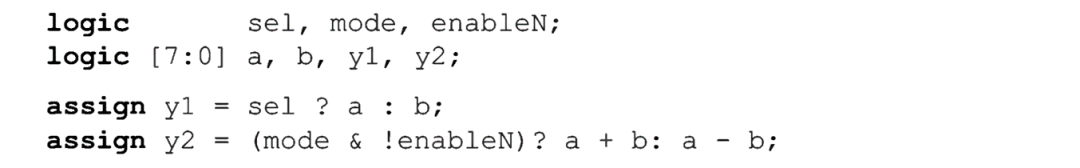

問(wèn)號(hào)(?)前面列出的表達(dá)式被稱為控制表達(dá)式(control expression),表示它可以是一個(gè)簡(jiǎn)單的整數(shù)值(任何大小的向量,包括1位),也可以是另一個(gè)返回整數(shù)值的操作的結(jié)果。例如:

使用以下規(guī)則將控制表達(dá)式計(jì)算為true或false:

- 如果所有位為l,則表達(dá)式為true。

- 如果所有位均為0,則表達(dá)式為false。

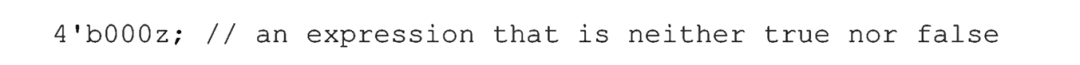

- 如果未設(shè)置任何位且并非所有位均為0,則表達(dá)式未知,如果某些位為X或Z,則可能出現(xiàn)這種情況。

對(duì)于4-state值,控制表達(dá)式可能既不是真的也不是假的。在下面的值中,沒(méi)有一個(gè)位是l,但不是所有的位都是0。

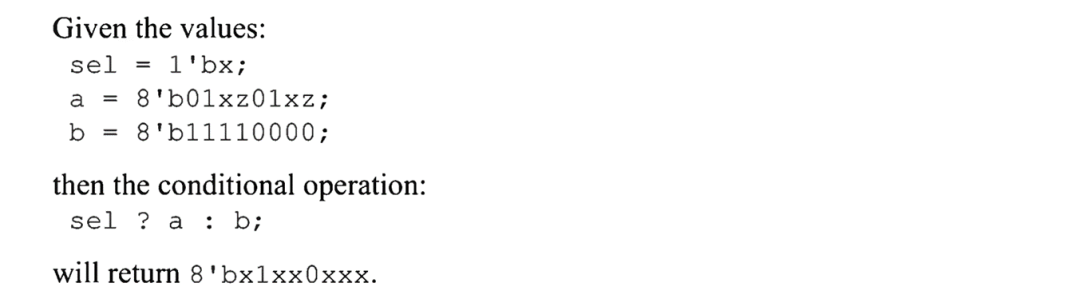

當(dāng)控制表達(dá)式未知時(shí),條件運(yùn)算符對(duì)兩個(gè)可能的返回值進(jìn)行按位比較。如果對(duì)應(yīng)位均為0,則該位位置返回0,如果對(duì)應(yīng)位均為l,則該位位置返回1。如果對(duì)應(yīng)的位不同,或者任一位有X或Z值,則返回該位位置的X。下面的示例演示了這種仿真行為。

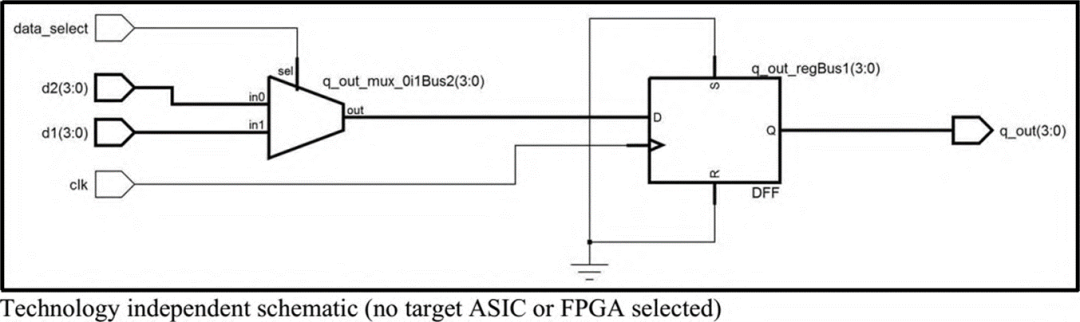

條件運(yùn)算符的行為通常類似于硬件多路復(fù)用器。示例5-3說(shuō)明了如何使用條件運(yùn)算符在寄存器的兩個(gè)輸入之間進(jìn)行選擇。圖5-3顯示了綜合該示例的結(jié)果。條件運(yùn)算符映射到四個(gè)多路復(fù)用器,四位d1和d2輸入的每一位對(duì)應(yīng)一個(gè)多路復(fù)用器。

示例5-3:使用條件運(yùn)算符:4位多路復(fù)用寄存器D輸入

// 4-bit register with multiplexed D input, using conditional

// operator.

//

//`begin_keywords "1800-2012" // use SystemVerilog-2012 keywords

module muxed_register

#(parameter WIDTH = 4) // register size

(input logic clk, // 1-bit input

input logic data_select, // 1-bit input

input logic [WIDTH-1:0] d1, d2, // scalable input size

output logic [WIDTH-1:0] q_out // scalable output size

);

timeunit 1ns; timeprecision 1ns;

always_ff @(posedge clk)

q_out <= data_select? d1 : d2; // store d1 or d2

endmodule: muxed_register

//`end_keywords

圖形5-3:示例5-3的綜合結(jié)果:條件運(yùn)算符(多路復(fù)用寄存器)

圖5-3所示的電路是綜合編譯器將電路映射到特定ASIC或FPGA目標(biāo)實(shí)現(xiàn)之前的中間通用綜合結(jié)果。用于生成圖5-3的綜合編譯器使用了具有未連接的set和rst輸入的通用觸發(fā)器,使用ASIC或FPGA庫(kù)的最終實(shí)現(xiàn)可能能夠使用沒(méi)有這些輸入的觸發(fā)器(如果目標(biāo)設(shè)備中可用)。不同的綜合編譯器可能會(huì)使用不同的通用型組件來(lái)表示這些中間結(jié)果。

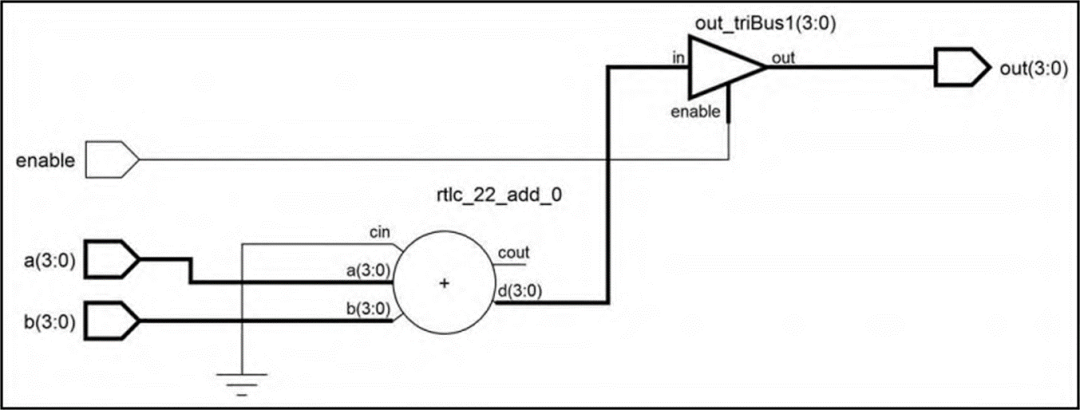

條件運(yùn)算符并不總是作為多路復(fù)用器實(shí)現(xiàn)。綜合編譯器可能會(huì)根據(jù)操作數(shù)的類型和運(yùn)算的上下文,將條件運(yùn)算符映射并優(yōu)化為其他類型的門級(jí)邏輯。在示例5-4中,條件運(yùn)算符表示三態(tài)緩沖器,而不是多路復(fù)用邏輯,圖5-4顯示了綜合該示例的結(jié)果,

示例5-4:使用條件運(yùn)算符:帶三態(tài)輸出的4位加法器

// 4-bit adder with tri-state outputs, using conditional operator

// (no carry).

//

//`begin_keywords "1800-2012" // use SystemVerilog-2012 keywords

module tri_state_adder

#(parameter N = 4) // N-bit adder size

(input logic enable, // output enable

input logic [N-1:0] a, b, // scalable input size

output tri logic [N-1:0] out // tri-state output, net type

);

timeunit 1ns; timeprecision 1ns;

assign out = enable? (a + b) : 'z; // tri-state buffer

endmodule: tri_state_adder

//`end_keywords

在本例中,條件運(yùn)算符(?)選擇輸出端口應(yīng)分配(a+b)或高阻抗。如果en為false,則將out賦值為z。’z標(biāo)記是一個(gè)文字值,用于將表達(dá)式的所有位設(shè)置為高阻抗,并自動(dòng)縮放到表達(dá)式的向量大小。有關(guān)向量填充文字值的更多詳細(xì)信息,請(qǐng)參見(jiàn)之前的文章。

在示例5-4中觀察,out三態(tài)輸出端口被聲明為3-state logic類型,而不是通常的邏輯類型,logic數(shù)據(jù)類型只定義端口時(shí)可以有四態(tài)值,它不定義端口類型是網(wǎng)絡(luò)類型或者變量類型。輸出端口默認(rèn)為變量類型,除非顯式聲明為NET(網(wǎng)絡(luò))類型。(相反,輸入端口將默認(rèn)為NET類型,除非顯式聲明為變量類型),關(guān)鍵字?tri聲明網(wǎng)絡(luò)類型。tri類型在各個(gè)方面都與wire類型相同,但tri關(guān)鍵字可以幫助記錄網(wǎng)絡(luò)或端口的預(yù)期三態(tài)(高阻抗)值。

圖5-4:示例5-4的綜合結(jié)果:條件運(yùn)算符(三態(tài)輸出)

-

建模

+關(guān)注

關(guān)注

1文章

315瀏覽量

61377 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60588 -

運(yùn)算符

+關(guān)注

關(guān)注

0文章

172瀏覽量

11325

發(fā)布評(píng)論請(qǐng)先 登錄

C語(yǔ)言運(yùn)算符的使用方法

條件運(yùn)算符是什么_條件運(yùn)算符有哪些

單目運(yùn)算符是什么_單目運(yùn)算符有哪些

條件運(yùn)算符的用法_C運(yùn)算符的結(jié)合方向

C運(yùn)算符的優(yōu)先級(jí)和結(jié)合性詳細(xì)解決

淺析MySQL中的各類運(yùn)算符

條件(三元)運(yùn)算符

條件(三元)運(yùn)算符

評(píng)論