內(nèi)容提要

創(chuàng)意電子采用臺積電 N3 制程工藝,在 Cadence Innovus 設計實現(xiàn)的助力下,實現(xiàn)運算速度為 3.16GHz 的 HPC 核心設計,其中包含了 350 萬個實例

創(chuàng)意電子在臺積電 N5 制程上采用了 Cadence Cerebrus AI 解決方案,在 CPU 設計上,成功縮小 9% 的設計面積并降低 8% 的功耗

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,創(chuàng)意電子(GUC)借助 Cadence 數(shù)字解決方案成功完成先進的高性能計算 (HPC)設計和 CPU 設計。其中,HPC 設計采用了臺積電先進的 N3 制程,運用 Cadence Innovus Implementation System 設計實現(xiàn)系統(tǒng),順利完成首款具有高達 350 萬個實例,時鐘速度高達到 3.16GHz 的先進設計。另一款 CPU 設計采用 AI 賦能的 Cadence Cerebrus Intelligent Chip Explorer 和完整的數(shù)字設計流程,借助臺積電 N5 制程工藝,成功讓功耗降低 8%,設計面積縮小 9%,同時顯著提升了工程效率。

Innovus Implementation System 設計實現(xiàn)系統(tǒng)具備高度精確的 GigaPlace 引擎,支持臺積電 FINFLEX 單元行布局,可在整個流程中考慮引腳連接,以實現(xiàn)臺積電 N3 制程設計規(guī)則檢查(DRC)收斂。先進的 GigaOpt 引擎從臺積電 N3 庫中部署最優(yōu)配置,同時平衡不同單元行的利用率,實現(xiàn)了更好的優(yōu)化。Innovus 設計實現(xiàn)系統(tǒng)還包括一個大規(guī)模的并行架構,并整合了成熟的 NanoRoute 引擎,助力創(chuàng)意電子在設計流程的初期就能解決信號完整性問題,同時改善布線后的設計相關性。

Cadence Cerebrus 與完整的 Cadence 數(shù)字產(chǎn)品線相結合,在助力創(chuàng)意電子優(yōu)化功率、性能和面積(PPA)方面發(fā)揮重要作用,并在 5nm CPU 設計中通過綜合、設計實現(xiàn)到簽核的完整流程,提升工程團隊的生產(chǎn)力。Cadence Cerebrus 的獨特之處在于以 AI 強化學習引擎,可自主優(yōu)化創(chuàng)意電子的設計流程,幫助團隊突破工程設計的人工極限,加快產(chǎn)品上市。

創(chuàng)意電子設計服務中心資深副總經(jīng)理林景源博士表示:“創(chuàng)意電子是為 AI、HPC、5G、工業(yè)和其他新興應用提供先進芯片解決方案的市場領導者。我們致力于向客戶提供最具競爭力的設計,因此對我們來說,投資于領先的技術非常重要。我們選擇 Cadence Cerebrus Intelligent Chip Explorer,正是因為其與更廣泛的數(shù)字流程相結合,有助于我們通過人工智能技術加快設計周轉,同時還能改善 PPA。Innovus 設計實現(xiàn)系統(tǒng)是我們的得力助手,讓我們成功交付了首款 N3 芯片,助力團隊加速創(chuàng)建高性能、低功耗的 HPC 設計。”

Cadence Cerebrus AI 解決方案和 Innovus Implementation 設計實現(xiàn)系統(tǒng)是完整數(shù)字設計流程的一部分,支持 Cadence 的智能系統(tǒng)設計(Intelligent System Design)戰(zhàn)略,旨在實現(xiàn)系統(tǒng)級芯片的卓越設計。

審核編輯:湯梓紅

-

臺積電

+關注

關注

44文章

5738瀏覽量

168853 -

cpu

+關注

關注

68文章

11029瀏覽量

215858 -

Cadence

+關注

關注

65文章

962瀏覽量

143767 -

AI

+關注

關注

87文章

34063瀏覽量

275192 -

制程工藝

+關注

關注

0文章

46瀏覽量

9531

原文標題:創(chuàng)意電子采用 Cadence 數(shù)字解決方案完成首款臺積電 N3 制程芯片及首款 AI 優(yōu)化的 N5 制程設計

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

Cadence攜手臺積公司,推出經(jīng)過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發(fā)展

西門子與臺積電合作推動半導體設計與集成創(chuàng)新 包括臺積電N3P N3C A14技術

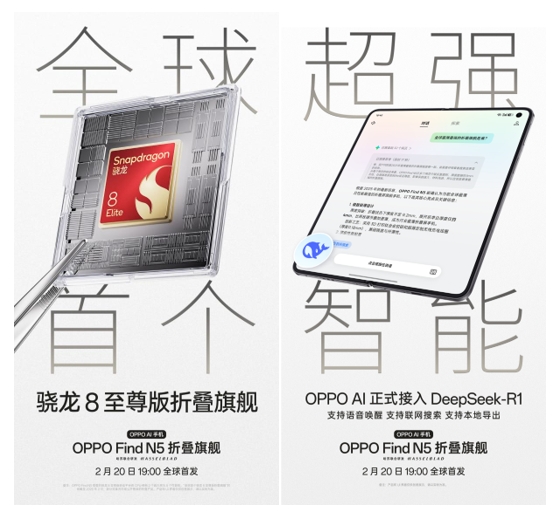

全球首款驍龍?8至尊版折疊旗艦,OPPO Find N5搭載冰川電池續(xù)航領先

創(chuàng)意電子采用Cadence數(shù)字解決方案完成首款臺積電N3制程芯片及首款AI優(yōu)化的N5制程設計

創(chuàng)意電子采用Cadence數(shù)字解決方案完成首款臺積電N3制程芯片及首款AI優(yōu)化的N5制程設計

評論