現(xiàn)場(chǎng)可編程門(mén)陣列 (FPGA) 以加速人工智能/機(jī)器學(xué)習(xí)應(yīng)用而聞名,但它是如何在 FPGA 中實(shí)現(xiàn)的,有哪些不同的方法?讓我們探索工程師的設(shè)計(jì)空間。

人工智能 (AI) 是云和邊緣應(yīng)用程序中的熱門(mén)話題。在許多情況下,人工智能可以實(shí)現(xiàn)更安全、更高效和安全的系統(tǒng)。人工智能已經(jīng)存在很長(zhǎng)時(shí)間了,它于 1956 年由約翰·麥卡錫 (John McCarthy) 在第一次人工智能會(huì)議召開(kāi)時(shí)首次使用。雖然幾十年來(lái)進(jìn)行了大量研究,但僅在最近 5 到 10 年,人工智能系統(tǒng)才從實(shí)驗(yàn)室和研究轉(zhuǎn)移到產(chǎn)品路線圖和產(chǎn)品中。

在云和邊緣環(huán)境中,部署最廣泛的 AI 形式之一是機(jī)器學(xué)習(xí) (ML)。機(jī)器學(xué)習(xí)是對(duì)計(jì)算機(jī)算法的研究,它允許計(jì)算機(jī)程序通過(guò)經(jīng)驗(yàn)自動(dòng)改進(jìn)。這方面的一個(gè)例子是為 ML 網(wǎng)絡(luò)提供帶有標(biāo)簽的圖像數(shù)據(jù)集。機(jī)器學(xué)習(xí)算法識(shí)別圖像的特征和元素,以便在輸入新的未標(biāo)記的、以前未見(jiàn)過(guò)的圖像時(shí),ML 算法確定圖像包含任何已學(xué)習(xí)特征和元素的可能性。可以訓(xùn)練此類 ML 算法來(lái)檢測(cè)圖像中的對(duì)象、處理語(yǔ)音中的關(guān)鍵字以及分析傳感器數(shù)據(jù)的異常情況。典型應(yīng)用包括視覺(jué)引導(dǎo)機(jī)器人、車輛自主操作以及工業(yè)和安全關(guān)鍵系統(tǒng)的預(yù)測(cè)。

因此,ML 學(xué)習(xí)算法分為兩個(gè)要素,第一個(gè)是針對(duì)訓(xùn)練數(shù)據(jù)集對(duì)網(wǎng)絡(luò)進(jìn)行訓(xùn)練。第二個(gè)是訓(xùn)練網(wǎng)絡(luò)領(lǐng)域的部署,這些元素分別稱為訓(xùn)練和推理。訓(xùn)練準(zhǔn)確的模型需要一個(gè)帶標(biāo)簽的大型數(shù)據(jù)集,并且通常在基于云的 GPU 上執(zhí)行以加速訓(xùn)練過(guò)程。設(shè)計(jì)工程師可以跨從 MCU 到 GPU 和 FPGA 的一系列技術(shù)部署訓(xùn)練有素的網(wǎng)絡(luò)。

在 FPGA 中嵌入 AI

幾個(gè)非常流行的框架——Caffe、TensorFlow。和 Pytorch——幫助訓(xùn)練和部署 AI/ML 系統(tǒng)。這些框架用于網(wǎng)絡(luò)定義、訓(xùn)練和推理。

許多基于邊緣的人工智能系統(tǒng)的關(guān)鍵要素之一是能夠在確定的時(shí)間范圍內(nèi)執(zhí)行推理。例如,自動(dòng)駕駛汽車必須快速檢測(cè)車輛、障礙物和行人以防止碰撞。這需要一個(gè)既響應(yīng)又確定的解決方案,響應(yīng)是因?yàn)閭鞲衅鲾?shù)據(jù)必須以最小延遲快速處理,確定是因?yàn)槊總€(gè)輸入的響應(yīng)時(shí)間必須相同并且不依賴于系統(tǒng)操作條件或資源使用,例如,使用共享 DDR 內(nèi)存會(huì)減慢響應(yīng)時(shí)間。

由于響應(yīng)性和確定性的要求,基于邊緣的解決方案的開(kāi)發(fā)人員通常以 FPGA 或基于異構(gòu) SoC 的解決方案為目標(biāo)。這些為開(kāi)發(fā)人員提供了可編程邏輯,是實(shí)現(xiàn)機(jī)器學(xué)習(xí)網(wǎng)絡(luò)的理想選擇,因?yàn)樗牟⑿刑匦灾С猪憫?yīng)式應(yīng)用程序和非常確定的解決方案。

在可編程邏輯中實(shí)現(xiàn) ML 推理時(shí),可以采用兩種方法。在使用浮點(diǎn)數(shù)學(xué)開(kāi)發(fā)和訓(xùn)練神經(jīng)網(wǎng)絡(luò)時(shí),無(wú)論采用哪種方法,F(xiàn)PGA 或異構(gòu) SoC 中的實(shí)現(xiàn)通常都使用定點(diǎn)實(shí)現(xiàn)。從浮點(diǎn)數(shù)到定點(diǎn)數(shù)的轉(zhuǎn)換過(guò)程稱為量化,推理精度會(huì)略有下降;然而,對(duì)于大多數(shù)應(yīng)用程序,可以使用量化的權(quán)重和激活來(lái)執(zhí)行額外的訓(xùn)練以恢復(fù)準(zhǔn)確性。

第一種方法直接在可編程邏輯中實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)。為推理訓(xùn)練的權(quán)重被加載到網(wǎng)絡(luò)中。這可以在運(yùn)行時(shí)或在設(shè)計(jì)的編譯/綜合期間實(shí)現(xiàn)。

這些神經(jīng)網(wǎng)絡(luò)的一個(gè)例子是 AMD-Xilinx FINN 網(wǎng)絡(luò),它可用于在 FPGA 中實(shí)現(xiàn)量化神經(jīng)網(wǎng)絡(luò)。這些量化神經(jīng)網(wǎng)絡(luò)被實(shí)現(xiàn)為具有二進(jìn)制權(quán)重和兩位激活的量化神經(jīng)網(wǎng)絡(luò)。

有了量化神經(jīng)網(wǎng)絡(luò),神經(jīng)網(wǎng)絡(luò)可以在 FPGA 中實(shí)現(xiàn),資源更少,因?yàn)椴恍枰獠?DDR 或 SoC 支持。使該方法成為空間、組件和成本非常寶貴的受限開(kāi)發(fā)的理想選擇。雖然它需要更多的專業(yè)知識(shí)才能集成到整體解決方案中,但它可能非常有效。可能使用此類方法的典型示例可能是工業(yè)機(jī)械的預(yù)測(cè),例如軸承磨損或振動(dòng)等。

在 FPGA 邏輯中使用神經(jīng)網(wǎng)絡(luò)直接實(shí)現(xiàn)的替代方法是使用高度專業(yè)化的神經(jīng)網(wǎng)絡(luò)加速器。神經(jīng)網(wǎng)絡(luò)加速器在可編程邏輯中實(shí)現(xiàn),并與具有高帶寬鏈路的 DDR 存儲(chǔ)器以及異構(gòu) SoC 中的專用處理器緊密耦合。

在使用神經(jīng)網(wǎng)絡(luò)加速器的應(yīng)用程序中,它們由軟件應(yīng)用程序提供網(wǎng)絡(luò)和權(quán)重/激活和偏差。因此,這使得 ML 推理更容易集成到整個(gè)應(yīng)用程序中。神經(jīng)網(wǎng)絡(luò)加速器的一個(gè)例子是 AMD-Xilinx 深度學(xué)習(xí)單元,它可以與 Pytorch、Caffe 和 TensorFlow 中定義的網(wǎng)絡(luò)一起工作,并為應(yīng)用程序執(zhí)行所有量化、再訓(xùn)練和程序生成。這樣可以更輕松地集成到正在開(kāi)發(fā)的應(yīng)用程序中。這種方法的典型應(yīng)用是基于視覺(jué)的高性能應(yīng)用,例如視覺(jué)引導(dǎo)機(jī)器人、智能城市解決方案,當(dāng)然還有提高汽車 SAE 自主水平。

最高的準(zhǔn)確性和性能來(lái)自于使用專門(mén)的神經(jīng)網(wǎng)絡(luò)加速器,并且易于集成通常提供更好的整體解決方案。因此,這種方法被多家供應(yīng)商用于他們的 AI 解決方案。這種方法更容易與更高級(jí)別的軟件框架和抽象堆棧集成,這是利用整體性能的關(guān)鍵,因?yàn)?AI 通常只是整體解決方案的一小部分(但很重要)。

最后的想法

很多時(shí)候,選擇哪種解決方案取決于最終應(yīng)用,即使 AI 可能是主要的營(yíng)銷元素。在現(xiàn)實(shí)世界中,人工智能通常只是整個(gè)解決方案的一小部分,因?yàn)閭鞲衅?a target="_blank">接口、預(yù)處理、執(zhí)行器驅(qū)動(dòng)和構(gòu)成解決方案的其他元素也會(huì)有自己的限制和要求。

可編程邏輯使開(kāi)發(fā)人員能夠構(gòu)建具有響應(yīng)性和確定性的 AI/ML 解決方案。通過(guò)將這些解決方案與行業(yè)標(biāo)準(zhǔn)框架相結(jié)合,開(kāi)發(fā)人員可以使云和邊緣 AI/ML 應(yīng)用程序更安全、更高效、更安全。

審核編輯黃昊宇

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

614001

發(fā)布評(píng)論請(qǐng)先 登錄

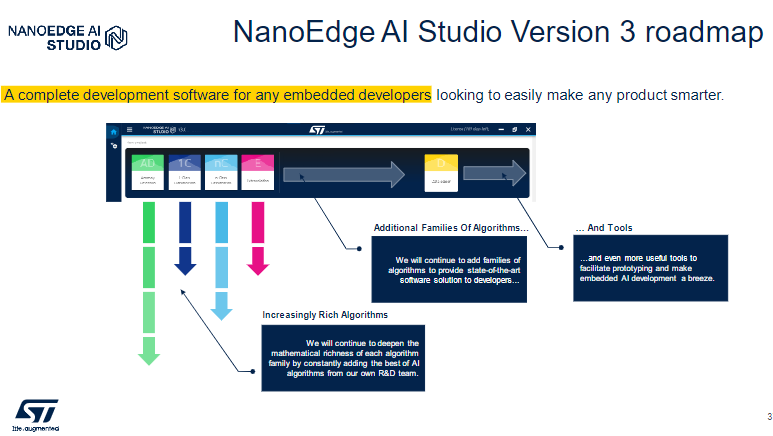

NanoEdge AI Studio 面向STM32開(kāi)發(fā)人員機(jī)器學(xué)習(xí)(ML)技術(shù)

AI和ML如何重塑電子制造業(yè)

Nordic nRF54 系列芯片:開(kāi)啟 AI 與物聯(lián)網(wǎng)新時(shí)代?

Raspberry Pi Pico 2 上實(shí)現(xiàn):實(shí)時(shí)機(jī)器學(xué)習(xí)(ML)音頻噪音抑制功能

FPGA+AI王炸組合如何重塑未來(lái)世界:看看DeepSeek東方神秘力量如何預(yù)測(cè)......

當(dāng)我問(wèn)DeepSeek AI爆發(fā)時(shí)代的FPGA是否重要?答案是......

AI在芯片上的應(yīng)用:革新設(shè)計(jì)與功能

SPEC ML基準(zhǔn)測(cè)試新增模算效率指標(biāo)

FPGA在AI方面有哪些應(yīng)用

AI編程在工業(yè)自動(dòng)化設(shè)備上應(yīng)用趨勢(shì)

新思科技Foundation IP:AI芯片低功耗設(shè)計(jì)必選項(xiàng)

為AI、ML和數(shù)字孿生模型建立可信數(shù)據(jù)

芯科科技前沿的MCU+AI/ML開(kāi)發(fā)工具解決方案

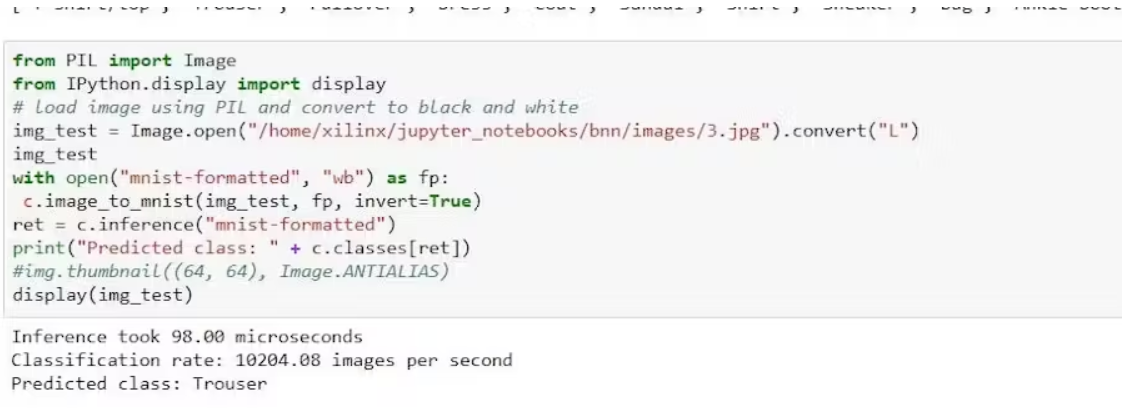

使用PYNQ訓(xùn)練和實(shí)現(xiàn)BNN

在 FPGA 上實(shí)施 AI/ML 的選項(xiàng)

在 FPGA 上實(shí)施 AI/ML 的選項(xiàng)

評(píng)論