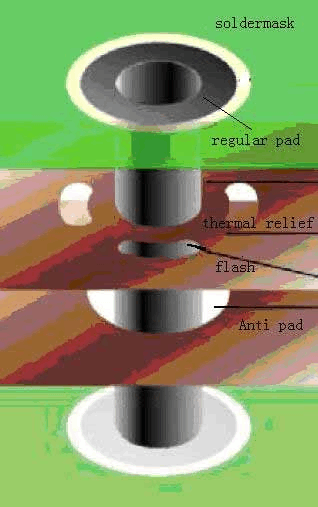

一.焊盤大小

焊盤中心孔要比元件引線直徑稍大一些,焊盤太大易形成虛焊。焊盤外徑D一般不小于 (d+1.2mm),其中d為引線徑。對(duì)高密度的數(shù)字電路,焊盤最小直徑可取 (d+1.0mm)。

二.印刷電路板電路的抗干擾措施

1.電源線設(shè)計(jì)

盡量加粕電源線寬度,減少環(huán)路電陽(yáng)。同時(shí),使電源線、地線的走向和數(shù)據(jù)傳遞的方向一致,這樣有助干增強(qiáng)抗噪聲能力

2.地線設(shè)計(jì)

數(shù)字地與模擬地分開。低頻電路的地應(yīng)盡量采用單點(diǎn)并聯(lián)接地,實(shí)際布線有困難時(shí)可部分串聯(lián)后再并聯(lián)接地。高頻電路宜采用多點(diǎn)電聯(lián)接地,地線應(yīng)短而粗,高頻元件周圍盡量用柵格狀的大面積銅箔.

接地線應(yīng)盡量加粗。若接地線用很細(xì)的線條,則接地電位隨電流的變化而變化,使抗噪聲性能降低。因此應(yīng)將接地線加粗,使它能通過三倍于印制板上的允許電流。如有可能,接地線應(yīng)在2~3mm以上

只由數(shù)字電路組成的印制板,其接地電路構(gòu)成閉環(huán)能提高抗噪聲能力.

三.去耦電容配置

電源輸入端跨接10 ~ 100uF的電解電容器。如有可能,接100uF以上的更好原則上每個(gè)集成電路芯片都應(yīng)布置一個(gè)0.01pF的瓷片電容,如遇印制板空隙不夠,可每4~8個(gè)芯片布置一個(gè)1~ 10pF的鉅電容對(duì)于抗噪能力弱、關(guān)斷時(shí)電源變化大的元件,如RAM、ROM存儲(chǔ)元件,應(yīng)在芯片的電源線和地線之間接入去糖電容。電容引線不能太長(zhǎng),尤其是高頻旁路電容不能有引線。

在印制板中如有接觸器、繼電器、按鈕等元件,操作它們時(shí)會(huì)產(chǎn)生較大火花放電,必須采用RC電路來吸收放電電流。一般R取1~2k,C取2.2 ~ 47uF。

CMOS的輸入陽(yáng)抗很高,目易受感應(yīng),因此在使用時(shí)對(duì)不使用的端口要接地或接正電源.

四、各元件之間的接線

印刷電路中不允許有交叉電路,對(duì)于可能交叉的線條,可以用“鉆”、“繞”兩種辦法解決。同一級(jí)電路的接地點(diǎn)應(yīng)盡量靠近,并且本級(jí)電路的電源濾波電容也應(yīng)接在該級(jí)接地點(diǎn)上總地線必須嚴(yán)格按”高頻一中頻一低頻”逐級(jí)按”弱電到強(qiáng)電”的順序排列原則,不可隨便翻來覆去亂接。在使用IC座的場(chǎng)合下,一定要特別注意IC座上定位槽放置的方位是否正確,并注意各個(gè)IC腳位置是否正確。

審核編輯 黃昊宇

-

電路

+關(guān)注

關(guān)注

173文章

6022瀏覽量

174374 -

元件

+關(guān)注

關(guān)注

4文章

1065瀏覽量

37429 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3501瀏覽量

5223

發(fā)布評(píng)論請(qǐng)先 登錄

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

【PCB】四層電路板的PCB設(shè)計(jì)

104條關(guān)于PCB布局布線的小技巧

PCB可制造性設(shè)計(jì):開啟高效生產(chǎn)的鑰匙

峰值電流模式降壓LED驅(qū)動(dòng)器應(yīng)用的環(huán)路響應(yīng)考慮

高速電路PCB的EMC設(shè)計(jì)考慮

飛凌 Elfboard硬件分享-高速 PCB 設(shè)計(jì)需考慮因素

基于熱性能的NIS(V)3071 PCB設(shè)計(jì)考慮因素

影響smt價(jià)格的因素有哪些?

天線PCB布局的設(shè)計(jì)考慮因素是什么?

PCB電源設(shè)計(jì)需要考慮的九大因素!

PCB布線時(shí)應(yīng)考慮的因素

PCB布線時(shí)應(yīng)考慮的因素

評(píng)論