摩爾定律在工藝復雜度和經濟高成本雙重壓力下步履蹣跚,伴隨疫情的全球形勢變化又給整個半導體行業供應鏈帶來巨大的壓力。在技術和環境的雙重限制下,3D-IC從發明之初錦上添花的技術晉身顯學,被無數企業視作在現有環境下提高系統集成度和全系統性能的必不可少的解決方案。

不知不覺間,行業文章和會議開始言必稱chiplet —— 就像曾經的言必稱AI一樣。這種熱度對于3D-IC的從業人員,無論是3D-IC制造、EDA、還是3D-IC設計,都是好事。但在我們相信3D-IC之路是Do Right Things的同時,如何Do Things Right也愈發重要。

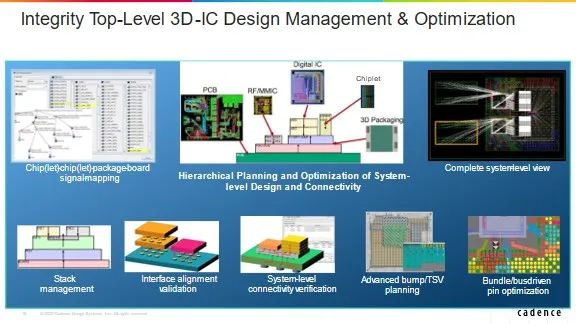

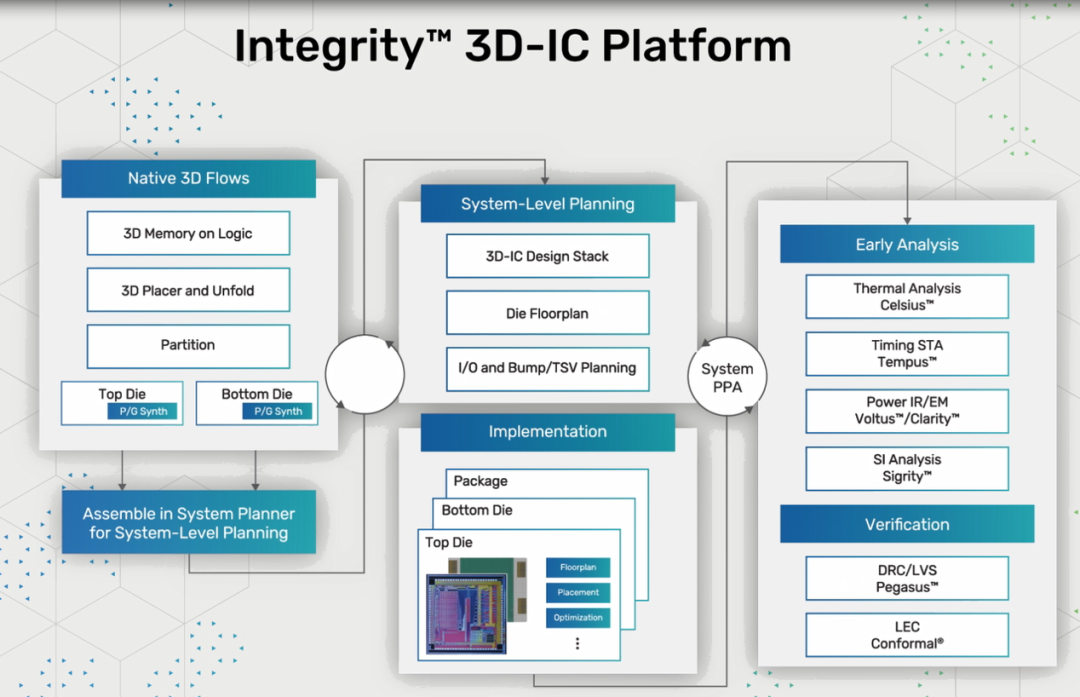

Cadence在3D-IC道路上已經探索了很多年,全新Integrity 3D-IC平臺的研發基于十幾年的探索、先進客戶的使用經驗、和先進制程流片封裝經驗,在2019年正式啟動,如今已經擁有包括3D-IC系統頂層規劃、堆疊設計、中介層繞線、自底向上、自頂向下、MoL近存運算、LoL邏輯切分等子流程在內的全套設計方法學和工具,以及包括電、熱、時序、功耗、設計規則檢查等在內的全套系統性能分析和設計簽核工具,輔以強大便捷的流程管理器和3D可視化界面,使能系統設計芯片設計者最大限度的發揮想象力高質量的實現各種復雜3D-IC設計。

在剛剛結束的TSMC開放創新平臺大會上,Cadence更是成為唯一一家獲得TSMC 3DFabric全流程(系統規劃、實現及系統級簽核)認證的合作伙伴。

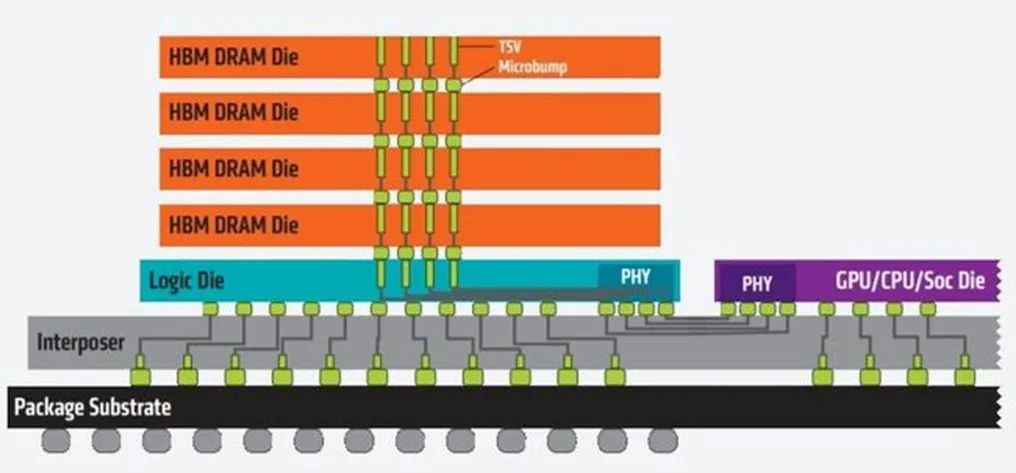

3D-IC設計不同于傳統意義上的2D設計,2D芯片經過幾十年的發展已經在設計、制造、封裝角度形成了固定的流程。而3D-IC設計中系統設計會在很大程度上被最終的流片廠封裝廠甚至TSV/Bump提供商的具體制造方案影響。這也是為什么傳統3D-IC設計是由封裝團隊而不是設計團隊或者完成3D系統設計或者制定出對每個晶粒的約束條件,并且由設計團隊參考封裝約束條件實現芯片的物理設計。但伴隨著3D-IC從一種可選的技術方案走向集成度或系統性能驅動的必選方案,如何提高原封裝驅動的設計流程的自動化以及如何從系統角度得到全系統性能、功耗、面積、散熱的最優化設計已經變成的越來越重要。并且在此基礎上還要考慮不同3D制造、封裝方案對系統設計的影響。再考慮到設計不同階段和不同步驟的設計意圖交互和數據交互以及ECO需求,這一切都不是原有基于不同設計團隊的不同點工具所能輕松解決的。

在過去的幾個月里,我們為大家推出了一系列的文章,涵蓋了通過Integrity 3D-IC平臺的從系統規劃、中介層布線自底向下實現、早期三維布圖綜合及層次化設計Memory-on-Logic堆疊實現三維寄生參數提取和靜態時序分析等步驟和流程在內的全流程解決方案:

3D-IC設計之如何實現高效的系統級規劃

3D-IC設計之中介層自動布線

3D-IC設計之自底向上實現流程與高效數據管理

3D-IC設計之早期三維布圖綜合以及層次化設計

3D-IC設計之Memory-on-Logic堆疊實現流程

3D-IC設計之寄生抽取和靜態時序分析

3D-IC設計之系統級版圖原理圖一致性檢查

該方案可以在最大限度上提高設計在不同3D-IC制造方案的可遷移性,從而最大程度減少芯片設計團隊對于3D-IC先進封裝技術的學習成本,封裝設計團隊對芯片設計技術的學習成本,系統多物理驗證和簽核團隊對芯片設計和封裝設計的學習成本,從而使團隊中的每個角色專注于自己所熟悉的領域,更快的實現3D-IC產品全系統的設計收斂和簽核,通過傳統工藝實現更高系統集成度,或在先進工藝節點或異構集成系統上進一步提高數據帶寬、吞吐率和傳統的性能、功耗、面積等綜合系統指標。

Integrity 3D-IC平臺的推出只是開始,我們期待越來越多的設計者借助Integrity 3D-IC將兩維設計平面拓展到三維設計空間,來實現5G/6G通訊、人工智能、數據中心、高性能移動處理器、汽車電子等越來越先進的創新需求,為人類的生產生活開創更加美好的未來!

如您需了解Cadence 3D-IC Integrity 平臺的更多內容,請點擊“閱讀原文” 注冊申請我們的Integrity 3D-IC資料包。

Integrity 3D-IC資料包:

-Cadence Integrity 3D-IC 平臺 產品手冊

-Cadence Integrity 3D-IC 平臺PPT資料包

注冊成功且通過Cadence審核的用戶可獲得完整版PPT資料。審核通過后Cadence會將PPT發送至您的郵箱,提供您的公司郵箱地址通過審核的幾率更大哦!

Cadence Integrity 3D-IC 平臺提供了一個高效的解決方案,用于部署 3D 設計和分析流程,以實現強大的硅堆疊設計。該平臺是 Cadence 數字和簽核產品組合的一部分,支持 Cadence 公司的智能系統設計戰略(Intelligent System Design) ,旨在實現系統驅動的卓越 SoC 芯片設計。

審核編輯 :李倩

-

IC設計

+關注

關注

38文章

1346瀏覽量

105217

原文標題:3D-IC未來已來

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

西門子利用AI來縮小行業的IC驗證生產率差距

Cadence攜手臺積公司,推出經過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發展

西門子Innovator3D IC平臺榮獲3D InCites技術賦能獎

基于TSV的3D-IC關鍵集成技術

3.5D封裝來了(上)

3.5D封裝來了(下)

揭秘3D集成晶圓鍵合:半導體行業的未來之鑰

3D打印技術應用的未來

剖析 Chiplet 時代的布局規劃演進

Samsung 和Cadence在3D-IC熱管理方面展開突破性合作

西門子推出Innovator3D IC,用于 3D IC 設計、驗證和制造的多物理場集成環境

西門子推出Calibre 3DThermal軟件,持續布局3D IC熱分析

借助云計算加速3D-IC可靠性的機械應力模擬

3D-IC未來已來

3D-IC未來已來

評論