知道明德?lián)P科教是一個偶然,但后來耐心看完明德?lián)P知識大串講系列視頻卻是一個必然。因為做得用心,所以看得放心。

本人是一個純FPGA小白,就連FPGA這個名詞我都是最近才知道,所以如果你也正想入門學(xué)習(xí)FPGA的話,請耐心看下去吧,相信你看完絕對不會后悔。

因為最近參加了一個集成電路類的比賽,需要用FPGA進(jìn)行功能的實現(xiàn),無奈我們專業(yè)目前還沒有開設(shè)這門課,于是就只能自己開始著手自學(xué)了。經(jīng)過我們老師的推薦,我第一次了解到了明德?lián)P科教,了解到這樣一個這么純粹做技術(shù)和教育的機構(gòu),免費看完潘老師知識大串講系列視頻后頗有感觸,下面我來向大家分享一下作為一個FPGA小白的學(xué)習(xí)經(jīng)歷吧!

首先大家可能會疑問學(xué)習(xí)FPGA需要什么基礎(chǔ)知識,實話告訴你,基本不需要。我在學(xué)習(xí)FPGA之前除我們專業(yè)開設(shè)的模擬電子技術(shù)課外,自己只是自學(xué)了一下51單片機開發(fā)和數(shù)字電子技術(shù)的一些最簡單基礎(chǔ)的東西,最后發(fā)現(xiàn)用到的就是一個二進(jìn)制和一些基本的門級電路知識,其次就是一種編程思維的培養(yǎng),但我相信作為想學(xué)FPGA的你應(yīng)該也多少具備一些這類知識吧。如果沒有的話不妨簡單看看吧。

視頻的六個部分

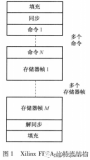

知識大串講系列視頻一共由六個部分組成,分別是:學(xué)習(xí)誤區(qū)、FPGA知識大串講、組合邏輯、D觸發(fā)器、時序邏輯和FPGA時序。每個視頻針對性地講一個小點,條理清楚,邏輯清晰,由淺入深,循序漸進(jìn),非常適合新手入門。這套視頻不像其他有些視頻一樣很冗長,讓人一看到視頻的時長就望而卻步,這套視頻最長的不過半個小時,最短的也就五分半,讓人看著不會覺得很枯燥。日常刷一個小視頻的時間而已,而且還能學(xué)會很多東西,何樂而不為呢?

明德?lián)P知識大串講系列視頻的知識體系

大家可能還會疑惑一個問題:在這么短的時間內(nèi)真的能學(xué)到知識嗎?

誠然,在如此短的時間內(nèi)想要掌握一門技術(shù)有些不太實際,但我看完視頻的經(jīng)歷告訴我,這套視頻只要你認(rèn)真看,理解潘老師講的每一個細(xì)節(jié),看不明白的地方就反復(fù)看看,再結(jié)合自己的理解思考一下,有些問題你就會恍然大悟。而且視頻中有些言語非常地道幽默,所以也很讓人容易理解接受。另外潘老師每個視頻只針對一個小點進(jìn)行講解和分析,所以也很容易聽懂,當(dāng)然大家也不要有會聽不懂的顧慮了。當(dāng)然,對于能力比較強的初學(xué)者來說1.5倍速播放可能更適合你!

大家都知道,一個工程的好壞不在于代碼量的多少,不是說實現(xiàn)一個功能用的代碼越少越好。評價一個工程的好壞要看綜合出來的電路,如果一個工程所在效率滿足的前提下,所調(diào)用的資源最少、可維護(hù)性高、拓展性強、代碼精簡便于閱讀,那么這就是一個好的工程。關(guān)于代碼,潘老師在視頻中也詳細(xì)教了一些方法和思維,以下是我學(xué)習(xí)后的一些思考和總結(jié)。

不要試圖用軟件思維去編寫代碼。因為軟件思維是在單片機編寫程序時運用廣泛的一種思維,主要通過一些串行或并行輸出的代碼去控制單片機處理一些問題,這樣就會涉及到一些諸如延時和初始化這樣的代碼,但在FPGA中則不一樣,在FPGA中是電路的反應(yīng),只要一通電就開始執(zhí)行。在FPGA中也沒有for循環(huán)和while循環(huán)、高阻態(tài)和不定態(tài)的說法。關(guān)于時序的功能都是通過時鐘來實現(xiàn)的。FPGA是使用Verilog語言進(jìn)行編寫的,Verilog中文翻譯又叫硬件描述語言,不是一種設(shè)計語言。所以我們在做一個FPGA設(shè)計之前,其實已經(jīng)有硬件的電路結(jié)構(gòu)在頭腦里面了,我們只是用Verilog語言把它描述出來而已,絕不是用Verilog設(shè)計一門電路出來,這個思維模式是完全不一樣的。

FPGA中是電路的反應(yīng)

軟件思維編寫的代碼可讀性較差,而且和硬件思維編寫的代碼比起來運行的時候更耗時。

以下是兩者實現(xiàn)一個攝像頭輸入模塊采集功能的代碼對比:

軟件思維編寫的代碼

明德?lián)P規(guī)范的代碼

可以看出,兩種思維的代碼相形見絀。用軟件思維寫出的代碼不僅結(jié)構(gòu)冗長、可讀性差,而且理解起來也比較麻煩。同樣是實現(xiàn)一個攝像頭輸入模塊采集功能,攝像頭輸入過來有三個信號:時鐘、使能和數(shù)據(jù)。數(shù)據(jù)分別用兩個字節(jié)的二進(jìn)制數(shù)的值來表示一個像素點中RGB的值,我們主要做的就是把這兩個值通過一個16bit的總線輸入到下一個模塊。軟件思維就是定義一個變量進(jìn)行加一運算,而明德?lián)P規(guī)范中就用一個取反就解決了。這只是一個簡單的例子,如果不夠明顯的話,接下來我們來看一個稍微復(fù)雜一點的例子。

現(xiàn)在我們需要實現(xiàn)一個幀頻率的計算,統(tǒng)計兩秒鐘內(nèi)輸入幀的個數(shù),然后把得到的數(shù)除以2就得到一秒鐘的幀頻率。下面我們來一起看看這個功能用兩種不同代碼實現(xiàn)的區(qū)別:

軟件思維寫出的代碼

明德?lián)P規(guī)范的代碼

大家不難看出,用軟件思維寫出的代碼不僅繁雜,理解起來也比較困難,而明德?lián)P規(guī)范的代碼則顯得更簡潔、高效,效率也是不可同日而語的。

另外我們還不難發(fā)現(xiàn)一點,潘老師和明德?lián)P規(guī)范的代碼結(jié)構(gòu)和語法非常簡單,很多語法幾乎都只是用得到了if和else這些最簡單的語句,所以我們在學(xué)習(xí)語法上其實不用花費太多的時間,這也為我們新手入門降低了很多難度,節(jié)省了很多寶貴的時間。

明德?lián)P規(guī)范的代碼結(jié)構(gòu)和語法

另外潘老師個人講課也比較有特點,雖然潘老師普通話不是特別標(biāo)準(zhǔn),但這并不影響我們對于知識和思維的學(xué)習(xí)。

潘老師研發(fā)經(jīng)驗非常豐富,曾在華為這種世界500強的公司工作過,做過很多項目的開發(fā),所以實戰(zhàn)經(jīng)驗豐富,講的很多東西實用性比較強。特別是對于我這種是抱著參加競賽的小白來說幫助很大。

我們都知道,想要提要時鐘頻率就要減小時鐘周期,但因為D觸發(fā)器和線路之間傳遞的那部分延時是由物理器件決定的跟器件的工藝和材料等因素有關(guān),我們沒辦法進(jìn)行修改,我們能做的就是對組合邏輯那部分電路的延時減到最小。這條把延時減到最小的路徑也叫關(guān)鍵路徑。

關(guān)鍵路徑

老師在一開始就講過在FPGA里面的電路是一通電就可以工作,指的是對于最基本的門電路而言的。于是老師就舉了他在海思里面做項目的一個例子:要把一個集成電路跑到2G的頻率!可想而知這需要多么小的時鐘周期,他們的方法就是把所有能拆的組合邏輯都拆成了基本的門電路,甚至連選擇器他們也不放過,只為了一步步提高頻率。就這樣一直不停地拆,直至把任何兩個寄存器之間的延時縮小到最小最小,從而達(dá)到就可以達(dá)到提高時鐘頻率的目標(biāo),這個方法也叫流水線設(shè)計。

減小時鐘周期

潘老師講課還善于聯(lián)系現(xiàn)實生活進(jìn)行分析。在講到關(guān)于狀態(tài)機的設(shè)計時,為了將狀態(tài)機設(shè)計的目和過程一目了然,于是便聯(lián)系生活講到了我們?nèi)粘I钪谐R姷淖詣邮圬洐C的設(shè)計。

自動售貨機的設(shè)計

并且還就這個例子講到了代碼設(shè)計的三段論格式,讓設(shè)計代碼顯得非常實用高效,便于分析。

自動售貨機代碼的設(shè)計

總而言之,看完整套視頻后,作為一個小白的我感覺對于FPGA有了一個大概的了解了,讓原本在門外徘徊的我慢慢地就走進(jìn)了門里。在這里常感謝明德?lián)P科教提供的這個讓我免費學(xué)習(xí)的機會。

以上就是我看完明德?lián)P知識大串講系列視頻后的一些收獲和總結(jié),希望能給同樣熱愛學(xué)習(xí)的你帶來一些啟發(fā)!也讓我們在學(xué)習(xí)FPGA的道路上共同進(jìn)步吧!

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21967瀏覽量

614245 -

單片機

+關(guān)注

關(guān)注

6063文章

44925瀏覽量

647074 -

時序邏輯

+關(guān)注

關(guān)注

0文章

39瀏覽量

9341

發(fā)布評論請先 登錄

智多晶FPGA設(shè)計工具HqFpga接入DeepSeek大模型

進(jìn)群免費領(lǐng)FPGA學(xué)習(xí)資料!數(shù)字信號處理、傅里葉變換與FPGA開發(fā)等

27個FPGA實例源代碼

基于FPGA的電子琴設(shè)計

FPGA在AI方面有哪些應(yīng)用

本人研一,做DFB激光穩(wěn)頻,目前只差FPGA ADC DAC做一個反饋系統(tǒng)

FPGA基礎(chǔ)知識及設(shè)計和執(zhí)行FPGA應(yīng)用所需的工具

FPGA加速深度學(xué)習(xí)模型的案例

FPGA做深度學(xué)習(xí)能走多遠(yuǎn)?

如何用FPGA實現(xiàn)一個通信系統(tǒng)的發(fā)射端接收機?

基于FPGA的CCD工業(yè)相機系統(tǒng)設(shè)計

一文了解FPGA比特流的內(nèi)部結(jié)構(gòu)

【學(xué)習(xí)FPGA必看】一個FPGA小白的自述

【學(xué)習(xí)FPGA必看】一個FPGA小白的自述

評論