“課堂上給大家介紹代碼規范的時候,反復強調不能出現組合邏輯環,具體就是組合邏輯所有的else語句要寫全,case語句也要寫全,但組合邏輯環到底有什么危害?下面就詳細舉例說明。”

01

—

什么是組合邏輯環?

組合邏輯反饋環路是數字同步邏輯設計的大忌,它最容易因振蕩、毛刺、時序違規等問題引起整個系統的不穩定和不可靠。組合邏輯反饋環路是二種高風險的設計方式,主要原因如下:

1.組合反饋環的邏輯功能完全依賴于其反饋環路上組合邏輯的門延時和布線延時等,如果這些傳播延時有任何改變,則該組合反饋環單元的整體邏輯功能將徹底改變,而且改變后的邏輯功能很難確定。

2.組合反饋環的時序分析是無窮循環的時序計算,綜合、實現等EDA 工具迫不得已一般必須主動割斷其時序路徑,以完成相關的時序計算。而不同的EDA工具對組合反饋環的處理方法各不相同,所以組合反饋環的最終實現結果有很多不確定因素。

3.通常的綜合工具在處理組合邏輯反饋問題時,將產生Latch,這將對時序造成許多問題。

在用Verilog HDL進行可綜合電路設計時,有很多情況都有可能產生組合邏輯環。

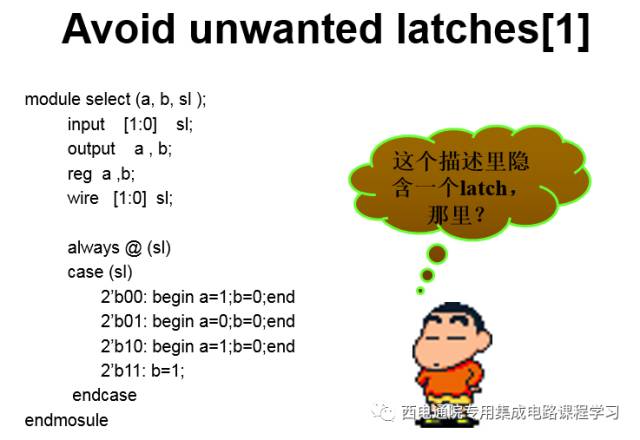

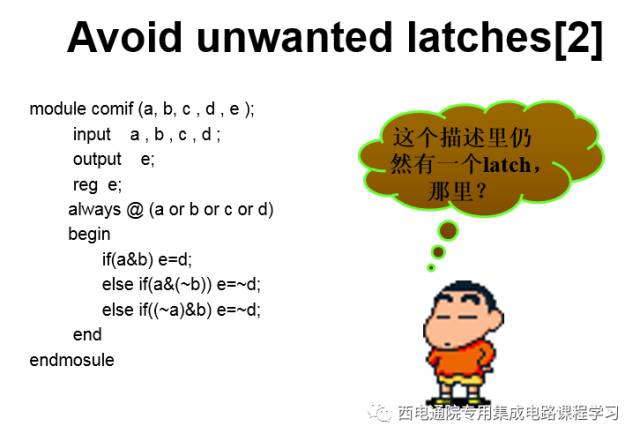

?在組合邏輯的組合進程中, 條件語句描述時應該指定所有條件下所有輸出的狀態,以避免鎖存。比如if/case語句的所有分支必須定義全部的輸出才可能避免出現鎖存。

?在設計中,應該盡量避免使用鎖存!因為鎖存要占去大量的觸發器資源,而且會對電路帶來某種不穩定的隱患。

?所謂的latch,其實質是組合電路中有反饋!反饋的形成是利用到了前一個狀態。

具體舉例如下:

總結如下:

?組合電路描述中,條件判斷語句必須指明所有條件分支情況下,被賦值信號的值。

?分支不完整,意味著電路需要在某種電平狀態下,讓被賦值的信號“保持原值”,這只能使用鎖存電路實現。

02

—

一個實例

設計代碼如下:

// **************************************************************

// COPYRIGHT(c)2015, Xidian University

// All rights reserved.

//

// IP LIB INDEX :

// IP Name :

// File name :

// Module name :

// Full name :

//

// Author : Liu-Huan

// Email : assas[email protected]

// Data :

// Version : V 1.0

//

// Abstract :

// Called by :

//

// Modification history

// -----------------------------------------------------------------

//

//

//

// *****************************************************************

// *******************

// TIMESCALE

// *******************

`timescale 1ns/1ps

// *******************

// INFORMATION

// *******************

//*******************

//DEFINE(s)

//*******************

//`define UDLY 1 //Unit delay, for non-blocking assignments in sequential logic

//*******************

//DEFINE MODULE PORT

//*******************

module TOP (

input clk ,

input rst

) ;

//*******************

//DEFINE LOCAL PARAMETER

//*******************

//parameter(s)

parameter IDLE = 5'b0_0001 ;

parameter S1 = 5'b0_0010 ;

parameter S2 = 5'b0_0100 ;

parameter S3 = 5'b0_1000 ;

parameter S4 = 5'b1_0000 ;

//*********************

//INNER SIGNAL DECLARATION

//*********************

//REGS

(* mark_debug = "true" *)reg [4:0] c_state ;

(* mark_debug = "true" *)reg [4:0] n_state ;

reg [3:0] cnt ;

(* mark_debug = "true" *) reg [3:0] led ;

//WIRES

//*********************

//INSTANTCE MODULE

//*********************

//*********************

//MAIN CORE

//*********************

always @(posedge clk or posedge rst) begin

if (rst == 1'b1) begin

cnt <= 4'b0 ;

end

else begin

cnt <= cnt+1'b1 ;?

end

end

// 三段式狀態機 驗證 第二段 if無else的異常跳轉

// 第一段 狀態轉移

always @(posedge clk or posedge rst) begin

if (rst == 1'b1) begin

c_state <= IDLE ;?

end

else begin

c_state <= n_state ;

end

end

// 第二段 計算下一狀態

always @ (*) begin

case ( c_state )

IDLE : begin

if ( cnt == 'b0 )

n_state = S1 ;

end

S1 : begin

if ( cnt == 'd2 )

n_state = S2 ;

end

S2 : begin

if ( cnt == 'd4 )

n_state = S3 ;

end

S3 : begin

if ( cnt == 'd8 )

n_state = S4 ;

end

S4 : begin

if ( cnt == 'd15 )

n_state = IDLE ;

end

default : begin

n_state = IDLE ;

end

endcase

end

// 第三段 輸出

always @(posedge clk or posedge rst) begin

if (rst == 1'b1) begin

led <= 4'b0 ;

end

else begin

case ( n_state )

IDLE : led <= 4'b0 ;

S1 : led <= 4'd1 ;

S2 : led <= 4'd2 ;

S3 : led <= 4'd3 ;

S4 : led <= 4'd4 ;

default : begin

led <= 4'd0 ; ?

end

endcase

end

end

endmodule

仿真激勵代碼如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2017/12/11 2030

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module test ;

reg clk ;

reg rst ;

initial begin

clk = 1'b0 ;

rst = 1'b1 ;

# 100

rst = 1'b0 ;

end

always # 5 clk = ~clk ;

TOP U_TOP (

.clk ( clk ) ,

.rst ( rst )

) ;

endmodule

上面組合邏輯環的代碼已經用紅色字體顯示。

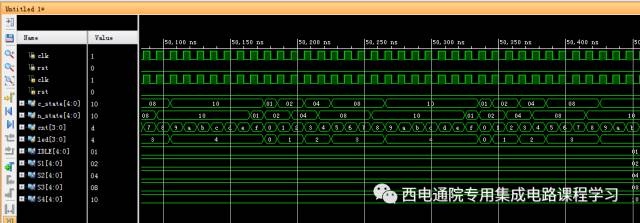

先看前仿真結果:

看不太清?讓我們再看一張圖。

狀態跳變正常,n_state[4:0]按照1、2、4、8、16、1......的順序重復跳變,沒有任何問題。

但在用FPGA工具(如vivado)進行綜合時,會報警告:

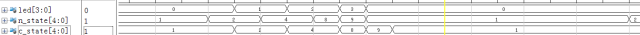

但是上板抓取信號,發現狀態機異常跳轉,如下圖所示。

此時的n_state[4:0]信號跳變狀態為:1、2、4、8、9、1......,出現了9這樣的一個狀態!

此時,水落石出!出現組合邏輯環會給電路帶來嚴重問題!

而上面的例子是顯而易見的,一眼就能看出來,還有一些組合邏輯環,是在寫代碼時不小心引入的,并且是由多個always模塊組成的,這種組合邏輯環在綜合的時候也會報warning,必須要修改掉之后才能繼續后續工作。否則,等真正上板調試時,規模稍微大點的設計如果要定位到這個錯誤估計也得花掉好幾天的時間,所以代碼規范至關重要!

03

—

組合邏輯環的好處

在實際芯片設計中,也是不允許出現組合邏輯環的。但組合邏輯環能夠減少電路邏輯資源,降低電路功耗,具有很多優點。但是其難以被靜態時序分析工具分析和計算,且難以生成功能驗證向量和自動測試圖形向量.針對此問題,很多人都提出了多種組合邏輯環轉化方法,以解決硬件描述語言以及高級語言邏輯綜合階段所面臨的組合邏輯環拆分問題。

審核編輯 :李倩

-

FPGA

+關注

關注

1644文章

22009瀏覽量

616591 -

Verilog

+關注

關注

29文章

1366瀏覽量

112059 -

eda

+關注

關注

71文章

2908瀏覽量

177293

原文標題:Verilog HDL描述的組合邏輯環在FPGA實現時到底有什么問題?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文詳解Verilog HDL

Verilog HDL描述的組合邏輯環在FPGA實現時到底有什么問題?

Verilog HDL描述的組合邏輯環在FPGA實現時到底有什么問題?

評論