應用材料公司今天舉辦了在線邏輯大師班,展示了幾種材料工程解決方案,這些解決方案通過持續改進功率、性能、面積、成本和上市時間(PPACt)實現高級邏輯擴展。

正如我的同事在最近的博客中概述的那樣,在將晶體管和互連擴展到3nm節點及更高節點時,多重挑戰阻礙了功耗和性能的提高。還存在模式可變性問題,需要新的材料工程解決方案。在這篇博客中,我將重點介紹應用材料公司如何通過基于工藝步驟協同優化和集成材料解決方案(IMS)的創新,幫助客戶實現先進邏輯的PPACt路線圖。我們還在幫助業界實施一種稱為設計技術協同優化(DTCO)的擴展技術,該技術將在新興節點中變得越來越普遍,因為它使邏輯密度擴展能夠繼續進行,即使音高擴展速度變慢。

晶體管縮放:將FinFET擴展到5nm以上;啟用門全方位拐點

FinFET路線圖有三個重要的技術挑戰:翅片彎曲、高k金屬柵極(HKMG)和接口關鍵尺寸縮放以及源極/漏極電阻。應用材料公司正在使用新材料和工藝協同優化的組合來幫助解決每個問題。

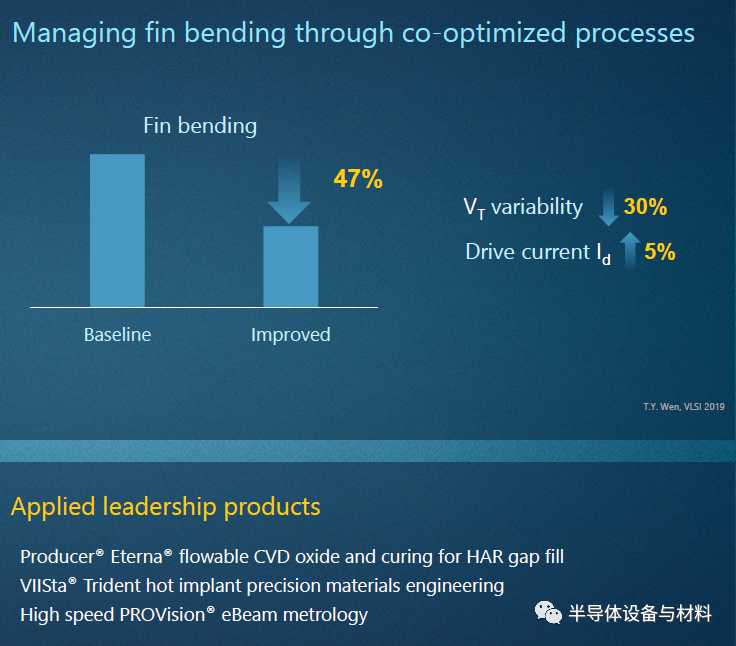

制造過程中的翅片彎曲會導致可變性,從而降低性能并降低電源效率。為了緩解這種情況,我們開發了協同優化的材料工程解決方案,包括用于翅片隔離的可流動氧化物,以及共同優化的離子注入和退火步驟,所有這些都使用應用材料公司的PROVision eBeam測量和檢測技術進行監控。使用這些技術,我們可以實現高、直、高長寬比的翅片,具有更高的均勻性,從而將閾值電壓變化率降低30%,并將驅動電流增加5%以上(見圖1)。

圖 1:應用材料公司共同優化的工藝可減少翅片彎曲,從而將閾值電壓變異性降低 30%,驅動電流增加 5% 以上。

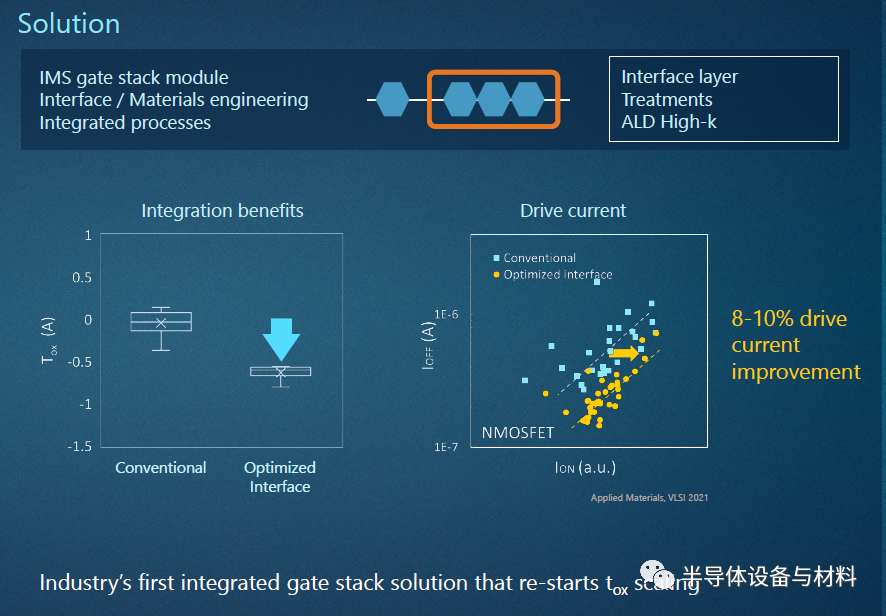

兩個HKMG邏輯元件——接口和高k值層——是提高晶體管驅動電流的關鍵。但是,自14nm節點以來,這兩層都沒有擴展,從而造成了性能瓶頸。為了解決這個問題,應用材料公司開發了一種新的集成材料解決方案(IMS),該解決方案結合了真空中的關鍵工藝步驟,以實現更高程度的界面工程和調整。使用IMS,我們展示了一種新的集成柵極堆棧,該堆棧使等效氧化物厚度縮放能夠恢復,并將驅動電流提高8%至10%(見圖2)。

圖 2:使用集成材料解決方案,應用材料公司展示了一種新的集成柵極堆棧,該堆棧可恢復等效氧化物厚度縮放,并將驅動電流提高 8% 至 10%。

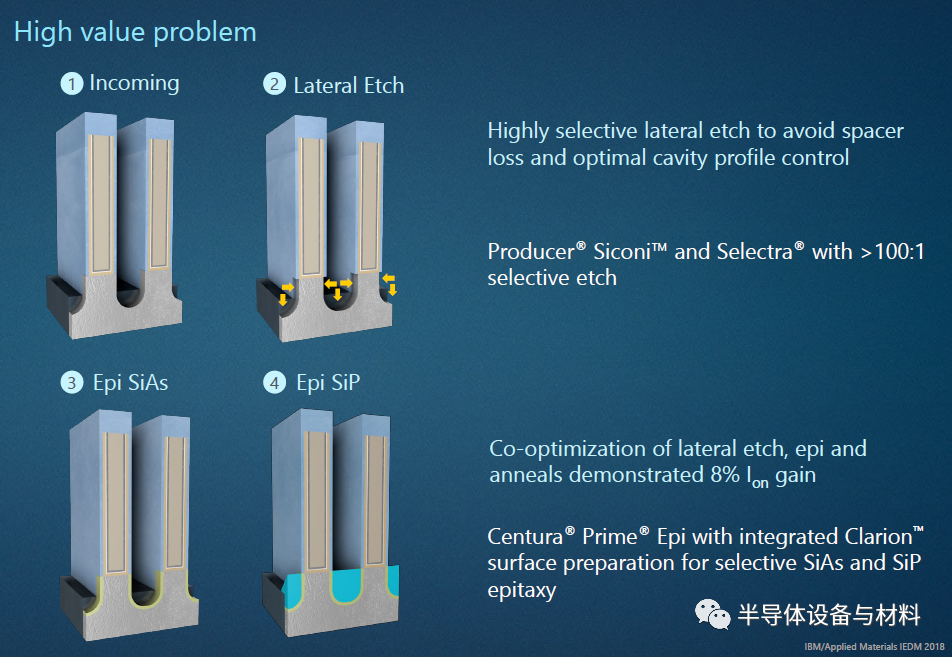

在晶體管的源極/漏極電阻模塊中,縮放使每個節點的接觸面積減少了25%,導致接觸電阻不可持續地增加。為了解決這個問題,應用材料公司開發了一種新的協同優化工藝技術,可以最大限度地利用可用于應變工程的區域(見圖3)。該解決方案包括橫向蝕刻,使嵌入式源極-漏極應力源更靠近通道。此外,我們還開發了一種新型選擇性砷化硅(SiAs)外延層。新的材料和材料工程技術降低了電阻,并將驅動電流提高了8%。

圖 3:應用材料公司的源極/漏極電阻解決方案包括共同優化的蝕刻、外延和退火,驅動電流增益為 8%。

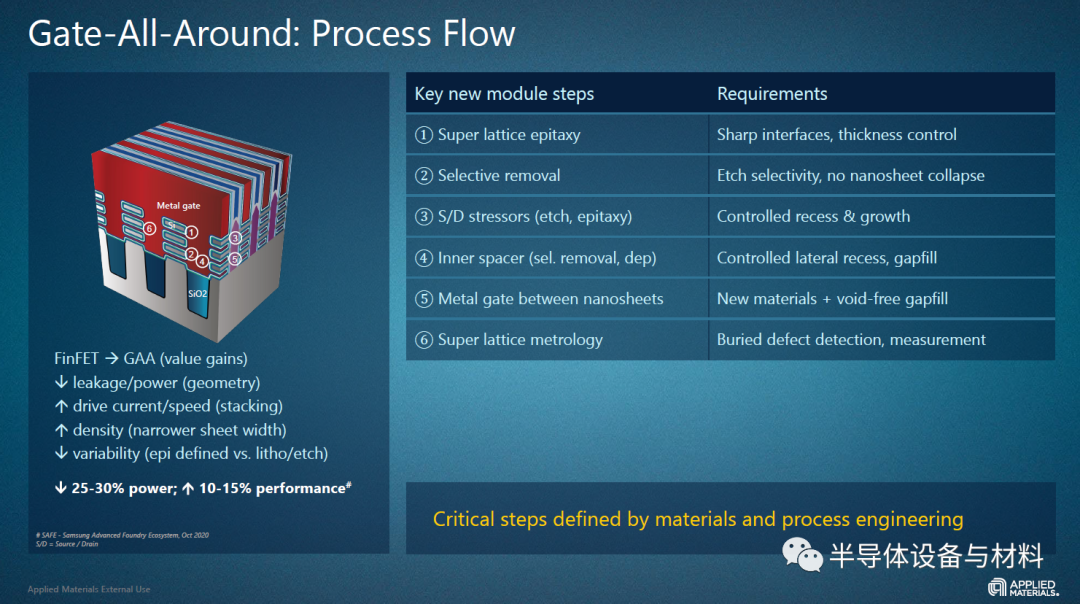

隨著行業從 FinFET 過渡到柵極全能 (GAA) 晶體管架構,進一步提高性能和功耗,材料工程創新將變得更加重要(見圖 4)。在GAA中,晶體管通道方向從垂直轉向水平,柵極在所有四個側面而不是三個側面圍繞通道。控制通道厚度對于性能和功耗至關重要:在從 FinFET 到 GAA 的過程中,通道厚度控制從高而薄的翅片的光刻和蝕刻轉向 GAA 中的外延和選擇性去除,因為它們提供了高度可控的增長和減少的可變性。GAA晶體管還需要通道之間的內部墊片,適當的工程設計有助于降低電容。墊片采用高度可控的選擇性蝕刻和間隙填充工藝制成。使用 eBeam 進行計量有助于確保新結構正確、最佳地形成,從而實現 10% 至 15% 的預期性能提升和 25% 至 30% 的功率提升。

Epi、選擇性去除和電子束計量是應用材料公司的領導領域,我們已經在開發協同優化的工藝,以幫助加速為客戶提供 GAA 解決方案。因此,與FinFET相比,我們預計GAA中每10萬WSPM(每月晶圓啟動)將獲得10億美元的增量收入。

圖 4:隨著行業向柵極全能 (GAA) 晶體管架構過渡,材料工程創新將變得更加重要。

互連擴展:新的集成材料解決方案將過孔阻力降低 50%

互連器件消耗近三分之一的功率,占電阻電容(RC)延遲的70%以上。與每個工藝節點收縮而性能提高的晶體管不同,互連線在收縮時會遇到更高的電阻,這反過來又降低了性能并增加了功耗。如果沒有突破,通過電阻的互連將從7nm到3nm節點增加10倍,從而抵消了晶體管縮放的好處。

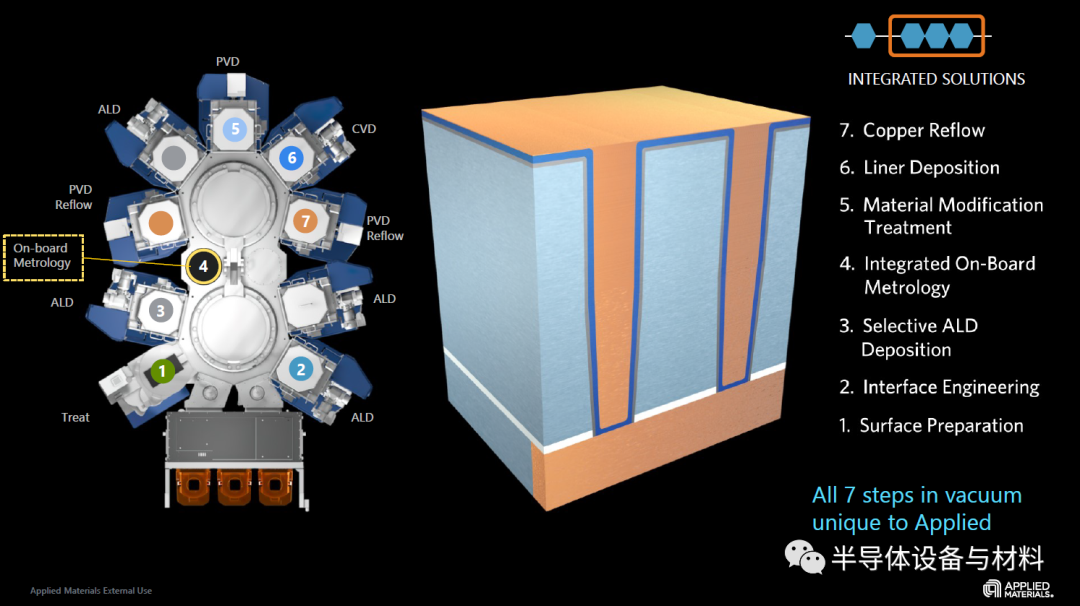

為了解決這一挑戰,應用材料公司今天推出了一項材料工程方面的突破,稱為Endura銅阻隔種子IMS。這款卓越的集成材料解決方案在高真空下將七種不同的工藝技術結合在一個系統中:ALD、PVD、CVD、銅回流焊、表面處理、界面工程和計量(見圖5)。該解決方案通過將保形原子層沉積替換為選擇性原子層沉積,消除了過孔接口處的高電阻率勢壘。它還包括銅回流焊技術,可在狹窄的特征中實現無空隙填充。該解決方案將過孔觸點接口處的電阻降低了多達 50%,從而提高了芯片性能和功耗。

圖 5:新型 Endura 銅阻隔種子 IMS 在高真空下將七種不同的工藝技術結合在一個系統中,以提高芯片性能和功耗。

通過材料工程和 DTCO 的創新解決模式變異性問題

由于EUV光刻技術與多圖案技術結合使用以創建更細的線條,因此在較小的節點上,圖案可變性的問題變得越來越成問題。我們想要的不是筆直、光滑的邊緣,而是越來越粗糙和不均勻。在過去,這并不是一個大問題,因為特征要大得多,邊緣粗糙度的比例更小。但是,隨著我們繼續使用EUV進行擴展,特征和邊緣粗糙度變得相當,從而導致隨機缺陷,例如開路和短路。

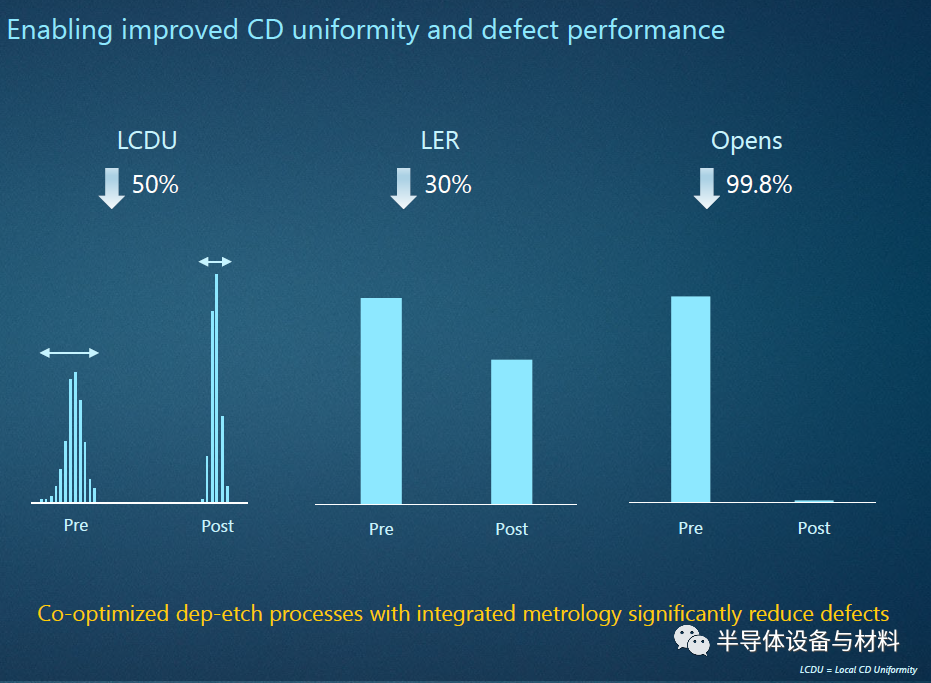

在多圖案化中,該行業通常使用旋入式電介質和爐子步驟將光刻圖案轉移到器件層中。為了減少隨機誤差,我們正在用高質量的CVD材料替換旋裝電介質,該材料與我們的Sym3蝕刻系統共同優化,該過程由我們的PROVision eBeam測量系統監控。事實上,我們將CVD集成到我們的蝕刻室中。一旦具有粗糙特征的晶圓進入腔室,我們就會選擇性地沉積一層薄薄的CVD材料,調整工藝,在寬開口上沉積更多材料,在小開口上沉積更少的材料,從而校正相鄰線之間的距離。

沉積后,我們使用經過特殊調整的蝕刻模式,該模式蝕刻小特征的速度快于大特征,再次減少了差異。因此,通過將CVD與我們先進的蝕刻技術共同優化,我們可以平滑線條并消除許多隨機缺陷。我們還使用電子束測量技術來快速測量這些微小特征的尺寸變化。事實證明,這種協同優化的解決方案可以使特征尺寸的局部變化減少50%,線路邊緣粗糙度降低30%,開路缺陷減少近100%,從而實現持續的邏輯縮放和健康的器件良率(見圖6)。

圖 6:應用材料公司 CVD 與先進蝕刻技術的共同優化消除了許多隨機缺陷,從而顯著降低了局部臨界尺寸均勻性 (LCDU)、線邊粗糙度 (LER) 和開路缺陷。

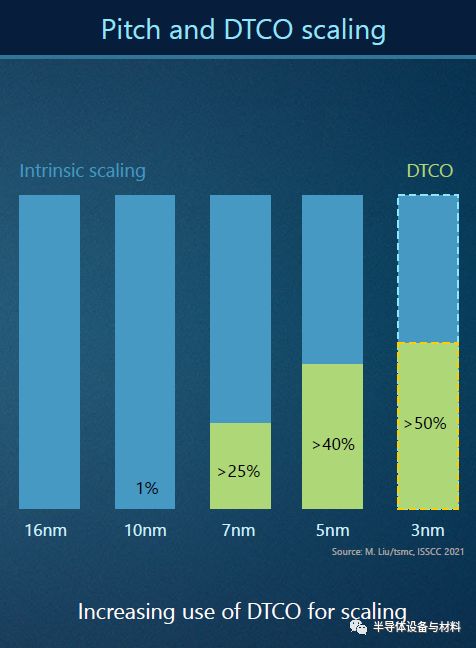

邏輯路線圖依賴于持續的邏輯密度改進來降低面積成本。但2D收縮正在放緩并變得更加困難。可用于繼續將柵極和電線拉得更近的物理空間越來越少,而且它們越接近,電氣挑戰就越嚴重。幾十年來,傳統的摩爾定律2D縮放(又名音高縮放或固有縮放)為該行業提供了非常好的服務。然而,展望未來,DTCO將越來越多地補充音高縮放,DTCO代表設計技術協同優化(見圖7)。DTCO 允許邏輯設計人員使用巧妙的 2D 和 3D 設計技術來增加相同間距下的邏輯密度。基于DTCO的一個關鍵變化是帶有背面供電網絡的埋地電源軌。這種新架構將厚電源線從硅晶圓的背面或晶體管下方路由到晶體管單元,允許進一步的2D縮放,同時降低電壓損耗。應用材料公司憑借在金屬、隔離電介質、蝕刻和 CMP 工藝方面的專業知識,幫助實現此技術和其他 DTCO 技術。

圖 7:設計技術協同優化 (DTCO) 預計將在未來節點中提供越來越大比例的整體擴展優勢。

結束語

應用材料公司的目標是成為我們客戶的 PPACt 支持公司,今天的大師班說明了材料工程對未來邏輯縮放的重要性。幾十年來,邏輯路線圖是由傳統的摩爾定律2D縮放驅動的。然而,隨著這種方法的好處放緩,業界正在通過基于材料工程的技術組合來補充它,以實現擴展到3nm節點甚至更遠的地方。客戶正在采用"PPACt的新劇本",這為應用材料公司創造了巨大的增長機會。隨著邏輯從5nm過渡到3nm,應用材料公司預計其服務市場將增長25-30%。

審核編輯 :李倩

-

電壓

+關注

關注

45文章

5698瀏覽量

117300 -

晶體管

+關注

關注

77文章

9979瀏覽量

140670 -

回流焊

+關注

關注

14文章

500瀏覽量

17376

原文標題:AMAT:材料工程

文章出處:【微信號:半導體設備與材料,微信公眾號:半導體設備與材料】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

多值電場型電壓選擇晶體管結構

晶體管故障診斷與維修技巧 晶體管在數字電路中的作用

晶體管與場效應管的區別 晶體管的封裝類型及其特點

全方位解剖MOS管

通過應用頻率將TPS92210的調光范圍擴展到通用AC范圍

晶體管的基本工作模式

NMOS晶體管和PMOS晶體管的區別

晶體管處于放大狀態的條件是什么

消息稱臺積電3nm/5nm將漲價,終端產品或受影響

PNP晶體管符號和結構 晶體管測試儀電路圖

晶體管縮放:將FinFET擴展到5nm以上;啟用門全方位拐點

晶體管縮放:將FinFET擴展到5nm以上;啟用門全方位拐點

評論