“always”關(guān)鍵字意味著這個(gè)語句塊“總是”一直執(zhí)行。大多數(shù)時(shí)候“always”后面跟一個(gè)邊沿事件或者延遲。

always后面不能0延遲,不然仿真會(huì)一直hang,例如下面這行代碼:

always clk = !clk; //zero delay loop. Simulation

will get stuck at time 0

always #10 clk = !clk; //correct time control

在實(shí)際的項(xiàng)目當(dāng)中“always” 后面經(jīng)常跟著一個(gè)邊沿事件上升沿或者下降沿。

always @(posedge) always @(negedge )

但問題是,你真的清楚posedge和negedge的準(zhǔn)確定義么?

實(shí)際上:

posedge意味著

0->1, 0-> x, 0-> z, x->1, z->1

negedge意味著

1->0, x->0, z->0, 1->x, 1->z

還有一種不那么常見的寫法就是即對(duì)上升沿又對(duì)下降沿敏感:

always @(edge clk) begin ... end

或者

always @(clk) begin ... end

審核編輯:湯梓紅

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111840 -

System

+關(guān)注

關(guān)注

0文章

166瀏覽量

37576 -

代碼

+關(guān)注

關(guān)注

30文章

4887瀏覽量

70264

原文標(biāo)題:SystemVerilog中的“always”語句塊

文章出處:【微信號(hào):芯片驗(yàn)證工程師,微信公眾號(hào):芯片驗(yàn)證工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

關(guān)于always語句的問題

Verilog中的always塊內(nèi)的語句執(zhí)行的速度?

initial和always兩者的關(guān)系分析

SystemVerilog中對(duì)于process的多種控制方式

systemverilog的決策語句if…else語句介紹

決策語句允許程序塊的執(zhí)行流程

數(shù)字硬件建模SystemVerilog-組合邏輯建模(1)連續(xù)賦值語句

什么是SystemVerilog-決策語句-if-else語句?

什么是程序塊

Verilog中的If語句和case語句介紹

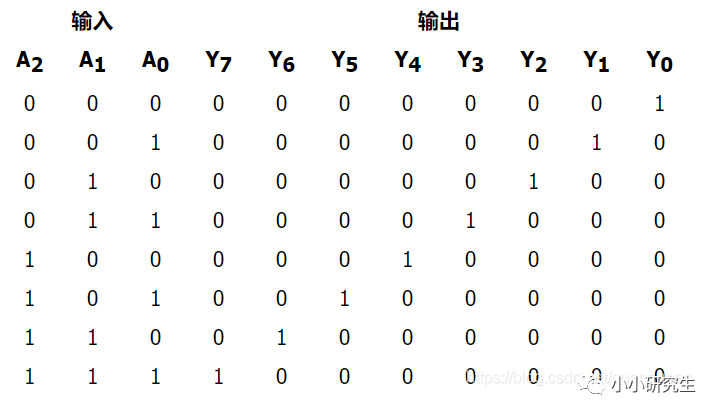

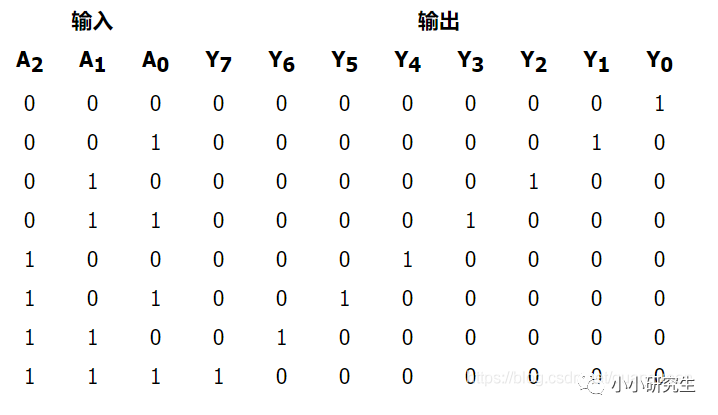

FPGA設(shè)計(jì):always組合邏輯塊的講解和譯碼器的實(shí)現(xiàn)

always組合邏輯塊的講解和譯碼器的實(shí)現(xiàn)

Python中什么是語句塊

SystemVerilog:處理信號(hào)雙驅(qū)動(dòng)問題解析

SystemVerilog中的always語句塊

SystemVerilog中的always語句塊

評(píng)論