1.同步電路設(shè)計

2.全異步電路設(shè)計

3.異步信號與同步電路交互的問題及其解決方法

4.SoC設(shè)計中的時鐘規(guī)劃策略

1.同步電路設(shè)計

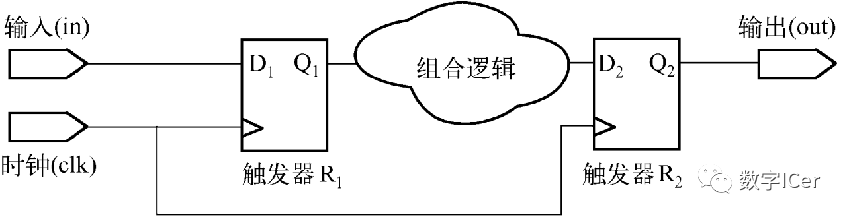

同步電路,即電路中的所有受時鐘控制的單元,如觸發(fā)器(Flip Flop)或寄存器(Register),全部由一個統(tǒng)一的全局時鐘控制。

同步電路的時序收斂

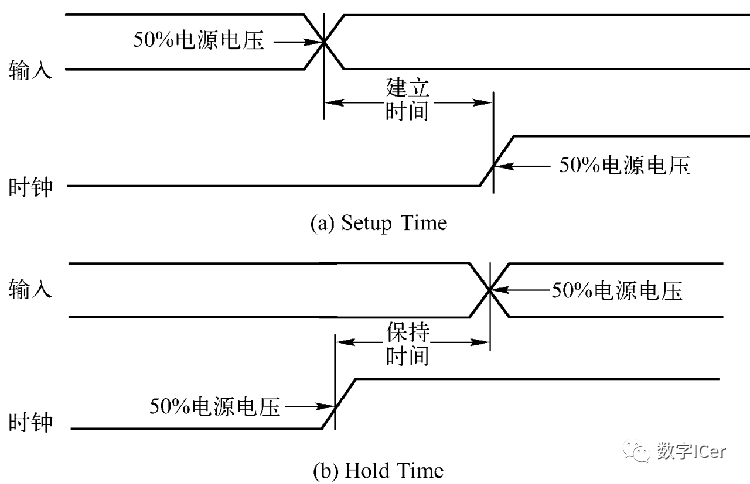

觸發(fā)器的建立時間和保持時間

觸發(fā)器的建立時間和保持時間

同步電路設(shè)計的優(yōu)點

在同步設(shè)計中,EDA工具可以保證電路系統(tǒng)的時序收斂,有效避免了電路設(shè)計中競爭冒險現(xiàn)象

由于觸發(fā)器只有在時鐘邊緣才改變?nèi)≈担艽笙薅鹊販p少了整個電路受毛刺和噪聲影響的可能

同步電路設(shè)計的缺點

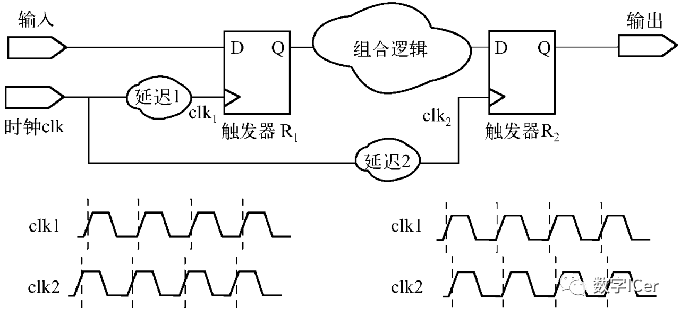

時鐘偏斜(Clock Skew)

時鐘樹綜合,需要加入大量的延遲單元,使得電路的面積和功耗大大增加

時鐘抖動(Clock Jitter)

時鐘偏斜

時鐘偏斜

2.全異步電路設(shè)計

全異步設(shè)計跟同步設(shè)計最大的不同就是它的電路中的數(shù)據(jù)傳輸可以在任何時候發(fā)生,電路中沒有一個全局的或局部的控制時鐘。

異步電路設(shè)計的基本原理

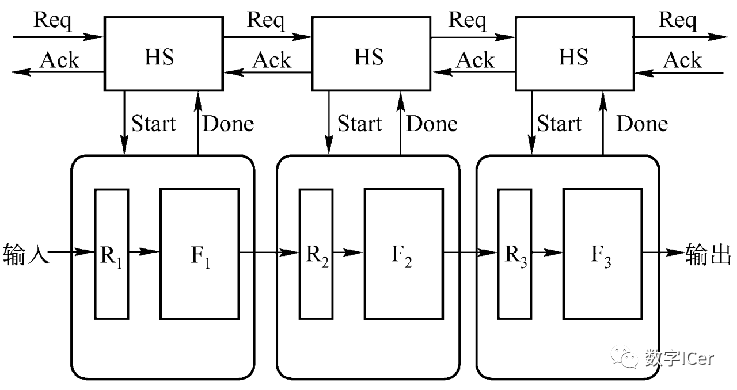

自定時的流水線數(shù)據(jù)通路

自定時的流水線數(shù)據(jù)通路

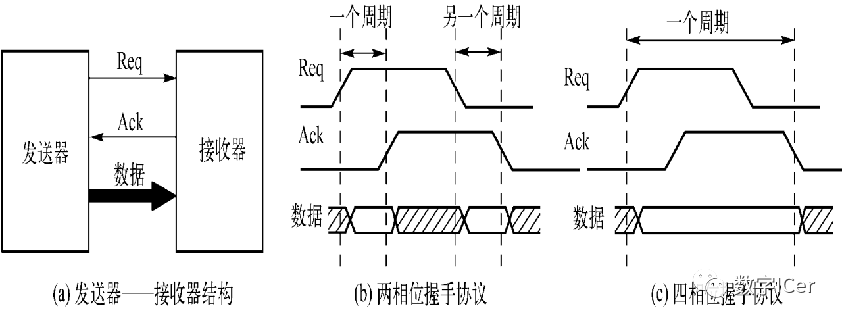

握手協(xié)議

握手協(xié)議原理

握手協(xié)議原理

異步電路設(shè)計的優(yōu)點

模塊化特性突出

對信號的延遲不敏感

沒有時鐘偏斜問題

有潛在的高性能特性

好的電磁兼容性

具有低功耗的特性異步電路設(shè)計的缺點

設(shè)計復(fù)雜

缺少相應(yīng)的EDA工具的支持

在大規(guī)模集成電路設(shè)計中應(yīng)避免采用異步電路設(shè)計

3.異步信號與同步電路交互的問題及其解決方法

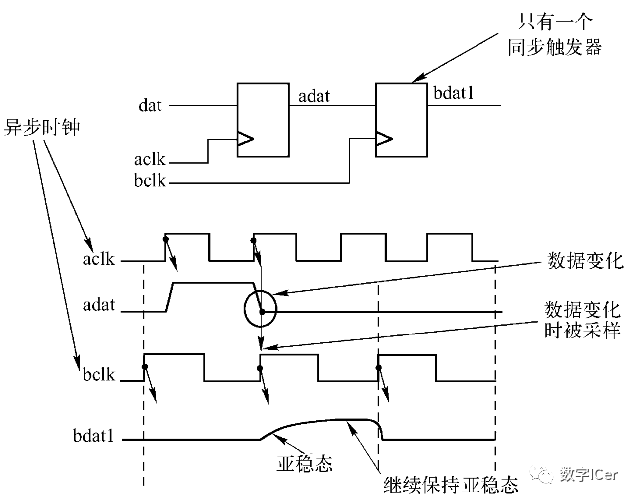

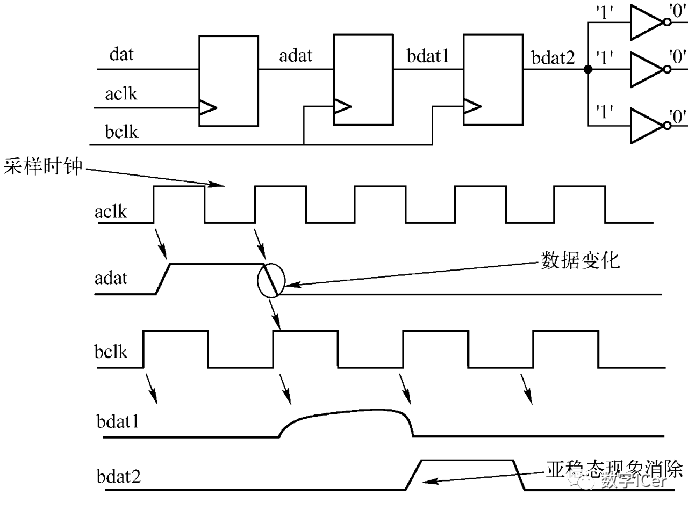

3.1亞穩(wěn)態(tài)現(xiàn)象

亞穩(wěn)態(tài)示意圖

亞穩(wěn)態(tài)示意圖  亞穩(wěn)態(tài)信號的傳播

亞穩(wěn)態(tài)信號的傳播

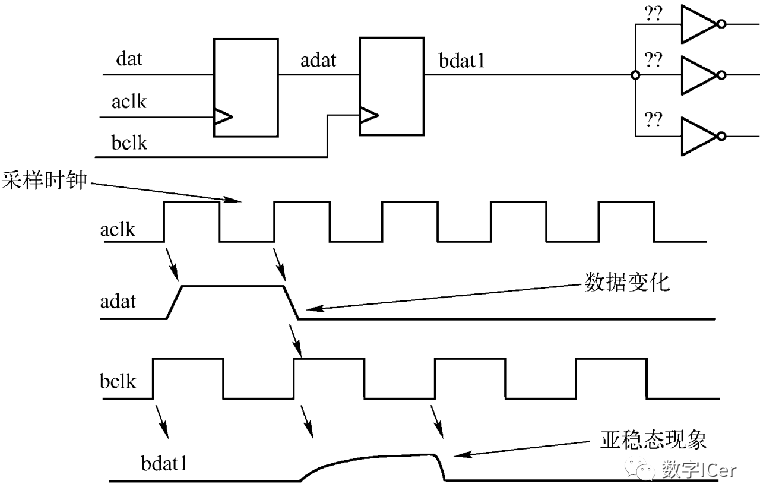

亞穩(wěn)態(tài)問題的解決及其RTL實現(xiàn)

亞穩(wěn)態(tài)現(xiàn)象的解決方法

亞穩(wěn)態(tài)現(xiàn)象的解決方法

modulesynchronizer( bclk,//目的時鐘,與aclk異步的時鐘 reset_b,//全局異步復(fù)位信號 adat,//異步輸入信號,工作在aclk bdat,//同步器輸出 ); inputbclk; inputreset_b; inputadapt; outputbdat; wirebdat; regbdat1; regbdat2; always@(posedgebclkornegedgereset_b) if(reset_b) {bdat2,bdat1}<=?2?'?b0; else ????{bdat2,bdat1}?<=?{bdat1,adat}; assign?bdat?=?bdat2; endmodule

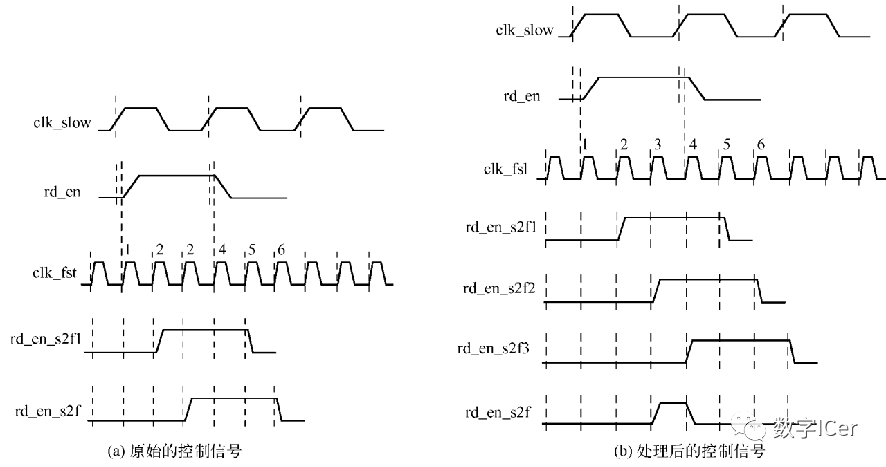

3.2快時鐘同步慢時鐘域下的異步控制信號

快時鐘同步慢時鐘信號示意圖

快時鐘同步慢時鐘信號示意圖

modulesynchronizer(

clk_fst,

reset_b,

rd_en,

rd_en_s2f

);

inputclk_fst,reset_b,rd_en

outputrd_en_s2f;

wirerd_en_s2f;

regrd_en_s2f1,rd_en_s2f2,rd_en_s2f3

always@(posedgeclk_fstornegedgereset_b)

if(!reset_b)

{rd_en_s2f3,rd_en_s2f2,rd_en_s2f1}<=?3'b111;

????else

??? {rd_en_s2f3,rd_en_s2f2,rd_en_s2f1}<={rd_en_s2f2,rd_en_s2f1,rd_en};

always?@?(rd_en_s2f3??or??rd_en_s2f2)

????case?({rd_en_s2f3,rd_en_s2f2})

????????????2'b01:

????????????????rd_en_s2f?<=?1'b1;????????

????????????default:

????????????????rd_en_s2f?<=?1'b0;

?????endcase

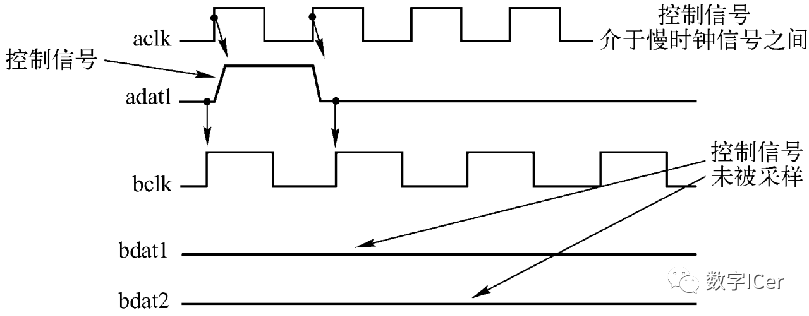

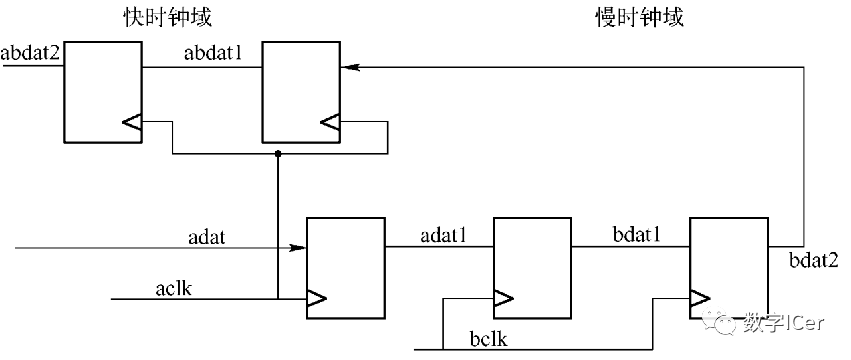

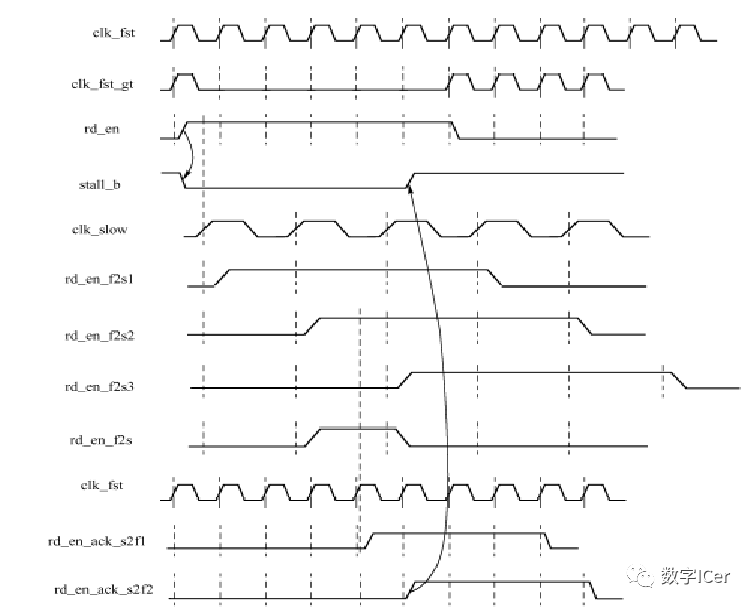

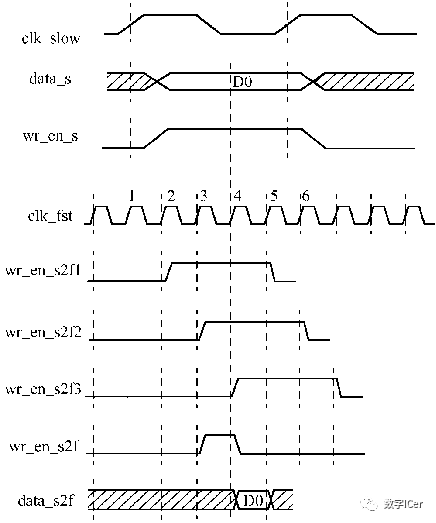

3.3慢時鐘同步快時鐘域下的異步控制信號

慢時鐘同步快時鐘信號示意圖

慢時鐘同步快時鐘信號示意圖

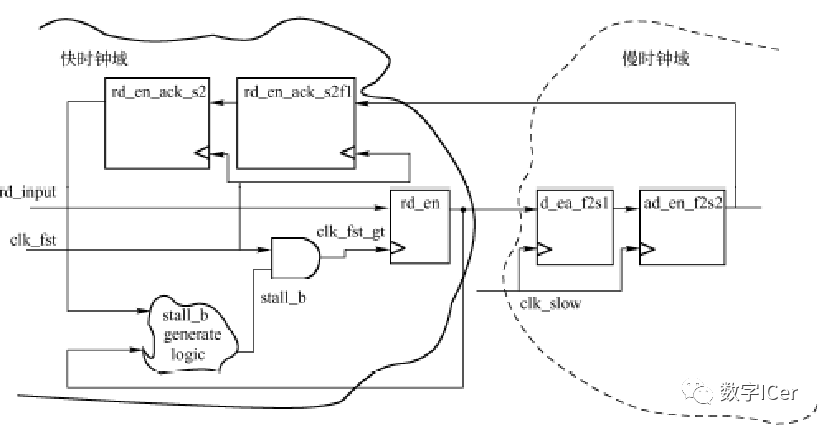

解決辦法 : 握手機制實現(xiàn)方法一

moduleadapt_gen( aclk,//快時鐘 reset_b,//系統(tǒng)復(fù)位信號 adat,//原始控制信號 abdat2, //從慢時鐘域反饋回來的同步控制信號 adat1 //經(jīng)過保持后的信號輸出 ); inputaclk,reset_b,adat,abdat2; outputadat1; regadat1; always@(posedgeaclkornegedgereset_b) if(!reset_b) adat1<=?1'b0;???? ????else?if?(abdat2) ??????????adat1?<=?1'b0; ????else if?(adat) ??????????adat1?<=?1'b1; endmoudule?

解決辦法 : 握手機制實現(xiàn)方法二

modulestall_logic( rd_en, rd_en_ ack_s2f, stall_b ); inputrd_en; inputrd_en_ack_s2f; outputstall_b; wirestall_b; always@(rd_enorrd_en_ack_s2f) if(rd_en_ack_s2f) stall_b<=?1'b1; else if?(rd_en) ????stall_b?<=?1'b0; else ????stall_b?<=?1'b1; endmodule

3.4異步時鐘域的數(shù)據(jù)同步

握手機制

握手同步異步數(shù)據(jù)

握手同步異步數(shù)據(jù)

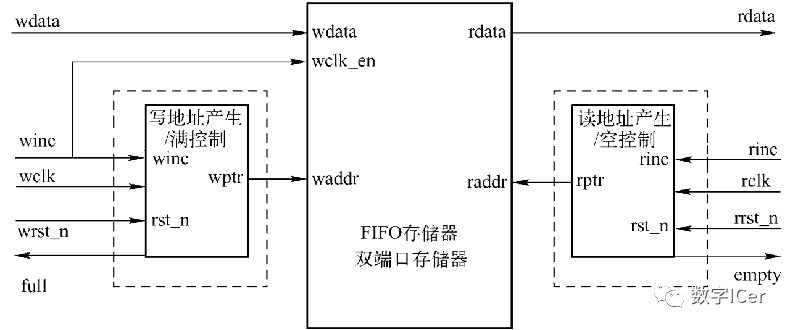

先入先出隊列(FIFO)

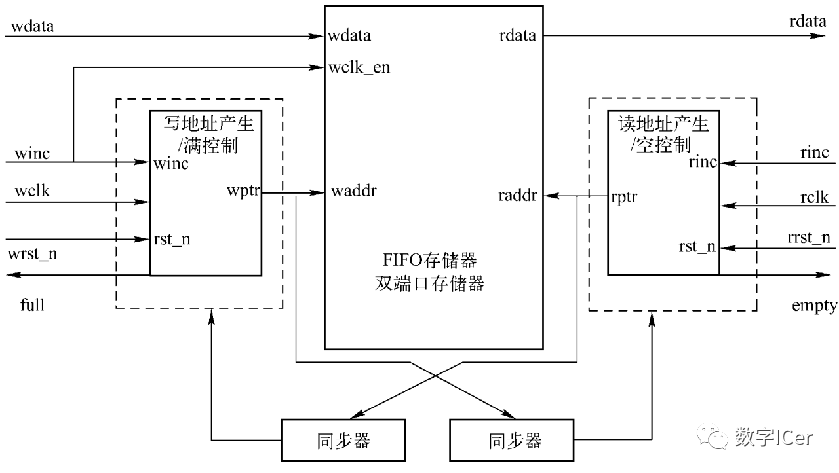

FIFO結(jié)構(gòu)圖

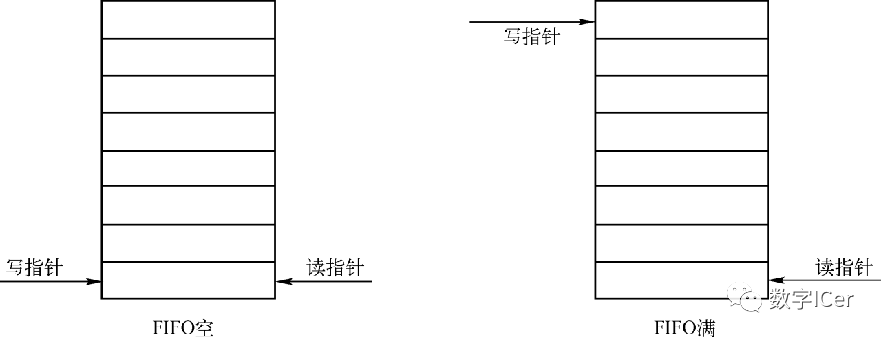

FIFO結(jié)構(gòu)圖  FIFO空滿示意圖

FIFO空滿示意圖

同步異步時鐘FIFO的電路行為

待同步的數(shù)據(jù)時鐘域會在其寫信號的控制之下,將數(shù)據(jù)寫入到FIFO中

目的時鐘域在發(fā)現(xiàn)空標(biāo)志位無效后,執(zhí)行FIFO讀動作,讀出被異步時鐘域?qū)懭隖IFO的數(shù)據(jù)

如果只要同步一個數(shù)據(jù),空標(biāo)志位再次有效

如果需要同步多個數(shù)據(jù),因為FIFO的讀/寫之間可以不受影響的進(jìn)行,所以待同步

FIFO設(shè)計中的亞穩(wěn)態(tài)問題

通常,通過比較讀/寫指針是否相等來判斷FIFO是否為空。而因為讀/寫指針屬于不同的時鐘域,兩者顯然不能直接連到比較器的兩端來產(chǎn)生空信號,否則會造成讀FIFO的目的時鐘域的電路碰到亞穩(wěn)態(tài)現(xiàn)象.

解決辦法

以格雷碼編碼表示讀/寫指針,用格雷碼加法器來實現(xiàn)讀/寫地址的加一動作

用同步器將讀指針同步到FIFO滿標(biāo)志的產(chǎn)生邏輯,同樣用同步器將寫指針同步到FIFO空標(biāo)志的產(chǎn)生邏輯中

新的異步FIFO的結(jié)構(gòu)框圖

新的異步FIFO的結(jié)構(gòu)框圖

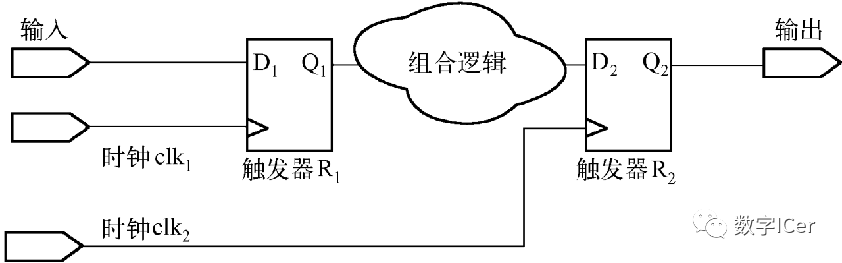

4.SoC設(shè)計中的時鐘規(guī)劃策略

首先盡可能使用同步設(shè)計:

對于同步電路,邏輯綜合和時鐘樹綜合等EDA工具能發(fā)揮更大的作用,可以用靜態(tài)時序分析工具分析單時鐘同步設(shè)計的時序收斂問題

可測性設(shè)計(DFT)的插入工作得到最大的簡化

其次,注意同步電路設(shè)計的缺陷

噪聲問題

時鐘樹上的功耗很大

如果必須采用不同的時鐘,則要注意

后端設(shè)計的復(fù)雜化,如約束條件中要考慮多周期路徑(Multi Cycle Path)

可測性設(shè)計更加復(fù)雜,因為此時系統(tǒng)中需要有多條獨立的掃描鏈

越多的時鐘域,發(fā)生亞穩(wěn)態(tài)的概率就會越大

最后,設(shè)計規(guī)劃中應(yīng)注意以下幾點:

盡可能將不同時鐘域的數(shù)量減到越少越好

盡可能將異步交互電路歸入同一或多個獨立的模塊,這樣不但方便后端設(shè)計腳本的書寫,也方便代碼的閱讀

盡可能避免使用電平觸發(fā)器(Latch),因為靜態(tài)時序分析會變得復(fù)雜,不能得到EDA工具很好的支持

盡可能減小時鐘樹的延時,因為這個延時可能會造成系統(tǒng)功能失效和多余的功耗;

任何異步時鐘域交互的環(huán)節(jié)都要盡可能避免亞穩(wěn)態(tài)現(xiàn)象.

審核編輯:湯梓紅

-

電路設(shè)計

+關(guān)注

關(guān)注

6696文章

2518瀏覽量

209929 -

同步電路

+關(guān)注

關(guān)注

1文章

60瀏覽量

13477 -

異步電路

+關(guān)注

關(guān)注

2文章

48瀏覽量

11293

原文標(biāo)題:同步與異步電路信號交互的問題

文章出處:【微信號:數(shù)字ICer,微信公眾號:數(shù)字ICer】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Xilinx FPGA異步復(fù)位同步釋放—同步后的復(fù)位該當(dāng)作同步復(fù)位還是異步復(fù)位?

同步與異步電路信號交互的問題

同步與異步電路信號交互的問題

評論