在這個由兩部分組成的系列的第 1 部分中,我們討論了復雜 SoC 和系統設計中對早期功耗分析的需求,并介紹了 VisualSim 圖形建模工具作為全面的能源仿真解決方案。在第 2 部分中,我們將展示 VisualSim 在多核嵌入式環境中預測和表達多個場景(偏移并發任務;比較 1 GHz 的單核與 250 MHz 的四個核;動態電壓頻率縮放 (DVFS)和功率門控)的功率值時的性能。

對新狀態的更改可以是開始新的執行、在一段時間不活動后進入深度睡眠、執行低優先級與高優先級用例,以及內存激活和刷新等特定條件。功率表達式值必須與時鐘速度和溫度等時序屬性同步變化。

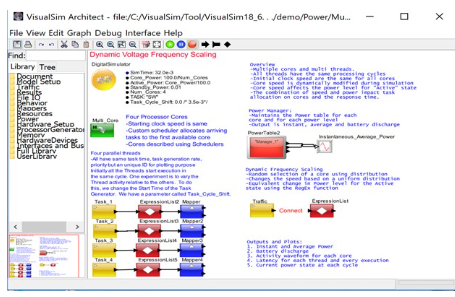

系統級功耗探索可以評估各種功耗降低和低功耗技術的優點和節省的能源。在這里,我們將討論這些技術,并使用 VisualSim 中的模擬模型解釋它們的影響。出于本研究的目的,我們使用四核處理器、調度程序代替 RTOS、四個并發線程以及按順序觸發處理資源上的線程的中斷。我們已經針對內核上的可變時鐘速度、1 到 4 之間的可變內核數以及線程觸發之間的偏移對模型進行了參數化。此外,我們還集成了電壓和時鐘速度動態變化的邏輯。

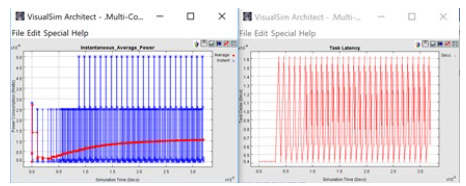

與此描述相關的框圖如圖 2 所示。

圖2.多核架構和四個并發線程的系統級框圖

進行以下實驗,我們查看每個場景的延遲和功耗。

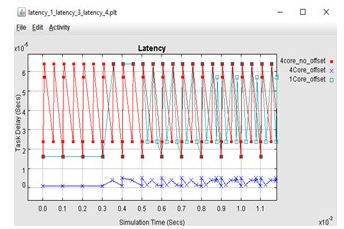

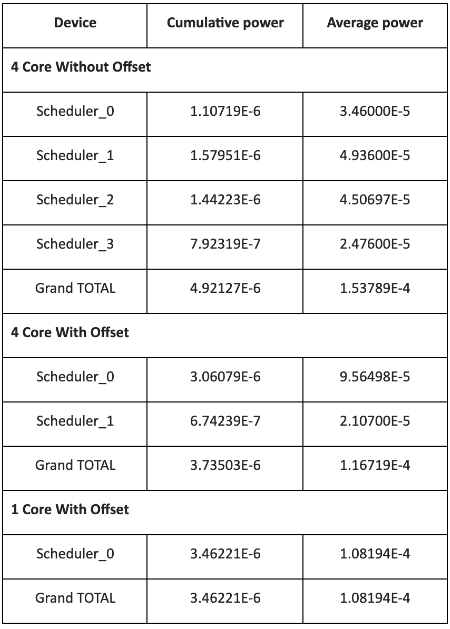

偏移并發任務:有四個任務,默認情況下,這些任務是同時觸發的。在這個實驗中,我們將每個任務移動了 3.5 毫秒。這樣,任務就不會同時啟動。如圖3所示,這種方法降低了功耗尖峰。最大尖峰從 1.0mW 到 7.5mW,節省 25%。從圖 4 可以看出,延遲確實從 7ms 降低到 0.5ms,這是一個顯著的改進。從圖 3 和表 1 中得出的有趣推論是,所有四個內核都不再被利用,并且處理資源的任務請求中只有偶爾的重疊。對平均功耗沒有影響。

比較運行在 1 GHz 的單核和運行在 250 MHz 的四個內核:在這個實驗中,我們將所有任務都定位在一個以 1GHz 速度運行的單個內核上。我們使用線程的偏移量。圖3的結果顯示,瞬時功率和平均功率均顯著降低。從圖 4 中我們可以看到延遲圖沒有顯著影響。可以看到,峰值功率與1.0mW的非失調值相同,但平均功率減少了一半,為0.15mW。這是因為處理速度存在相當大的浪費。

圖3.LHS 顯示隨時間推移的平均功率/RHS 顯示隨時間變化的即時功率

圖4.一段時間內的延遲

表 1.上述實驗的累積和平均功效

任務中具有偏移的一個內核的累積和平均功耗小于有偏移和不帶偏移的 4 個內核。

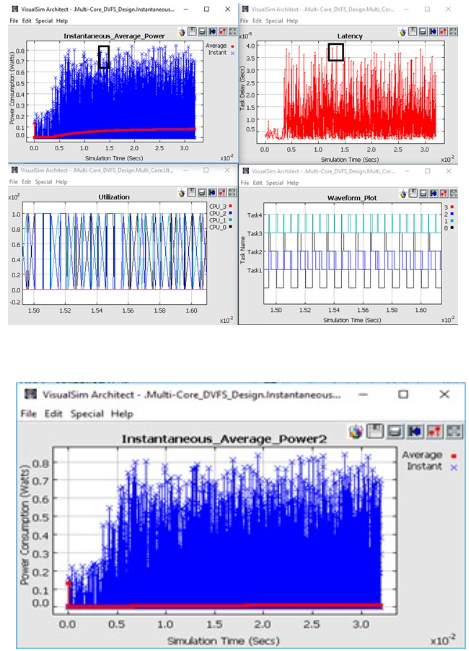

動態電壓頻率調節 (DVFS):這是節省功率的首選技術,通過根據任務要求改變時鐘速度來完成。一個很好的例子是 x86 處理器,其額定頻率為 3.2GHz,但在筆記本電腦上以 1.8 GHz 運行。使用原型板,當電壓頻繁調整時,很難預測任務的延遲。在相關模型中,我們沒有實現特定的算法,并且能夠看到功率和延遲在很寬的時鐘速度范圍內的變化。結果如圖 5 所示。我們將使用四個內核和四個偏移線程進行此運行。請注意,由于時鐘速度的變化,功率和延遲會波動。延遲與原始偏移版本相同。DVFS幫助我們大規模降低功耗。

從圖 4 中我們可以看到,所有任務的時隙都不相同,隨著傳入任務的增加,時鐘速度會根據需求隨每個內核而變化。

圖 6:通過實施電源管理降低平均功耗

強制內核在特定時間段后進入待機狀態將降低功耗。從圖 6 中,我們可以直觀地看到,實施電源管理后功耗會降低。為了擴展DVFS示例,可以修改每個任務的開始和頻率。在分析生成的統計信息時,我們可以看到正在使用的內核數量減少(core_3),從而消除了額外的待機功率并減少了功耗。如您所見,同時探索電源選項和軟件調度非常重要。這將確保所需的響應時間,同時減少功耗。

功率門控:這是在一段時間不活動后將處理單元移動到較低功率狀態的過程。一個常見的例子是筆記本電腦從活動到待機再到睡眠和休眠。在此模型中,我們將功率門控狀態機邏輯添加到電源表中。我們將空閑延遲設置為 10us,將轉換時間設置為 1 us。設備在待機狀態下停留的時間較短。從圖 6 中,我們可以看到,只要內核處于非活動狀態,內核的狀態就會從待機變為空閑。轉換時間對延遲的影響最小到零。

圖 6:電源門控,當內核處于非活動狀態 0.1ms 時,內核從待機狀態移動到空閑狀態,轉換時間為 1.0us

結論

系統級仿真可用于半導體級和系統級的廣泛功率分析。將功率探索與性能研究結合使用可確保權衡同時進行,從而確保更高質量的產品。許多功耗研究可以在產品實施之前在系統級完成,并消除集成過程中的所有意外。

這項研究的一個附帶好處是,熱和機械工程師可以獲得經過充分驗證的數據,而不是近似的最佳判斷信息。VisualSim 等軟件工具將性能和功耗分析集成到單個系統級模型中,有助于更快地構建模型,使用較小的模型集減少模型維護,并在設計周期的早期進行更高質量的探索。此外,這些系統級工具在設計中比以前更早地推動探索:

每個任務中偏移的含義可降低功耗和延遲

減少內核數量并提高處理器速度可顯著降低功耗

根據任務要求改變內核的時鐘速度是降低系統功耗的最佳方法

使內核在非活動期間空閑,減少系統中的電源浪費

審核編輯:郭婷

-

嵌入式

+關注

關注

5141文章

19537瀏覽量

315021 -

soc

+關注

關注

38文章

4341瀏覽量

221712 -

RTOS

+關注

關注

24文章

841瀏覽量

120767

發布評論請先 登錄

Python在嵌入式系統中的應用場景

嵌入式機器學習的應用特性與軟件開發環境

LDO在嵌入式系統中的應用 常見LDO故障及解決方法

什么是嵌入式?一文讀懂嵌入式主板

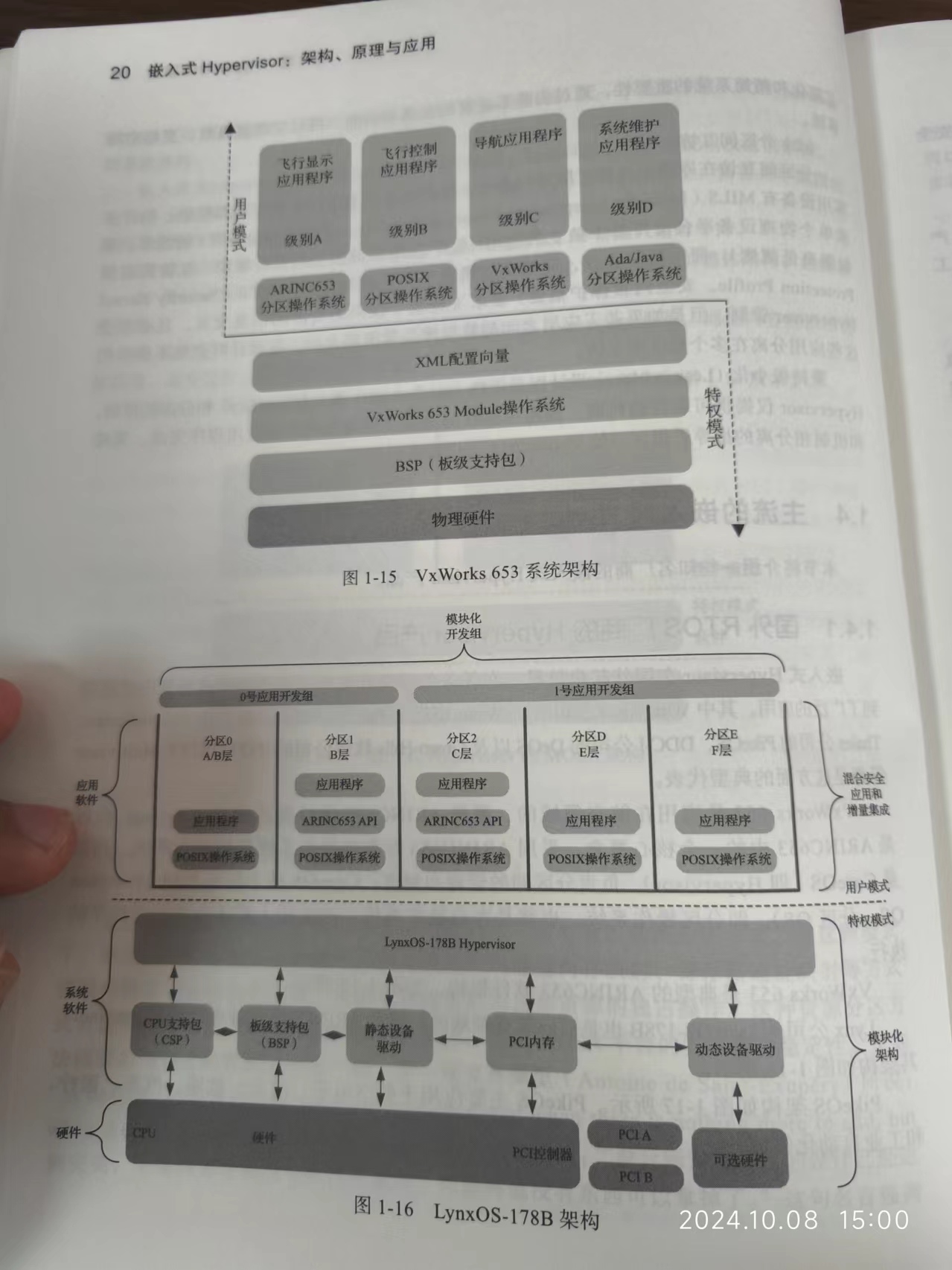

【「嵌入式Hypervisor:架構、原理與應用」閱讀體驗】+ Hypervisor應用場景調研

【「嵌入式Hypervisor:架構、原理與應用」閱讀體驗】+全文學習心得

【「嵌入式Hypervisor:架構、原理與應用」閱讀體驗】+第7-8章學習心得

嵌入式Hypervisor:架構、原理與應用 閱讀體驗 +Hypervisor基礎概念

嵌入式系統的未來趨勢有哪些?

嵌入式系統中的實時操作系統

機器視覺在嵌入式中的應用

嵌入式系統怎么學?

一文解析嵌入式多核異構方案,東勝物聯RK3588多核異構核心板系列一覽

VisualSim在多核嵌入式環境中預測和表達多個場景展示

VisualSim在多核嵌入式環境中預測和表達多個場景展示

評論