性能就是消除瓶頸,以最大程度地減少延遲并最大化吞吐量。當(dāng)今的高性能嵌入式計(jì)算 (HPEC) 系統(tǒng)集成了強(qiáng)大的處理子系統(tǒng),每個(gè)子系統(tǒng)都可能是一個(gè)功能齊全的處理節(jié)點(diǎn),需要與其他處理節(jié)點(diǎn)共享數(shù)據(jù)。為了最大限度地提高整體系統(tǒng)性能,需要最快、最高效的處理器到處理器數(shù)據(jù)路徑。借助 VPX,嵌入式系統(tǒng)擺脫了 VMEbus 共享并行總線模型。

與當(dāng)今基于串行結(jié)構(gòu)的系統(tǒng)相比,VME 性能總體吞吐量較低。一個(gè)原因是數(shù)據(jù)總線傳輸速度慢。另一個(gè)問(wèn)題是一次只有一個(gè)節(jié)點(diǎn)可以通信時(shí)發(fā)生的總線仲裁懲罰。對(duì)于基于現(xiàn)代串行架構(gòu)的系統(tǒng)(如 VPX),以太網(wǎng)也可用于在節(jié)點(diǎn)之間傳遞數(shù)據(jù)。交換以太網(wǎng)架構(gòu)使節(jié)點(diǎn)能夠并行通信,幾乎消除了共享總線的瓶頸。然而,當(dāng)今的處理器速度和功能遠(yuǎn)遠(yuǎn)超過(guò)以太網(wǎng)速度,使數(shù)據(jù)路徑和 CPU 密集型網(wǎng)絡(luò)堆棧再次成為關(guān)鍵的性能瓶頸。

其他替代結(jié)構(gòu),如Serial RapidIO(SRIO)和InfiniBand,也有其自身的局限性:很少有芯片供應(yīng)商支持SRIO,這意味著它的采用受到缺乏軟件的阻礙。由于SRIO沒(méi)有通用的軟件API[應(yīng)用程序編程接口]被廣泛采用,因此系統(tǒng)設(shè)計(jì)人員通常需要編寫(xiě)自己的定制軟件。對(duì) SRIO 的操作系統(tǒng)支持也很少,這使得 SRIO 設(shè)備驅(qū)動(dòng)程序也是一種定制開(kāi)發(fā)。就其本身而言,InfiniBand在可部署防御系統(tǒng)中的吸引力也有限,因?yàn)閷?duì)實(shí)時(shí)操作系統(tǒng)的軟件支持有限。它還受到硅器件的高成本和單一來(lái)源供應(yīng)商的有限支持的阻礙。

如今,幾乎所有現(xiàn)代處理器都使用 PCI Express (PCIe) 總線作為板載外設(shè)的高速互連。在大多數(shù)處理系統(tǒng)中,PCIe 接口還提供進(jìn)出處理器的最快數(shù)據(jù)路徑。PCIe 接口支持多種數(shù)據(jù)速率:第 1 代接口以 2.5 Gbps 的速度運(yùn)行,第 2 代接口將數(shù)據(jù)速率翻倍至 5.0 Gbps。 第 3 代接口將此速度提高到 8.0 Gbps,并且通過(guò)使用更有效的數(shù)據(jù)編碼機(jī)制,有效數(shù)據(jù)傳輸速率成為第 2 代的兩倍。PCIe Gen4標(biāo)準(zhǔn)的開(kāi)發(fā)即將完成,Gen4設(shè)備將于2017年晚些時(shí)候開(kāi)始從供應(yīng)商處發(fā)貨,再次旨在將性能提高一倍。

為什么使用 PCIe 繞過(guò)以太網(wǎng)或其他結(jié)構(gòu)接口設(shè)備?用戶報(bào)告了更低的延遲、更高的吞吐量和額外的附帶好處,例如降低功耗、增加 MTBF [平均故障間隔時(shí)間] 和降低成本。然而,直到最近,使用 PCIe 技術(shù)支持主機(jī)到主機(jī)通信的好處需要復(fù)雜的設(shè)置 PCIe 設(shè)備和交換機(jī)的配置。它還要求定制PCIe共享內(nèi)存驅(qū)動(dòng)程序軟件,大大降低了其可取性。

Dolphin Interconnect Solutions以其StarFabric技術(shù)而聞名,它為HPEC系統(tǒng)開(kāi)發(fā)了一種具有巨大前景的解決方案。其 eXpressWare 軟件套件使用 PCIe 連接來(lái)創(chuàng)建更快、更靈活的消息和處理器到處理器通信數(shù)據(jù)傳輸機(jī)制。該軟件經(jīng)過(guò)優(yōu)化,可利用 DMA [直接內(nèi)存訪問(wèn)]、PCIe 組播和多核處理等硬件功能。該軟件隱藏了 PCIe 設(shè)置的復(fù)雜性,簡(jiǎn)化了主機(jī)到主機(jī)架構(gòu)的設(shè)置和配置。

當(dāng)支持所有必需的 PCIe 交換機(jī)配置時(shí),該軟件可以自動(dòng)檢測(cè) PCIe 端點(diǎn)并將其配置為透明或非透明端口,設(shè)置消息隊(duì)列和數(shù)據(jù)傳輸窗口,以及配置和管理數(shù)據(jù)傳輸資源(如 DMA 引擎)。此外,它還帶有標(biāo)準(zhǔn)軟件API接口,可以使用大多數(shù)軟件開(kāi)發(fā)人員已經(jīng)熟悉的軟件范例進(jìn)行更快的軟件應(yīng)用程序開(kāi)發(fā)。

Dolphin 的 eXpressWare 使 HPEC 系統(tǒng)設(shè)計(jì)人員能夠利用最高水平的數(shù)據(jù)結(jié)構(gòu)性能來(lái)滿足國(guó)防工業(yè)的加固設(shè)備需求。為了獲得使用 PCIe 向嵌入式系統(tǒng)設(shè)計(jì)人員進(jìn)行節(jié)點(diǎn)到節(jié)點(diǎn)數(shù)據(jù)傳輸?shù)暮锰帲珻urtiss-Wright 最近在運(yùn)行 Linux 和 Wind River VxWorks 操作系統(tǒng)的嵌入式英特爾 SBC 和 DSP 引擎中添加了對(duì) eXpressWare 的支持,并將這種支持?jǐn)U展到基于 Power 架構(gòu)的主板。堅(jiān)固耐用的嵌入式系統(tǒng)依靠高性能結(jié)構(gòu)來(lái)減少數(shù)據(jù)傳輸時(shí)間的延遲。PCIe 為實(shí)現(xiàn)低延遲、高吞吐量處理器到處理器性能提供了當(dāng)今的最佳解決方案。通過(guò)提供通用軟件 API 并屏蔽 PCIe 設(shè)備編程的復(fù)雜細(xì)節(jié),eXpressWare 為 HPEC 系統(tǒng)設(shè)計(jì)人員帶來(lái)了突破,并為嵌入式硬件帶來(lái)了高速、低延遲的點(diǎn)對(duì)點(diǎn)通信。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19885瀏覽量

235054 -

芯片

+關(guān)注

關(guān)注

459文章

52480瀏覽量

440529 -

總線

+關(guān)注

關(guān)注

10文章

2959瀏覽量

89728

發(fā)布評(píng)論請(qǐng)先 登錄

QDMA Subsystem for PCI Express v5.0產(chǎn)品指南

Marvell展示2納米芯片3D堆疊技術(shù),應(yīng)對(duì)設(shè)計(jì)復(fù)雜性挑戰(zhàn)!

VirtualLab Fusion應(yīng)用:光柵的魯棒性分析與優(yōu)化

Littrow結(jié)構(gòu)中光柵系統(tǒng)的配置與優(yōu)化

光伏連接器外殼:超越簡(jiǎn)單塑料的復(fù)雜性與重要性

KeyStone設(shè)備的PCI Express (PCle)常見(jiàn)問(wèn)題

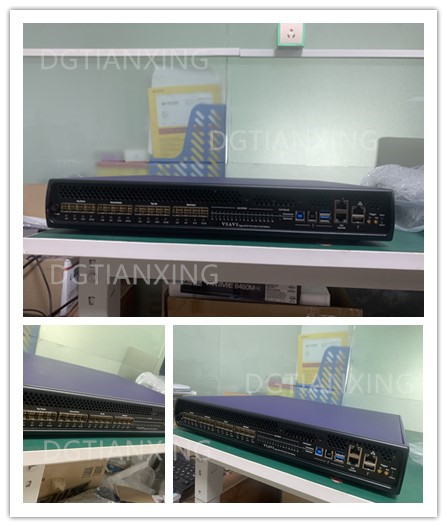

VIAVI Xgig 4K16 PCI Express 4.0 協(xié)議分析儀平臺(tái)介紹

DS320PR810的PCI Express合規(guī)性測(cè)試

使用TI PCI-Express Gen5.0轉(zhuǎn)接驅(qū)動(dòng)器進(jìn)行眼圖掃描

LMK3H0102 PCI Express合規(guī)性報(bào)告

LMK6H和LMKDB1xxx PCI Express合規(guī)性報(bào)告

LMK6H PCI Express合規(guī)性報(bào)告

LMKDB1xxx PCI Express合規(guī)性報(bào)告

消除PCI Express配置的復(fù)雜性,優(yōu)化HPEC系統(tǒng)設(shè)計(jì)

消除PCI Express配置的復(fù)雜性,優(yōu)化HPEC系統(tǒng)設(shè)計(jì)

評(píng)論