我是一名數(shù)字前端IP設(shè)計工程師,方向為通信芯片IP設(shè)計,我的主要工作就是“翻譯”算法代碼。

經(jīng)典的ASIC開發(fā)流程主要有:

以算法設(shè)計為主導(dǎo)

算法C代碼手工轉(zhuǎn)換為RTL

RTL與算法C代碼生成的測試向量對比進行驗證

依賴FPGA做大量實時、現(xiàn)場測試

適合通信信號處理,音視頻處理或圖像處理等產(chǎn)品

我的工作主要就是將算法C代碼手工轉(zhuǎn)換為RTL,尤其是通信芯片的設(shè)計,算法主要是將浮點運算近似成定點運算,定點的精度決定了系統(tǒng)的性能,所以一種開發(fā)模式就是,用C平臺生成的case數(shù)據(jù)和RTL仿真的數(shù)據(jù)進行對比,保證定點化后的仿真性能。

所以對于單個計算模塊的開發(fā)來說,可以說就是體力活了,算法的計算過程已經(jīng)擺在那里,單就是純翻譯。

然而再復(fù)雜的算法,在設(shè)計工程師的眼里,也就是一堆數(shù)學(xué)公式,算法設(shè)計者也應(yīng)該盡量做簡單的算法實現(xiàn),比如除法,求冪次方、開平方等復(fù)雜運算到了設(shè)計工程師這里都已經(jīng)轉(zhuǎn)化成了簡單的乘法和加法運算。更復(fù)雜的就是累加、累乘(我所能接觸到的)。

做芯片第一應(yīng)該關(guān)注的是芯片的PPA(Performance, Power, Area),如何設(shè)計的出更高性能的電路,占用更少的資源/面積,更低的功耗。這才是我們的專業(yè)知識。

通過學(xué)習(xí)算法代碼和文檔以及協(xié)議,了解算法的計算意圖。然后進行數(shù)據(jù)通路的分析,整體的數(shù)據(jù)流走向。哪些需要計算的數(shù)據(jù)可以用寄存器存儲,哪些數(shù)據(jù)需要用RAM存儲。模塊的劃分可拆解,哪些計算單元是功能類似的,可以做成一個小IP,乘法器同時使用的最大數(shù)量,是否能在整個大模塊中分時復(fù)用。

算法的設(shè)計中沒有時序的概念,也沒有計算時間的長短。需要設(shè)計工程師去整理整個模塊的計算流水,流水線排的時間長,需要的計算邏輯就越少,反之,面積越大。面積與速度互換思想,貫穿始終。現(xiàn)成乘法器的數(shù)量有限,是否能加上幾個乘法器而獲得模塊整體運算速度提高30%的收益,都需要去折中(Trade off)考慮。

排好計算流水,控制通路,一般都使用狀態(tài)機去做,當然,狀態(tài)機怎么設(shè)計算法可不會教你。整個模塊與更高層模塊的交互,接口控制時序需要討論確定。數(shù)據(jù)通路可能還需要用到RAM/Regfile去緩存中間數(shù)據(jù)的結(jié)果,RAM/Regfile的讀寫地址控制也是常見設(shè)計。數(shù)據(jù)通路的運算,是主要消耗資源的部分,所以一個好的詳細設(shè)計方案非常重要,同樣的設(shè)計,別人可以用比你小30%的面積和少30%的時間來實現(xiàn)。這可能就是設(shè)計工程師真正的價值體現(xiàn)之處。

對于通信算法中,矩陣運算也是比較常見的,復(fù)雜矩陣的運算是最耗費資源的,矩陣運算的拆解也需要很多技巧,比如矩陣的乘法是A的第一行乘以B的第一列,累加得到第一個元素,這部分的運算電路可以復(fù)用流水起來做。一個矩陣需要拆解合并成數(shù)個小矩陣,想要保持并行,用寄存器存儲,就會消耗的資源多。存在RAM中就是串行流水做會消耗的時間長,所以這都需要在模塊架構(gòu)設(shè)計階段去計算處理時間和評估消耗資源、折中是否采取(Trade off)。

這種大型矩陣運算動輒幾百上千bit的寄存器輸出,連線選擇運算,可能會造成后端congestion問題,所以方案設(shè)計的重要性又體現(xiàn)出來了。組合邏輯的運算,如果路徑過長,時序會出現(xiàn)問題,插寄存器的位置也非常重要,消耗的寄存器的數(shù)量也是不同的,甚至可以通過手動retimming,找個寄存器把打拍的位置換一下,消耗的資源還是相同的。

對于芯片的功耗前端能做的就是,去加一些時鐘門控,模塊不用時候可以關(guān)掉,組合邏輯計算單元不用的時候避免翻轉(zhuǎn),乘法器的使能信號的控制,避免無效翻轉(zhuǎn),數(shù)據(jù)通路寄存器帶著使能打拍,工具也會自動插時鐘門控,這些就和算法沒關(guān)系了。

至于算法,當然不同領(lǐng)域的相關(guān)知識不同,雖然設(shè)計方法是完全類似的,但是在一個領(lǐng)域深扎,成為這個領(lǐng)域的專業(yè)的人,可以更好的理解算法到硬件的實現(xiàn)。

IP設(shè)計工程師經(jīng)常調(diào)侃自己是算法“翻譯官”,雖然也沒什么問題,但是自嘲歸自嘲,如果感興趣的話,還是應(yīng)該去想著如何更好的做好自己的設(shè)計,做好芯片。即使是“翻譯官”也是一個十分有價值的“翻譯官”。

審核編輯 :李倩

-

算法

+關(guān)注

關(guān)注

23文章

4699瀏覽量

94748 -

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111832

原文標題:如何將算法“翻譯”成Verilog?

文章出處:【微信號:IP與SoC設(shè)計,微信公眾號:IP與SoC設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何將RT-Thread移植到NXP MCUXPressoIDE上

如何將python文件導(dǎo)入到ROS系統(tǒng)中

AI助力實時翻譯耳機

Verilog 測試平臺設(shè)計方法 Verilog FPGA開發(fā)指南

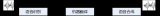

LLMWorld上線代碼翻譯新工具——問丫·碼語翻譯俠,快來體驗!

如何將LVDS/OLDI橋接到HDMI/DVI

如何將算法“翻譯”成Verilog?

如何將算法“翻譯”成Verilog?

評論