unpacked數(shù)組和packed數(shù)組的主要區(qū)別是unpacked數(shù)組在物理存儲(chǔ)時(shí)不能保證連續(xù),而packed數(shù)組則能保證在物理上連續(xù)存儲(chǔ)。

另一種看待unpacked數(shù)組和packed數(shù)組差異點(diǎn)的角度是,packed數(shù)組可以看成一個(gè)整體,一個(gè)單一向量。

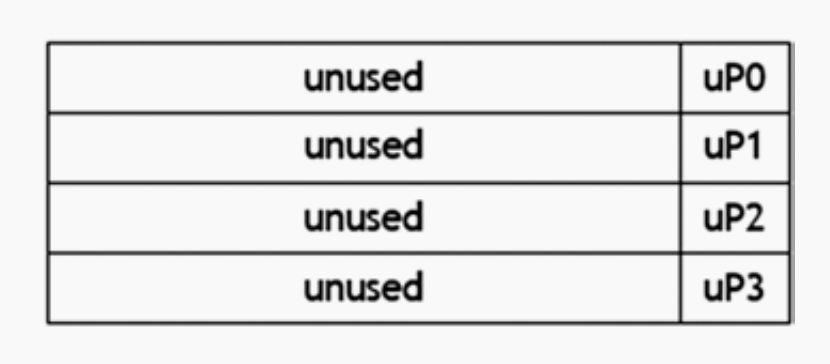

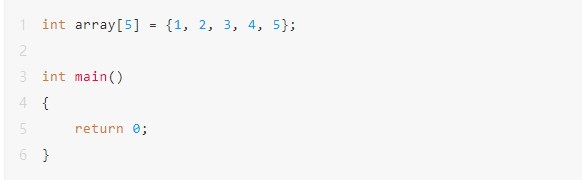

unpacked數(shù)組的維度是在數(shù)組名稱之后聲明的,數(shù)組中內(nèi)容可以是任何數(shù)據(jù)類型或者其他數(shù)組。

bit uP [3:0]; //1-D unpacked //unpacked dimensions declared after the data identifed name.

正如你所注意到的,uP0到uP3分散在多個(gè)word中,它們不是連續(xù)的。

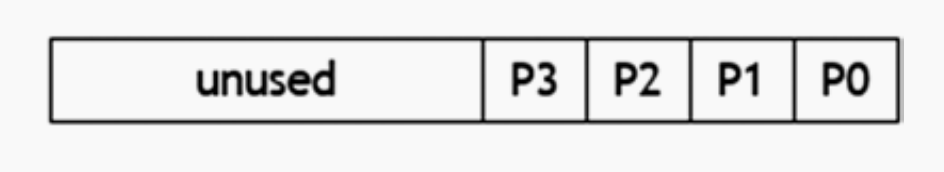

packed數(shù)組的維度是在數(shù)組名稱之前聲明的,下面是一個(gè)packed數(shù)組的例子:

bit [3:0] p; //1-D packed //packed dimensions declared before the data identifer name

這個(gè)打包數(shù)組可以表示為如下所示:

正如上圖所示的,p3到p0在物理空間上是連續(xù)的。

某種意義上,這個(gè)所謂的packed就是表示是否在物理空間連續(xù)存放。

2-D Packed Array

module tb; // 2-D packed array // 4 entries(rows) of 8 bits(columns) each // Total packed dimension (contiguous bits) = 4*8 = 32 bits bit [3:0][7:0] m_data; initial begin m_data = 32'h0102_0304;//Assign to 32 contiguous bits //display 2-d packed array as a contiguous set of bits $display ("m_data = 0x%h", m_data); //display 1 byte each stored at m_data[0]...m_data[3] for (int i = 0; i < 4; i++) begin $display ("m_data[%0d] = 0x%h", i, m_data[i]); end end endmodule

仿真log:

m_data = 0x01020304 m_data[0] = 0x04 m_data[1] = 0x03 m_data[2] = 0x02 m_data[3] = 0x01 V C S S i m u l a t i o n R e p o r t

在上面的例子中,我們聲明了一個(gè)名為“m_data”的二維packed數(shù)組。請(qǐng)注意,所有維度的聲明都位于數(shù)組名稱的左側(cè)。

這個(gè)數(shù)組一共有4(行),每行8bit(列),總的大小是4*8 = 32bit。因?yàn)槭莗acked數(shù)組,其中所有的bit都是連續(xù)存儲(chǔ)的,所以可以按照bit單獨(dú)索引到。

我們給這個(gè)數(shù)組賦值(32'h 0102_0304),然后打印相應(yīng)的4行數(shù)據(jù)。

0x04、0x03、0x02、0x01

3-D Packed Array

3維數(shù)組和2維數(shù)組類似。

module tb;

bit [2:0][1:0][7:0] m_data; // 3-D packed array

initial begin

// Assign 16-bits ([1:0][7:0]) at each of the three

//([2:0])locations

m_data[0] = 16'h0102;

m_data[1] = 16'h0304;

m_data[2] = 16'h0506;

// m_data as a single packed value

$display ("m_data = 0x%h", m_data);

//Assign the entire array with a single value

m_data = 48'hcafe_face_0708;

// m_data as a single packed value

$display("m_data = 0x%h", m_data);

foreach (m_data[i]) begin

$display ("m_data[%0d] = 0x%h", i, m_data[i]);

foreach (m_data[, j]) begin

$display ("m_data[%0d][%0d] = 0x%h", i, j, m_

data[i][j]);

end

end

end

endmodule

仿真log:

m_data = 0x050603040102 m_data = 0xcafeface0708 m_data[2] = 0xcafe m_data[2][1] = 0xca m_data[2][0] = 0xfe m_data[1] = 0xface m_data[1][1] = 0xfa m_data[1][0] = 0xce m_data[0] = 0x0708 m_data[0][1] = 0x07 m_data[0][0] = 0x08 V C S S i m u l a t i o n R e p o r t

在上面的例子中,我們聲明了一個(gè)三維packed數(shù)組,命名為“m_data”,一共是328 = 48bit。由于這是一個(gè)packed數(shù)組,48bit在物理空間上是連續(xù)分配的。

我們可以理解為:

1*48 或者 3*16 或者 6*8 或者48*1

1-D Packed and1-D Unpacked Array

下面是一個(gè)一維packed數(shù)組和1維unpacked數(shù)組的示例:

module PU; logic [31:0] v1 [7:0]; //1-D packed & 1-D unpacked (memory) initial begin //Array Index 7 of unpacked v1[7] = 'h FF_FF_FF_FF; //equivalent to v1[7][31:0] $display(v1); //Array Index 6 of unpacked; 31:0 of packed v1[6][31:0] = 'h 11_11_11_11; $display(v1); //Array Index 5 of unpacked; 15:0 of packed v1[5][15:0] = 'h aa_aa; $display(v1); //Array Index 4 of unpacked; 0th bit of packed v1[4][0] = 1; $display(v1); end endmodule

仿真log:

'{‘h ffffffff, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h

xxxxxxxx, ‘h xxxxxxxx}

'{‘h ffffffff, ‘h 11111111, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h

xxxxxxxx, ‘h xxxxxxxx}

'{‘h ffffffff, ‘h 11111111, ‘h xxxxaaaa, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h

xxxxxxxx, ‘h xxxxxxxx}

'{‘h ffffffff, ‘h 11111111, ‘h xxxxaaaa, ‘h xxxxxxx1, ‘h xxxxxxxx, ‘h xxxxxxxx, ‘h

xxxxxxxx, ‘h xxxxxxxx}

V C S S i m u l a t i o n R e p o r t

在上面的例子中,我們聲明了一個(gè)1維unpacked數(shù)組("v1",共包含8項(xiàng)),數(shù)組中的每一個(gè)內(nèi)容又是一個(gè)packed數(shù)組(bit [31:0])“v1”。我們可以理解為一個(gè)深度為8,寬度為32的存儲(chǔ)器。

4-D Unpacked Array

我們聲明一個(gè)4維unpacked數(shù)組,所有維度相關(guān)的聲明都在數(shù)組名稱的右邊

logic uP [3:0][2:0][1:0][7:0];

如果一個(gè)unpacked數(shù)據(jù)項(xiàng)使用1word存儲(chǔ),上面的數(shù)組就需要物理空間

4*3*2*8*1 word

1-D Packed and3-D Unpacked Array

logic [7:0] uP [3:0][2:0][1:0];

上面這個(gè)示例,是一個(gè)4*3*2個(gè)unpacked數(shù)組,其中每一個(gè)數(shù)據(jù)項(xiàng)都是一個(gè)8bit的packed數(shù)組。

如果每一個(gè)unpacked數(shù)據(jù)項(xiàng)使用1word存儲(chǔ),那么數(shù)組uP總的存儲(chǔ)空間就是

4*3*2*1word

2-D Packed and2D-Unpacked Array

logic [1:0] [7:0] uP[3:0] [2:0];

上面聲明了一個(gè)2維unpacked 數(shù)組,每個(gè)數(shù)組項(xiàng)都是一個(gè)2維的packed數(shù)組。所以,如果每個(gè)unpacked數(shù)據(jù)項(xiàng)使用1word存儲(chǔ),那么總的存儲(chǔ)空間是:

4*3*1word

3-D Packed and1-D Unpacked Array

logic [2:0][1:0][7:0] uP [3:0];

上面聲明了一個(gè)1維unpacked數(shù)組uP,一共4項(xiàng),每項(xiàng)是一個(gè)3維packed數(shù)組。如果每個(gè)unpacked數(shù)據(jù)項(xiàng)使用1word存儲(chǔ),那么總的存儲(chǔ)空間是

4*1word * 2

因?yàn)?word裝不下一個(gè)packed數(shù)組

原文標(biāo)題:SystemVerilog中的Packed和Unpacked數(shù)組

文章出處:【微信公眾號(hào):芯片驗(yàn)證工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

存儲(chǔ)

+關(guān)注

關(guān)注

13文章

4522瀏覽量

87296 -

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

112102 -

數(shù)組

+關(guān)注

關(guān)注

1文章

419瀏覽量

26475

原文標(biāo)題:SystemVerilog中的Packed和Unpacked數(shù)組

文章出處:【微信號(hào):芯片驗(yàn)證工程師,微信公眾號(hào):芯片驗(yàn)證工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

unpacked數(shù)組和packed數(shù)組的主要區(qū)別

unpacked數(shù)組和packed數(shù)組的主要區(qū)別

評(píng)論