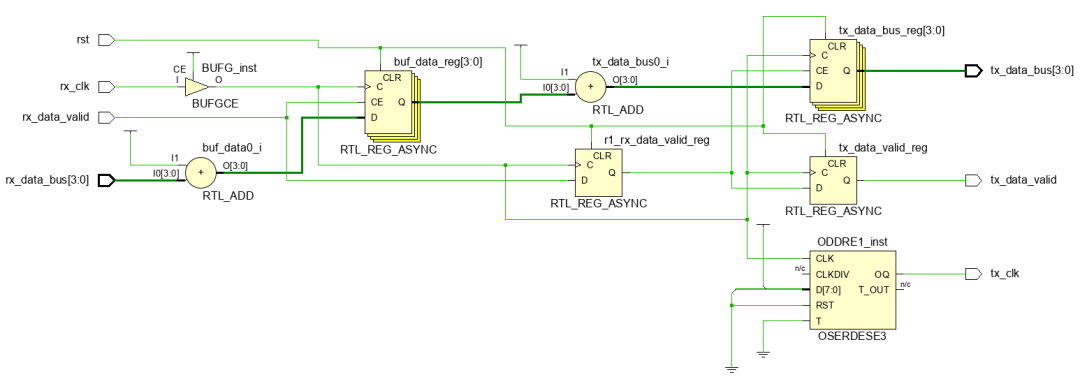

1. 前言 在上篇文章里《時序分析基本概念(一)——建立時間》,我們向大家介紹了建立時間的基本概念和計算方法。本篇文章我們將通過vivado工程實(shí)例來向大家介紹如何讀懂時序分析報告。 2. vivado實(shí)例工程介紹 借用的vivado工程實(shí)例很簡單,工程的電路原理框圖如下圖所示:  ? 電路功能為:在rx_data_valid信號拉高的情況下,對輸入的數(shù)據(jù)總線rx_data_bus數(shù)據(jù)做了兩次加法,最后通過tx_data_bus管腳輸出。大家可以自行下載vivado工程,具體下載方法見文章末尾。 我們對該工程進(jìn)行管腳約束和時鐘約束,如下圖所示:

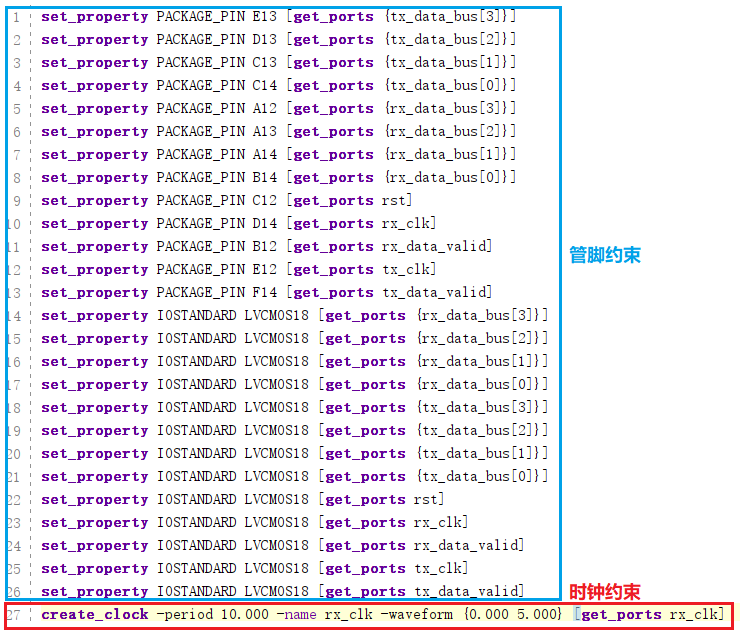

? 電路功能為:在rx_data_valid信號拉高的情況下,對輸入的數(shù)據(jù)總線rx_data_bus數(shù)據(jù)做了兩次加法,最后通過tx_data_bus管腳輸出。大家可以自行下載vivado工程,具體下載方法見文章末尾。 我們對該工程進(jìn)行管腳約束和時鐘約束,如下圖所示:  ? 圖中時鐘約束的含義是告訴vivado工具,rx_clk時鐘的時鐘頻率為100MHz。vivado軟件只有在知道工作時鐘頻率后,才能正確的布局布線以滿足該電路工作的時序要求。 3. 工程編譯并打開時序報告 vivado工程編譯好后,打開時序分析報告。

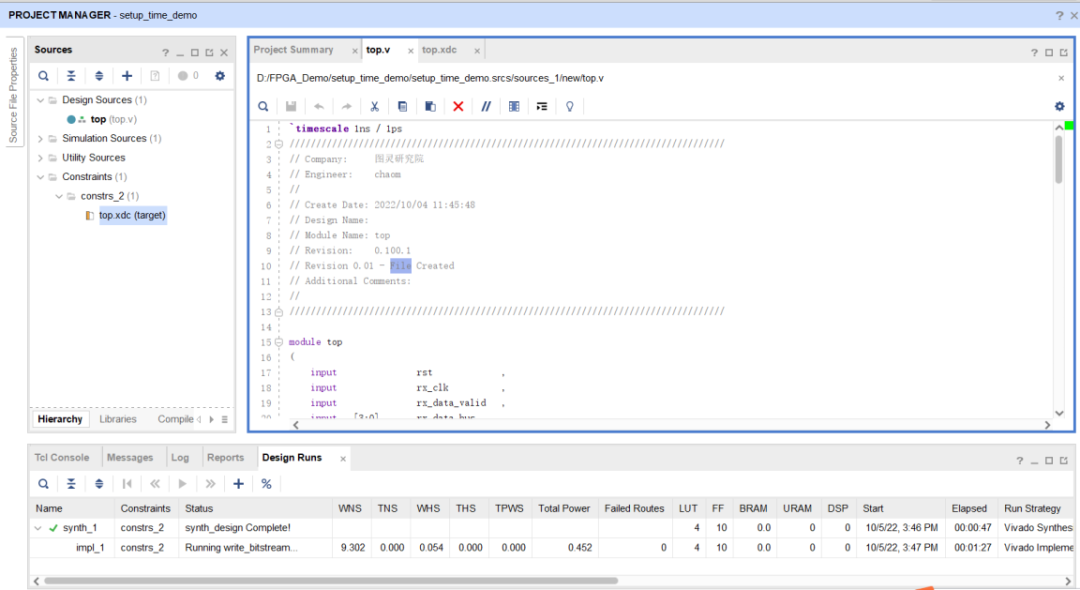

? 圖中時鐘約束的含義是告訴vivado工具,rx_clk時鐘的時鐘頻率為100MHz。vivado軟件只有在知道工作時鐘頻率后,才能正確的布局布線以滿足該電路工作的時序要求。 3. 工程編譯并打開時序報告 vivado工程編譯好后,打開時序分析報告。  ? 時序報告打開方法: ->先選擇“Open Implemented Design”,打開布局布線后的工程;

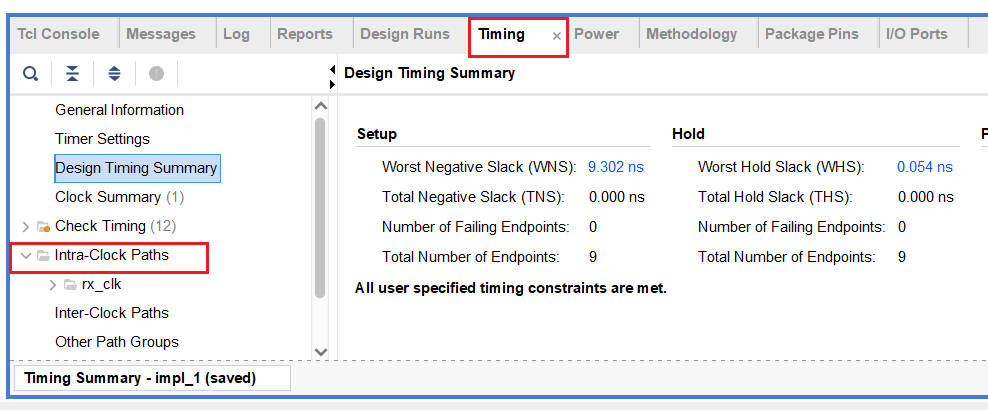

? 時序報告打開方法: ->先選擇“Open Implemented Design”,打開布局布線后的工程;  -> 選擇“Timing”選項(xiàng)卡,并展開“Intra-Clock Paths”;

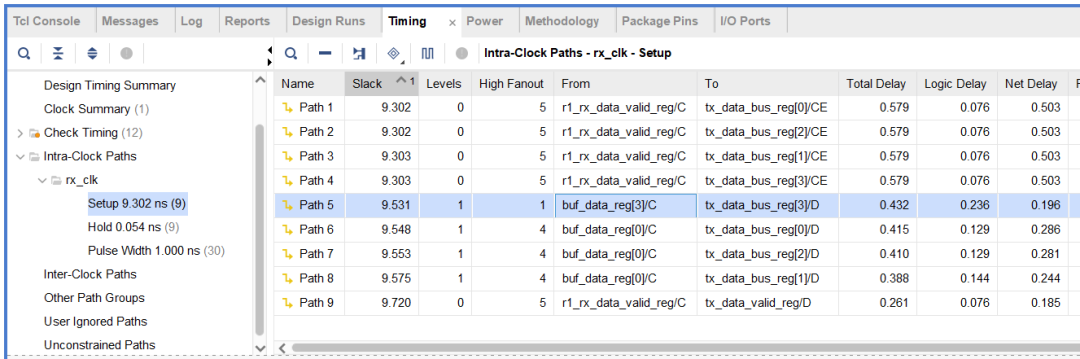

-> 選擇“Timing”選項(xiàng)卡,并展開“Intra-Clock Paths”;  ? 由于我們的工程只有rx_clk時鐘域,因此我們只用展開“rx_clk”時序報告,查看“Setup”報告(建立時間報告)。

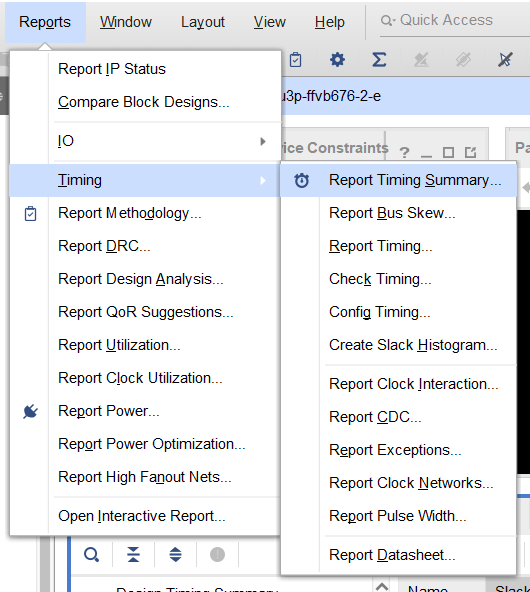

? 由于我們的工程只有rx_clk時鐘域,因此我們只用展開“rx_clk”時序報告,查看“Setup”報告(建立時間報告)。  ? 如果工程復(fù)雜,路徑過多,該窗口默認(rèn)顯示的路徑并不全,如果沒有找到我們想查看的路徑,我們可以選擇菜單上的“Reports -> Timing -> Report Timing Summary”

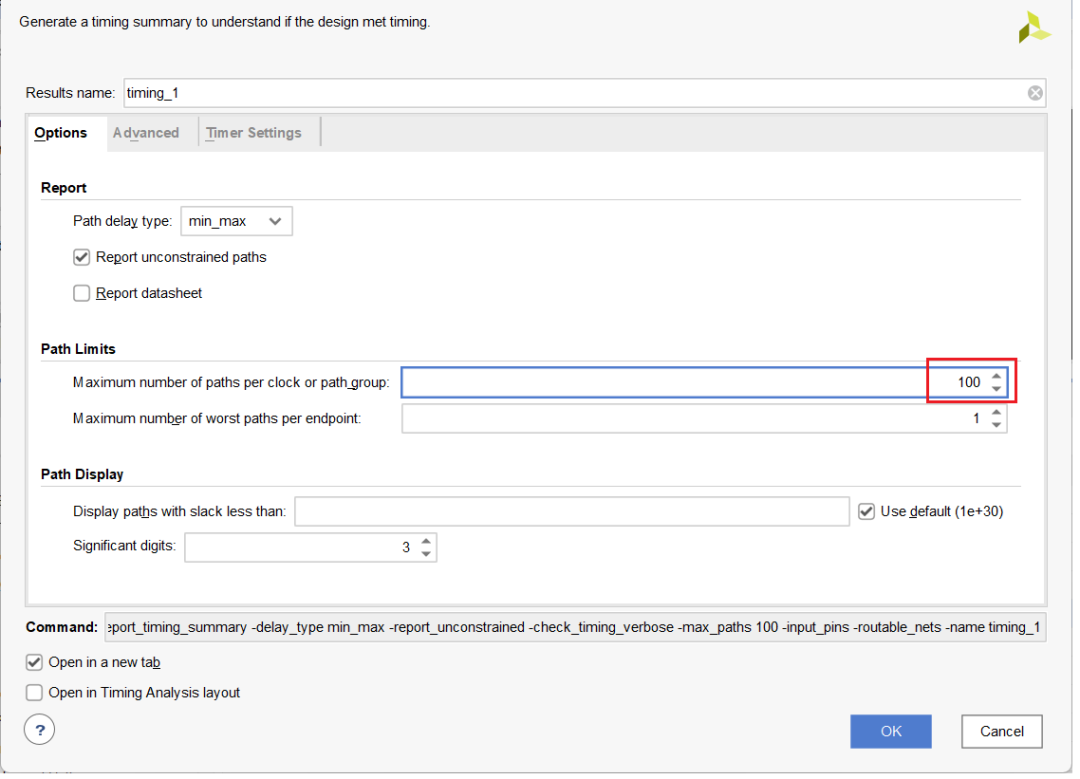

? 如果工程復(fù)雜,路徑過多,該窗口默認(rèn)顯示的路徑并不全,如果沒有找到我們想查看的路徑,我們可以選擇菜單上的“Reports -> Timing -> Report Timing Summary”  ? 修改Maximum number of paths per clock orpath_group至100(根據(jù)自己需要),點(diǎn)擊“OK”按鈕。

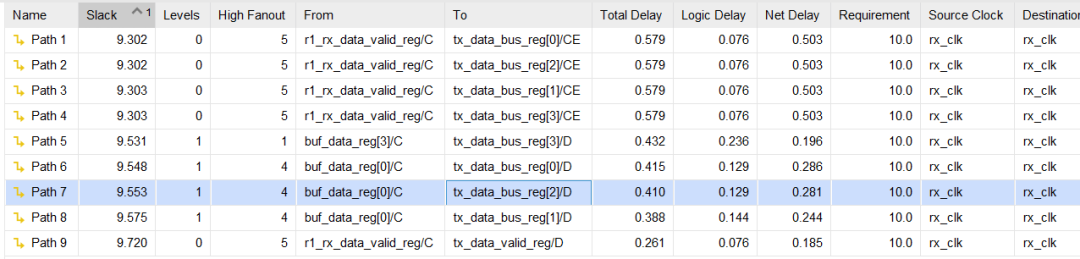

? 修改Maximum number of paths per clock orpath_group至100(根據(jù)自己需要),點(diǎn)擊“OK”按鈕。  ? 4. 分析時序報告 比如圖中的路徑“Path7”,第一列的“Slack”指的是建立時間的松緊程度。該值為正值代表該路徑的布線滿足時序要求。“Levels”為1,代表數(shù)據(jù)路徑上的組合邏輯為1級,“High Fanout”代表該路徑的扇出為4。

? 4. 分析時序報告 比如圖中的路徑“Path7”,第一列的“Slack”指的是建立時間的松緊程度。該值為正值代表該路徑的布線滿足時序要求。“Levels”為1,代表數(shù)據(jù)路徑上的組合邏輯為1級,“High Fanout”代表該路徑的扇出為4。  ? 雙擊路徑“Path7”可以打開更詳盡的時序報告,如下圖所示。

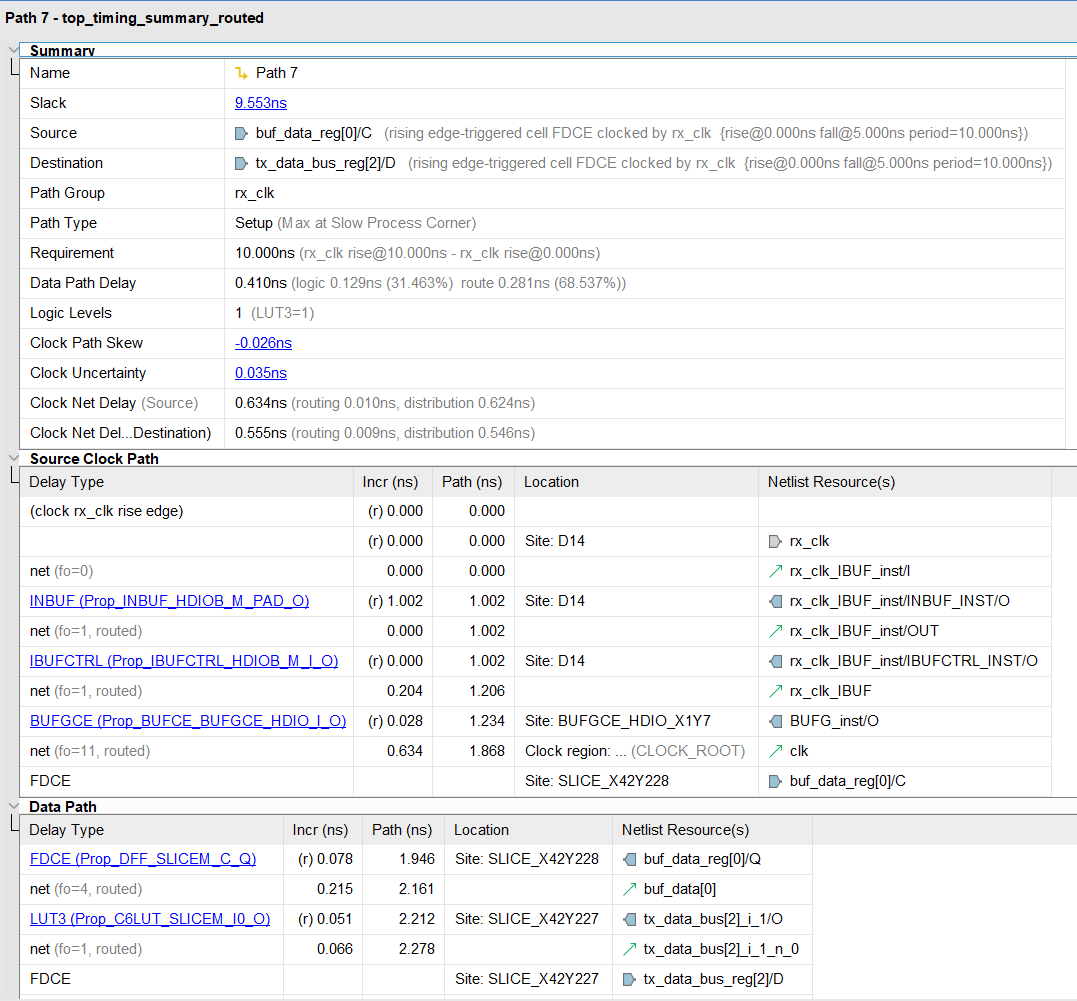

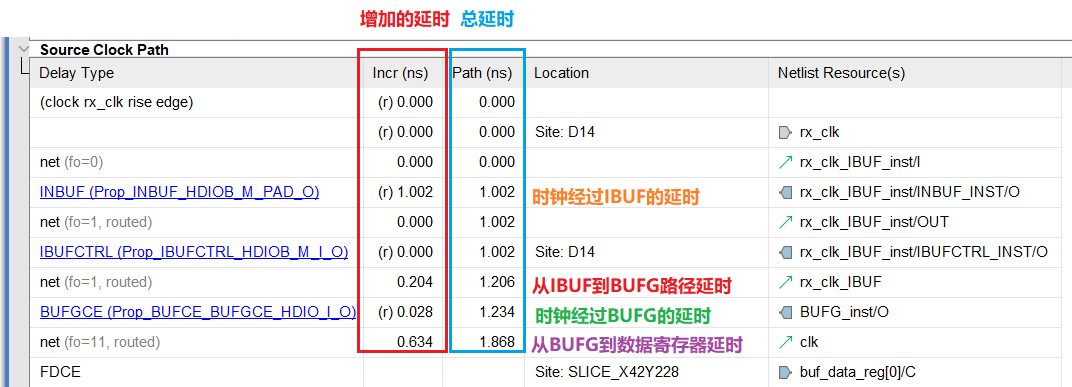

? 雙擊路徑“Path7”可以打開更詳盡的時序報告,如下圖所示。  ? ① Source Clock Path 我們先來查看源時鐘路徑,圖中用各個顏色表示了每行延時的具體含義。

? ① Source Clock Path 我們先來查看源時鐘路徑,圖中用各個顏色表示了每行延時的具體含義。  ? 根據(jù)上篇文章的學(xué)習(xí)可知,以上的延時總和為源時鐘的路徑延時,對應(yīng)建立時間計算公式的Tclk1,即Tclk1 = 1.868ns。 我們也可以通過綜合出來的電路圖來更直觀的查看這些路徑延時的由來,打開“SYNTHESIS-> Open Synthesized Design -> Schematic”。

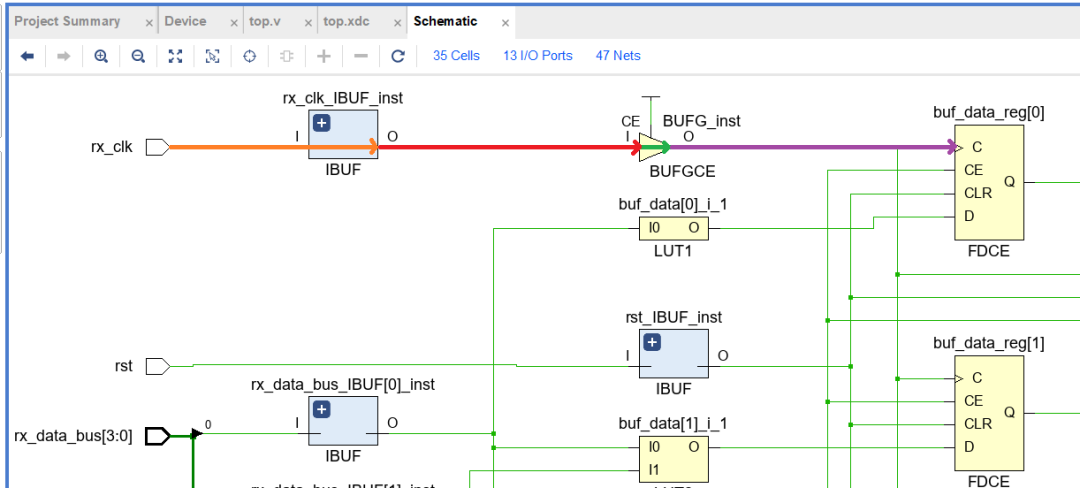

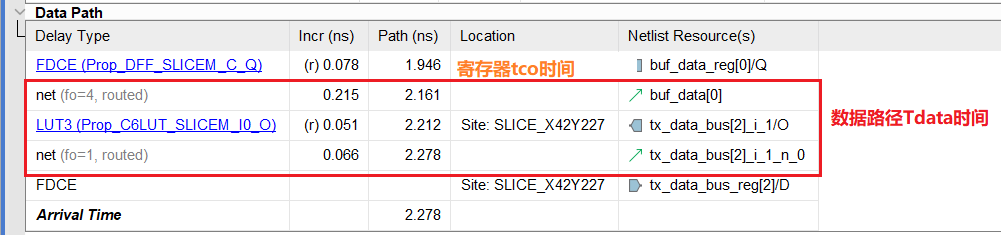

? 根據(jù)上篇文章的學(xué)習(xí)可知,以上的延時總和為源時鐘的路徑延時,對應(yīng)建立時間計算公式的Tclk1,即Tclk1 = 1.868ns。 我們也可以通過綜合出來的電路圖來更直觀的查看這些路徑延時的由來,打開“SYNTHESIS-> Open Synthesized Design -> Schematic”。  ? 圖中用對應(yīng)每行時序報告注釋的顏色標(biāo)出了對應(yīng)延時路徑的具體位置。 ② Data Path 我們再來看數(shù)據(jù)路徑時間。數(shù)據(jù)路徑時間相對簡單,主要由寄存器“buf_data_reg[0]”的內(nèi)部延時Tco、走線的路徑延時以及組合邏輯引入的延時組成。圖中用不同顏色的注釋已經(jīng)標(biāo)注出來。

? 圖中用對應(yīng)每行時序報告注釋的顏色標(biāo)出了對應(yīng)延時路徑的具體位置。 ② Data Path 我們再來看數(shù)據(jù)路徑時間。數(shù)據(jù)路徑時間相對簡單,主要由寄存器“buf_data_reg[0]”的內(nèi)部延時Tco、走線的路徑延時以及組合邏輯引入的延時組成。圖中用不同顏色的注釋已經(jīng)標(biāo)注出來。  ? 走線的路徑延時 + 組合邏輯引入的延時即為數(shù)據(jù)延時Tdata。同樣的,我們通過在綜合出來的電路圖上,用每行時序報告注釋的顏色標(biāo)出了對應(yīng)延時路徑的具體位置。

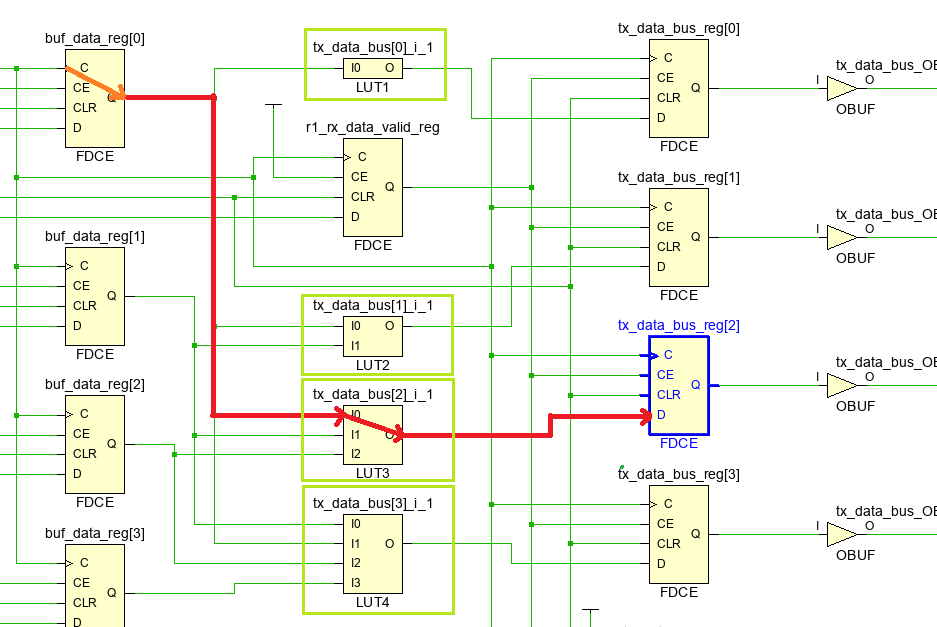

? 走線的路徑延時 + 組合邏輯引入的延時即為數(shù)據(jù)延時Tdata。同樣的,我們通過在綜合出來的電路圖上,用每行時序報告注釋的顏色標(biāo)出了對應(yīng)延時路徑的具體位置。  ? 圖中buf_data_reg[0]的Q端口輸出分別連至4個綠色框標(biāo)出的器件,因此該路徑的扇出為4。由于該數(shù)據(jù)路徑上,從第一個寄存器到達(dá)第二個寄存器之間只經(jīng)過了1個LUT器件,因此路徑上的組合邏輯為1級。 ③ Destination Clock Path 最后我們來看目的時鐘路徑。圖中用各個顏色表示了每行延時的具體含義。

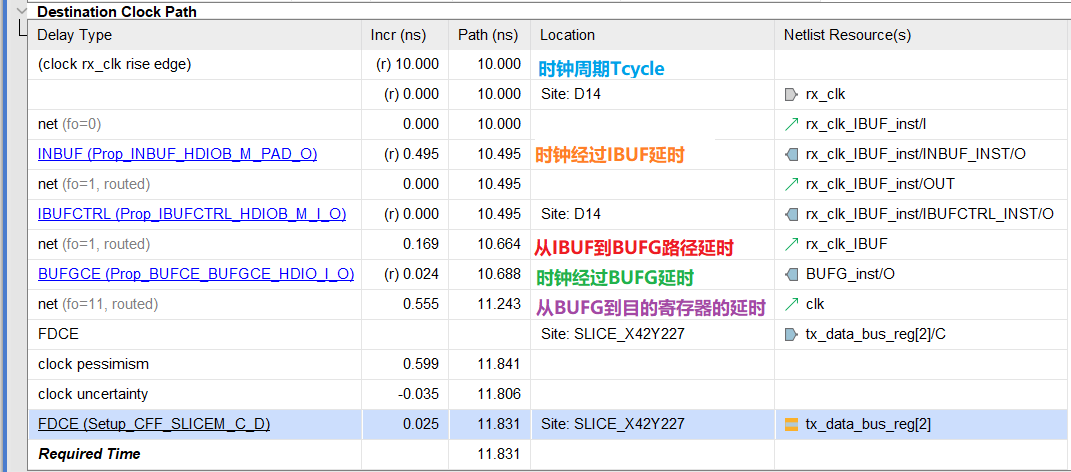

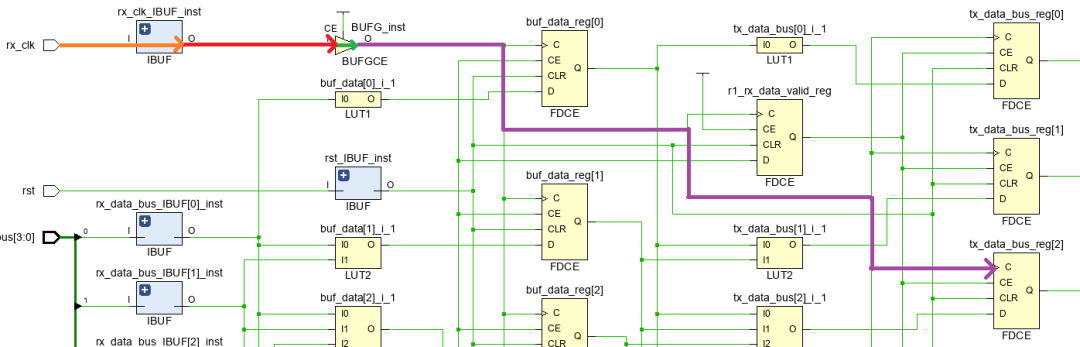

? 圖中buf_data_reg[0]的Q端口輸出分別連至4個綠色框標(biāo)出的器件,因此該路徑的扇出為4。由于該數(shù)據(jù)路徑上,從第一個寄存器到達(dá)第二個寄存器之間只經(jīng)過了1個LUT器件,因此路徑上的組合邏輯為1級。 ③ Destination Clock Path 最后我們來看目的時鐘路徑。圖中用各個顏色表示了每行延時的具體含義。  ? 表中除掉藍(lán)色的標(biāo)注,其它所有顏色標(biāo)注的延時總和為Tclk2。 表中還有“clock pessimism”時鐘悲觀值和“clock uncertainty”時鐘抖動值,這些值的具體由來不在本文中做詳述。 表中最后一項(xiàng)FDCE (Setup_CFF_SLICEM_C_D)為寄存器“tx_data_bus_reg”寄存器需要的建立時間值(Tsu)。 同樣的,我們通過在綜合出來的電路圖上,用每行時序報告注釋的顏色標(biāo)出了對應(yīng)延時路徑的具體位置。

? 表中除掉藍(lán)色的標(biāo)注,其它所有顏色標(biāo)注的延時總和為Tclk2。 表中還有“clock pessimism”時鐘悲觀值和“clock uncertainty”時鐘抖動值,這些值的具體由來不在本文中做詳述。 表中最后一項(xiàng)FDCE (Setup_CFF_SLICEM_C_D)為寄存器“tx_data_bus_reg”寄存器需要的建立時間值(Tsu)。 同樣的,我們通過在綜合出來的電路圖上,用每行時序報告注釋的顏色標(biāo)出了對應(yīng)延時路徑的具體位置。  ? 這樣我們通過公式最終可計算出建立時間的slack值: slack = Tcycle + Tclk2 + Tsu - (Tclk1 + Tco +Tdata) ???=10 + 1.806 + 0.025 – (1.868 + 0.078 + 0.332) = 9.553ns 和時序報告計算出來的值吻合。?

? 這樣我們通過公式最終可計算出建立時間的slack值: slack = Tcycle + Tclk2 + Tsu - (Tclk1 + Tco +Tdata) ???=10 + 1.806 + 0.025 – (1.868 + 0.078 + 0.332) = 9.553ns 和時序報告計算出來的值吻合。?

-

時鐘

+關(guān)注

關(guān)注

11文章

1901瀏覽量

133203 -

時序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

23794 -

Vivado

+關(guān)注

關(guān)注

19文章

835瀏覽量

68740

原文標(biāo)題:如何閱覽vivado工程的時序分析報告——建立時間

文章出處:【微信號:雷達(dá)通信電子戰(zhàn),微信公眾號:雷達(dá)通信電子戰(zhàn)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

FPGA實(shí)戰(zhàn)演練邏輯篇65:CMOS攝像頭接口時序設(shè)計5時序報告

調(diào)用timequest工具對工程時序進(jìn)行分析

時序基礎(chǔ)分析

正點(diǎn)原子FPGA靜態(tài)時序分析與時序約束教程

如何讀懂FPGA開發(fā)過程中的Vivado時序報告?

如何讀懂時序分析報告

如何讀懂時序分析報告

評論