內(nèi)存層次結(jié)構(gòu)的變化是穩(wěn)定的,但是訪問內(nèi)存的方式和位置會產(chǎn)生很大的影響。

數(shù)據(jù)的指數(shù)增長和對提高數(shù)據(jù)處理性能的需求催生了各種新的處理器設(shè)計和封裝方法,但它也推動了內(nèi)存方面的巨大變化。

雖然底層技術(shù)看起來仍然非常熟悉,但真正的轉(zhuǎn)變在于這些存儲器與系統(tǒng)內(nèi)處理元件和各種組件的連接方式。這會對系統(tǒng)性能、功耗甚至整體資源利用率產(chǎn)生重大影響。

多年來出現(xiàn)了許多不同類型的存儲,盡管有一些交叉和獨特的用例,但大多數(shù)都有明確的用途。其中包括 DRAM 和 SRAM、閃存和其他專用存儲器。DRAM 和 SRAM 是易失性存儲器,這意味著它們需要電源來維護數(shù)據(jù)。非易失性存儲器不需要電力來保留數(shù)據(jù),但讀/寫操作的數(shù)量是有限的,并且它們會隨著時間的推移而磨損。

所有這些都適合所謂的內(nèi)存層次結(jié)構(gòu),從SRAM開始——一種非常快速的內(nèi)存,通常用于各種級別的緩存。SRAM 速度極快,但由于每比特成本高,其應(yīng)用受到限制。同樣在最低級別,通常嵌入到 SoC 或連接到 PCB 的 NOR 閃存通常用于啟動設(shè)備。它針對隨機訪問進行了優(yōu)化,因此它不必遵循任何特定的存儲位置順序。

在內(nèi)存層次結(jié)構(gòu)中向上移動一步,DRAM是迄今為止最受歡迎的選擇,部分原因是它的容量和彈性,部分原因是它的每比特成本低。這部分是由于領(lǐng)先的 DRAM 供應(yīng)商已經(jīng)全面折舊他們的晶圓廠和設(shè)備,但隨著新型 DRAM 的上線,價格一直在上漲,為新的競爭對手打開了大門。

幾十年來,人們一直在談?wù)撘〈?DRAM,但事實證明,從市場的角度來看,DRAM 比任何人預(yù)期的都要更有彈性。在高帶寬內(nèi)存(HBM) 的 3D 配置中,它也被證明是一種極快、低功耗的選擇。

JEDEC 定義了四種主要類型的 DRAM:

標準內(nèi)存的雙倍數(shù)據(jù)速率 (DDRx);

低功耗 DDR (LPDDRx),主要用于移動或電池供電設(shè)備;

圖形 DDR (GDDRx),最初是為高速圖形應(yīng)用程序設(shè)計的,但也用于其他應(yīng)用程序,以及

高帶寬內(nèi)存 (HBMx),主要用于高性能應(yīng)用,例如 AI 或數(shù)據(jù)中心內(nèi)部。

與此同時,NAND 閃存通常用作可移動存儲(SSD/USB 記憶棒)。由于較長的擦除/寫入周期和較低的使用壽命,閃存不適合 CPU/GPU 和系統(tǒng)應(yīng)用。 “內(nèi)存標準機構(gòu) JEDEC 正在完善雙倍數(shù)據(jù)速率 (DDR5) 和低功耗版本的 LPDDR5 規(guī)范,”西門子 EDA解決方案產(chǎn)品工程師 Paul Morrison 說。“DDR6 和 LPDDR6 也在開發(fā)中。其他流行的 DRAM 內(nèi)存包括高帶寬內(nèi)存(HBM2 和 HBM3)和圖形 DDR(GDDR6,即將發(fā)布 GDDR7)。” 但小型電池供電設(shè)備的增長以及對設(shè)備快速啟動的需求也推高了對閃存的需求。NOR 閃存通常更小,約為 1 Gbit。相比之下,NAND 閃存用于 SSD。密度現(xiàn)在從每單元一位到每單元四位不等,預(yù)計每單元有五位和六位版本。此外,從 2D 到 3D 陣列的轉(zhuǎn)變進一步增加了密度。 “在 AI 和許多其他領(lǐng)域,內(nèi)存性能對于良好的系統(tǒng)性能至關(guān)重要,” Rambus的研究員和杰出發(fā)明家 Steven Woo 說。“以最高數(shù)據(jù)速率運行內(nèi)存將提高系統(tǒng)性能,但考慮數(shù)據(jù)結(jié)構(gòu)如何映射到內(nèi)存可以提高帶寬、功率效率和容量利用率。增加內(nèi)存容量還可以帶來更好的性能,而 CXL 的引入將為 AI 和其他處理器提供一種方式來增加內(nèi)存容量,這超出了直連內(nèi)存技術(shù)目前所能提供的范圍。”

距離很重要

內(nèi)存和處理器之間的距離曾經(jīng)是一個平面規(guī)劃問題,但隨著需要處理的數(shù)據(jù)量的增加以及功能的縮小,在內(nèi)存和處理器之間來回移動更多數(shù)據(jù)所需的能量元素增加。更細的電線需要更多的能量來移動電子,而將它們移動更長的距離需要更多的能量并增加延遲。 這引發(fā)了對近內(nèi)存和內(nèi)存計算的新興趣,其中至少一些數(shù)據(jù)可以被分區(qū)和優(yōu)先處理、處理和顯著減少。這減少了使用的能源總量,并且可能對性能產(chǎn)生重大影響。 內(nèi)存計算(又名內(nèi)存處理或內(nèi)存計算)是指在內(nèi)存(例如 RAM)內(nèi)進行處理或計算。前段時間,在芯片級完成此操作之前,已經(jīng)證明通過將數(shù)據(jù)分布在多個 RAM 存儲單元并結(jié)合并行處理,在投資銀行等案例中的性能提高了 100 倍。因此,雖然內(nèi)存/近內(nèi)存計算已經(jīng)存在了很長時間,并且從 AI 設(shè)計中得到了又一次推動,但直到最近芯片制造商才開始展示這種方法的一些成功。 2021 年,三星的內(nèi)存業(yè)務(wù)部門推出了在 HBM 內(nèi)存中集成 AI 內(nèi)核的內(nèi)存處理 (PIM) 技術(shù)。在使用 Xilinx Virtex Ultrascale 和 (Alveo) AI 加速器的語音識別測試中,PIM 技術(shù)能夠?qū)崿F(xiàn) 2.5 倍的性能提升和 62% 的能耗降低。SK 海力士和美光科技等其他存儲芯片制造商也在研究這種方法。 在內(nèi)存計算領(lǐng)域,最近獲得博士學(xué)位的萬維爾領(lǐng)導(dǎo)的國際研究團隊宣布了一項突破性進展。畢業(yè)于斯坦福大學(xué) Philip Wong 的實驗室,他在加州大學(xué)圣地亞哥分校從事這個想法。其他博士為這項研究做出重大貢獻的加州大學(xué)圣地亞哥分校的畢業(yè)生現(xiàn)在在圣母大學(xué)和匹茲堡大學(xué)經(jīng)營自己的實驗室。 通過將神經(jīng)形態(tài)計算與電阻式隨機存取存儲器緊密結(jié)合,NeuRRAM 芯片以高精度執(zhí)行 AI 邊緣計算——在 MNIST 手寫數(shù)字識別任務(wù)上的準確率達到 99%,在 CIFAR-10 圖像分類任務(wù)上達到 85.7%。與當今最先進的邊緣 AI 芯片相比,NeuRRAM 芯片能夠提供低 1.6 到 2.3 倍的能量延遲積(EDP;越少越好)和高 7 到 13 倍的計算密度。這為降低運行各種 AI 任務(wù)的芯片的功率提供了機會,同時又不影響未來幾年的準確性和性能。 “提高內(nèi)存性能的關(guān)鍵因素之一一直是最大限度地減少數(shù)據(jù)移動,”西門子 EDA 技術(shù)產(chǎn)品經(jīng)理 Ben Whitehead 說。“通過這樣做,它還可以降低功耗。以 SSD 為例,一次數(shù)據(jù)查找可以將傳輸速度提高 400 到 4000 倍。另一種方法是將計算移到內(nèi)存附近。內(nèi)存計算的概念并不新鮮。在內(nèi)存中添加智能將減少數(shù)據(jù)移動。該概念類似于邊緣計算,通過執(zhí)行本地計算而不是來回將數(shù)據(jù)發(fā)送到云。DRAM 中的內(nèi)存計算仍處于早期階段,但這將繼續(xù)成為未來內(nèi)存發(fā)展的趨勢。”

內(nèi)存標準更新

目前正在進行的三個主要標準組/工作可能會對所有這些產(chǎn)生重大影響: JEDEC:組織繼續(xù)其 50 多年來作為微電子行業(yè)內(nèi)存標準領(lǐng)導(dǎo)機構(gòu)的角色。它開發(fā)并發(fā)布了許多標準,重點關(guān)注主內(nèi)存(DDR4 和 DDR5 SDRAM)、閃存(UFS、e.MMC、SSD、XFMD)、移動內(nèi)存(LPDDR、Wide I/O)等。它將繼續(xù)成為內(nèi)存標準的主導(dǎo)機構(gòu)。 JEDEC 最近發(fā)布了兩個新標準。2022 年 8 月,它發(fā)布了 DDR5 SDRAM 規(guī)范,該規(guī)范定義了 x4、x8 和 x16 DDR5 SDRAM 設(shè)備的 8 Gb 到 32 Gb 的最低要求。這項工作是基于 DDR4 標準以及部分 DDR、DDR2、DDR3 和 LPDDR4 標準完成的。此外,2021 年 7 月 JEDEC 增加了 LPDDR5 和 LPDDR5X,定義密度范圍從 2 Gb 到 32 Gb 的 x16 單通道 SDRAM 設(shè)備和 x8 單通道 SDRAM 設(shè)備的最低要求。這項工作是根據(jù)以前的規(guī)范完成的,包括 DDR2、DDR3、DDR4、LPDDR、LPDDR2、LPDDR3 和 LPDDR4。 CXL:CXL聯(lián)盟是一個開放的行業(yè)標準組,支持 Compute Express Link ( CXL ),這是一種行業(yè)支持的高速緩存一致性互連,用于處理器、內(nèi)存擴展和加速器。該技術(shù)定義了 CPU 內(nèi)存空間和附加設(shè)備上的內(nèi)存之間的互連,以實現(xiàn)資源共享,這可以提高性能,同時最大限度地降低軟件和系統(tǒng)成本。它還有助于定義 AI/ML 中使用的加速器。該聯(lián)盟最近發(fā)布了 CXL 2.0 規(guī)范,該規(guī)范增加了開關(guān)功能,以啟用設(shè)備扇出、內(nèi)存擴展、擴展、內(nèi)存池、鏈路級完整性和數(shù)據(jù)加密 (CXL IDE) 以保護數(shù)據(jù)。 UCIe:在小芯片方面是最近發(fā)布的通用小芯片互連快速(UCIe) 標準。芯片制造商將繼續(xù)采用 UCIe 連接小芯片,包括存儲器。當前的重點包括物理層(具有行業(yè)領(lǐng)先 KPI 的芯片到芯片 I/O)和協(xié)議 (CXL/PCIe),以確保互操作性。 “CXL 幫助加速器與系統(tǒng)的其他部分保持一致,因此傳遞數(shù)據(jù)、消息和執(zhí)行信號量更加高效,”英特爾高級研究員兼 CXL 聯(lián)盟委員會技術(shù)任務(wù)組主席 Debendra Das Sharma 說。“此外,CXL 解決了這些應(yīng)用程序的內(nèi)存容量和帶寬需求。CXL 將推動內(nèi)存技術(shù)和加速器的重大創(chuàng)新。”

關(guān)于性能優(yōu)化的想法

其中一些內(nèi)存方法已經(jīng)存在了幾十年,但沒有什么是靜止的。內(nèi)存仍然被視為功率、性能和面積/成本范式中的關(guān)鍵元素,權(quán)衡可能會對所有這些元素產(chǎn)生重大影響。 “內(nèi)存技術(shù)不斷發(fā)展,”西門子 EDA 產(chǎn)品經(jīng)理 Gordon Allan 說。“例如,HBM 是目前 AI 應(yīng)用程序的完美選擇,但明天可能會有所不同。主要內(nèi)存標準機構(gòu) JEDEC 定義了 DDR4 和 5、DIMM 4 和 5、LRDIM 以及當今的其他內(nèi)存。但對于未來的內(nèi)存擴展,用于定義 PCIe 和 UCIe 接口的 CXL 標準正在獲得認可和發(fā)展勢頭。” 每個處理器都需要內(nèi)存來存儲數(shù)據(jù)。因此,了解內(nèi)存的特性及其行為將如何影響整體系統(tǒng)性能非常重要。設(shè)計和選擇存儲器的一些關(guān)鍵考慮因素包括:

在給定的能量單位內(nèi)最大化性能;

功率預(yù)算和熱管理;

將內(nèi)存與處理需求相匹配,例如需要更高內(nèi)存性能的 AI 系統(tǒng),以及重復(fù)使用設(shè)計、密度和封裝(2D、2.5D、3D-IC)

根據(jù)應(yīng)用程序,考慮數(shù)據(jù)如何在系統(tǒng)內(nèi)和系統(tǒng)之間傳輸也很重要。 “要優(yōu)化性能,您需要關(guān)注系統(tǒng)級別,” Cadence DDR、HBM、閃存/存儲和 MIPI IP 集團產(chǎn)品營銷總監(jiān) Marc Greenberg 說. “為了讓您的系統(tǒng)實現(xiàn)高吞吐量,它可能需要 80 多個內(nèi)存連接到處理器。有不同的方法可以提高效率。其中之一是優(yōu)化流量訪問的順序,并在給定時鐘頻率下以最小總線周期完成的任務(wù)數(shù)量最大化。一個簡單的類比是雜貨店的結(jié)賬過程。例如,客戶有五罐菠蘿、一個西瓜和其他東西。為了提高結(jié)賬效率,您可以將所有五個罐頭作為一組呈現(xiàn),而不是先呈現(xiàn)一個罐頭,然后是西瓜,然后是另一個罐頭。同樣的概念也適用于內(nèi)存。此外,在一個點上擁有一個智能內(nèi)存控制器(PHY 和控制器 IP)來管理多個內(nèi)存的流量協(xié)議將在內(nèi)存設(shè)計中實現(xiàn)更好的優(yōu)化。” 人工智能在許多設(shè)備中的推出使這些考慮變得更加重要。 “在 AI 訓(xùn)練中,提供最高帶寬、容量和功率效率的存儲器很重要,”Rambus 的 Woo 說。“HBM2E 內(nèi)存非常適合許多訓(xùn)練應(yīng)用,尤其是大型模型和大型訓(xùn)練集。使用HBM2E的系統(tǒng)實現(xiàn)起來可能更復(fù)雜,但如果可以容忍這種復(fù)雜性,那么它是一個不錯的選擇。另一方面,對于許多推理應(yīng)用程序來說,需要高帶寬、低延遲和良好的功率效率,同時具有良好的性價比。對于這些應(yīng)用,GDDR6 內(nèi)存可能更適合。對于物聯(lián)網(wǎng)等端點應(yīng)用,也可以與 LPDDR 結(jié)合使用的片上存儲器是有意義的。”

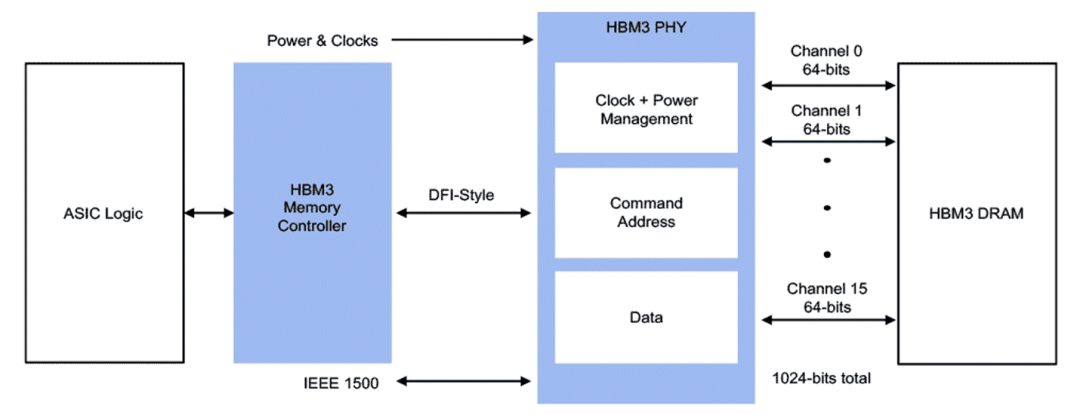

HBM 內(nèi)存控制器和 PHY IP 優(yōu)化了內(nèi)存管理功能 根據(jù)美光的說法,內(nèi)存系統(tǒng)比看起來更復(fù)雜。在給定的內(nèi)存帶寬內(nèi),系統(tǒng)性能可能會受到訪問模式、位置和解決時間等因素的影響。例如,自然語言處理模型需要 50 TB/s 的內(nèi)存帶寬來支持 7mS 的延遲時間來解決問題。如果可以容忍更長的延遲,則可以相應(yīng)地調(diào)節(jié)它們的內(nèi)存帶寬。 美光指出,架構(gòu)會隨著對解決方案堆棧的全面了解而得到改進——從軟件到架構(gòu)再到內(nèi)存系統(tǒng)。因此,出發(fā)點是優(yōu)化算法內(nèi)的訪問模式、數(shù)據(jù)放置和延遲緩解(即數(shù)據(jù)預(yù)取),同時利用內(nèi)存架構(gòu)的固有優(yōu)勢并解決其局限性。 JEDEC 不斷改進內(nèi)存,以應(yīng)對更高密度、低延遲、低功耗、更高帶寬等挑戰(zhàn)。通過遵循規(guī)范,內(nèi)存制造商和系統(tǒng)設(shè)計人員將能夠利用新的創(chuàng)新。近年來,來自 Synopsys 和 Siemens EDA 等公司的先進工具已可用于執(zhí)行所需的功能,例如測試、仿真和驗證。 “JEDEC 的目標之一是繼續(xù)提供支持進一步擴展的架構(gòu)創(chuàng)新,”新思科技定制設(shè)計與制造集團的產(chǎn)品營銷總監(jiān) Anand Thiruvengadam 說。“更新的內(nèi)存規(guī)格將繼續(xù)實現(xiàn)更高的密度、更低的功耗和更高的性能。例如,DDR4 的電源要求是 1.2V,而 DDR 5 是 1.1V。在此電壓縮放期間,必須考慮信號完整性和如何打開眼圖等因素。熱管理也得到了改進。DDR5 每個引腳有兩到三個溫度傳感器,比只有一個的 DDR4 有所改進。因此,遵循規(guī)范是有益的。” 但遵循規(guī)范是一回事。滿足規(guī)范是另一回事。“根據(jù)規(guī)范測試產(chǎn)品很重要,確保它通過所有最壞的情況,”Thiruvengadam 說。“復(fù)雜的分析和模擬可能需要數(shù)周時間。幸運的是,更新的仿真軟件解決方案可以將這一時間縮短到幾天。”

結(jié)論

JEDEC 將繼續(xù)定義和更新存儲器規(guī)格,涵蓋 DRAM、SRAM、FLASH 等。隨著 CXL 和 UCIe 標準的加入,內(nèi)存開發(fā)社區(qū)將受益于未來的系統(tǒng)和小芯片互連。盡管 UCIe 相對較新,但它有望在生態(tài)系統(tǒng)中開辟小芯片的新世界。 此外,預(yù)計 AI/ML 將繼續(xù)推動對高性能、高吞吐量內(nèi)存設(shè)計的需求。持續(xù)的斗爭將是平衡低功耗要求和性能。但涉及內(nèi)存計算的突破將為世界帶來更快的發(fā)展加速。更重要的是,這些先進的內(nèi)存開發(fā)將有助于推動未來基于人工智能的邊緣和端點 (IoT) 應(yīng)用。

審核編輯 :李倩

-

存儲器

+關(guān)注

關(guān)注

38文章

7643瀏覽量

166857 -

RAM

+關(guān)注

關(guān)注

8文章

1391瀏覽量

117125 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3117瀏覽量

75125 -

JEDEC

+關(guān)注

關(guān)注

1文章

37瀏覽量

17690

原文標題:如何通過內(nèi)存設(shè)計來優(yōu)化系統(tǒng)性能?

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

RDMA簡介3之四種子協(xié)議對比

變頻器主要支持哪四種模式?有什么區(qū)別?

四種常見ADC的特性和應(yīng)用

私藏技術(shù)大公開!四種常見供電方案

被問爆的四種供電方式,來啦~

JEDEC定義了四種主要類型的DRAM

JEDEC定義了四種主要類型的DRAM

評論