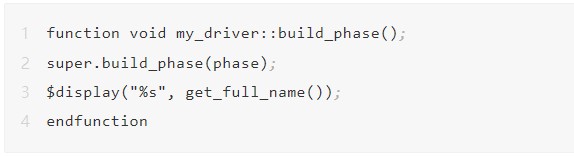

一個component(如my_driver)內通過get_full_name()函數可以得到此component的路徑

config_db機制用于在UVM驗證平臺間傳遞參數。它們通常都是成對出現的。set函數是寄信,而get函數是收信。如下設置當前名字為pre_num=100寄信給drive

uvm_config_db#(int)::set(this, "env.i_agt.drv", "pre_num", 100);

其中第一個和第二個參數聯合起來組成目標路徑,與此路徑符合的目標才能收信。第一個參數必須是一個uvm_component實例的指針,第二個參數是相對此實例的路徑。第三個參數表示一個記號,用以說明這個值是傳給目標中的哪個成員的,第四個參數是要設置的值。set函數的第一個參數為null時,在這種情況下,UVM會自動把第一個參數替換為uvm_ root::get()。

假如把this替換為了this.env,第二個參數是my_driver相對于env的路徑

uvm_config_db#(int)::set(this.env, "i_agt.drv", "pre_num_max", 100);

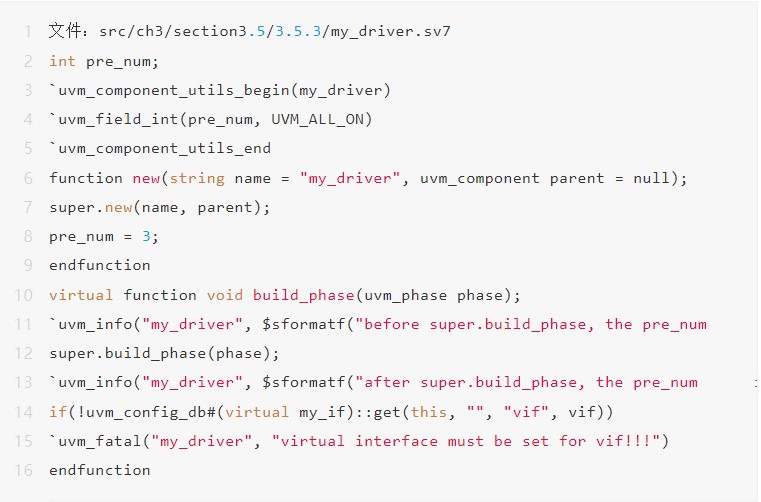

在driver中的build_phase使用如下方式收信

uvm_config_db#(int)::get(this, "", "pre_num", pre_num);

get函數中的第一個參數和第二個參數聯合起來組成路徑。第一個參數也必須是一個uvm_component實例的指針,第二個參數是相對此實例的路徑。一般的,如果第一個參數被設置為this,那么第二個參數可以是一個空的字符串。第三個參數就是set函數中的第三個參數,這兩個參數必須嚴格匹配,第四個參數則是要設置的

set與get函數一般都是成對出現,但是在某些情況下,是可以只有set而沒有get語句,即省略get語句。

只要使用uvm_field_int注冊,并且在build_phase中調用super.build_phase(),就可以省略在build_phase中的如下get語句

uvm_config_db#(int)::get(this, "", "pre_num", pre_num);

關鍵是build_phase中的super.build_phase語句,當執行到driver的super.build_ phase時,會自動執行get語句。

審核編輯:劉清

-

UVM

+關注

關注

0文章

182瀏覽量

19433

原文標題:UVM的config機制

文章出處:【微信號:FPGA學姐,微信公眾號:FPGA學姐】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

恩智浦MCU MCXN947 基于MCUXpresso Config tools創建IIC的教程步驟

模擬地和數字地混合PCB布局探討

復旦微電子與支付寶推出“碰一下”射頻芯片

你家也有“隱形守護者”?Rd-03雷達模組了解一下

ADS1115的Config Register在什么時候配置比較好?

“碰一下”支付背后的4G技術

支付寶發布新一代AI視覺搜索“探一下”

深入探討Linux系統中的動態鏈接庫機制

MySQL編碼機制原理

單片機的中斷機制

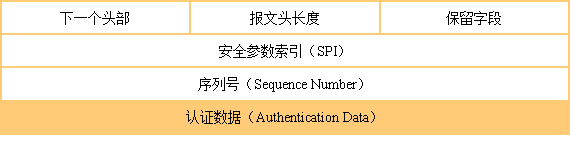

IPv6 Sec機制的深度解析與優勢探討

自感線圈斷電時燈泡為啥會閃亮一下

歡創播報 支付寶“碰一下”正式發布

探討一下UVM的config機制

探討一下UVM的config機制

評論