存儲供應(yīng)商正在競相為 3D NAND 添加更多層,這是一個(gè)由數(shù)據(jù)爆炸和對更高容量固態(tài)驅(qū)動器和更快訪問時(shí)間的需求驅(qū)動的競爭市場。

美光已經(jīng)在完成 232 層 NAND 的訂單,而且不甘示弱,SK 海力士宣布將于明年上半年開始量產(chǎn) 238 層 512Gb 三層單元 (TLC) 4D NAND。或許更重要的是,芯片制造商私下表示,他們將利用行業(yè)學(xué)習(xí)為目前正在開發(fā)的 3D-IC 堆疊 NAND。

西門子 EDA技術(shù)產(chǎn)品經(jīng)理 Ben Whitehead 表示:“處理器的摩爾定律在過去幾年中一直滯后,但對于 NAND 閃存來說仍然存在并且很好。”“這是一件好事,因?yàn)楝F(xiàn)代計(jì)算和網(wǎng)絡(luò)對快速存儲有著無法滿足的需求。”

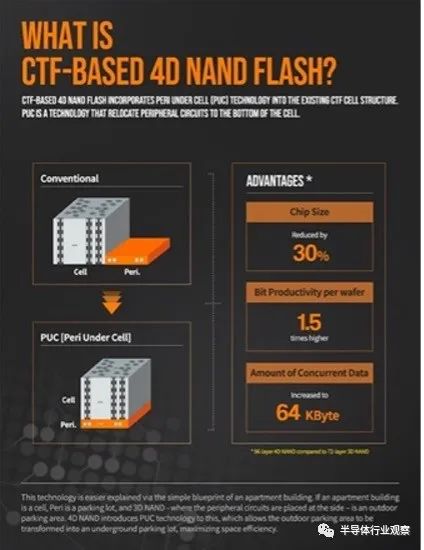

SK 海力士于 2018 年推出了 96 層 NAND 的 4D 命名法。盡管有這個(gè)名字,但該公司并未在四維空間中創(chuàng)建其產(chǎn)品或模仿 tesseract 立方體。但這個(gè)詞也不完全是營銷噱頭。它是 3D 架構(gòu)變體的商品名。

“對于 DRAM,大約需要 10 或 15 年的研發(fā)才能取得成果,但對于 3D NAND,發(fā)展速度非常快。當(dāng)你想到通常的開發(fā)速度時(shí),你會感到驚訝,” Synopsys研發(fā)總監(jiān)Xi-Wei Lin說。“除了技術(shù)本身,它還是一款殺手級應(yīng)用。蘋果是第一個(gè)放入閃存來存儲數(shù)據(jù)的。今天,我們買 iPhone 還是看內(nèi)存有多少,而且都是閃存。從那里開始,大數(shù)據(jù)、人工智能和分析需要高性能計(jì)算。閃存正在填補(bǔ)硬盤驅(qū)動器和 RAM 內(nèi)存之間的這一關(guān)鍵延遲差距。由于功耗、外形尺寸和密度成本,您可以看到應(yīng)用程序,尤其是在數(shù)據(jù)中心、分析和游戲領(lǐng)域。”

演變與革命

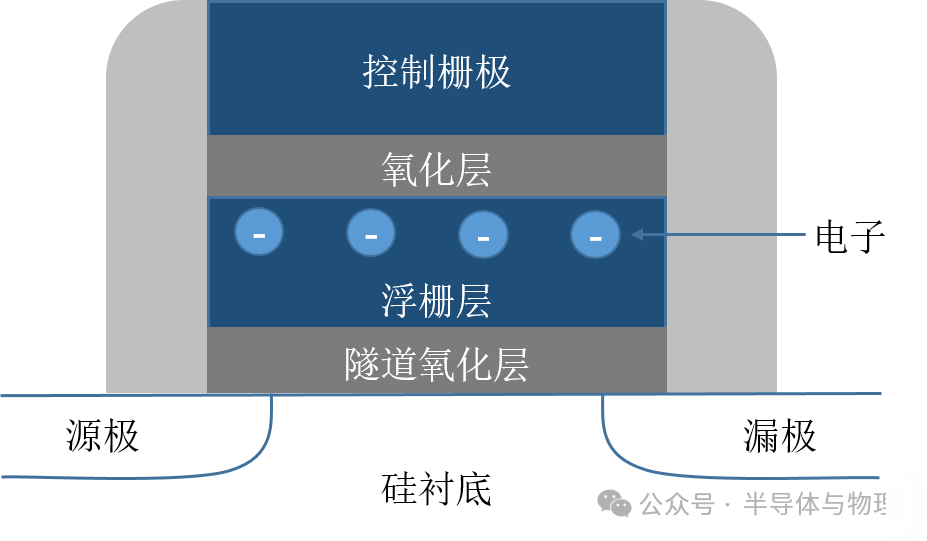

回顧 2D NAND,它具有平面架構(gòu),浮柵 (FG) 和外圍電路彼此相鄰。2007 年,隨著 2D NAND 達(dá)到其規(guī)模極限,東芝提出了 3D NAND 結(jié)構(gòu)。

三星在 2013 年率先推出了其所謂的“V-NAND”。

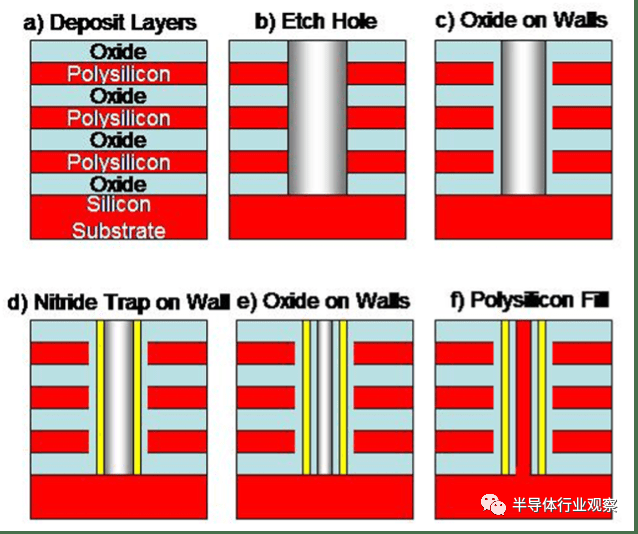

3D 設(shè)計(jì)引入了多晶硅和二氧化硅的交替層,并將浮柵交換為電荷陷阱閃存 (CTF)。區(qū)別既有技術(shù)上的,也有經(jīng)濟(jì)上的。FG 將存儲器存儲在導(dǎo)電層中,而 CTF 將電荷“捕獲”在電介質(zhì)層中。由于制造成本降低,CTF 設(shè)計(jì)很快成為首選,但肯定不是唯一的。

IBM 研究員 Roman Pletka 指出:“盡管所有制造商都轉(zhuǎn)向電荷陷阱單元架構(gòu),但我預(yù)計(jì)傳統(tǒng)浮柵單元在未來仍將發(fā)揮不可忽視的作用,尤其是對于容量或保留敏感的用例。”

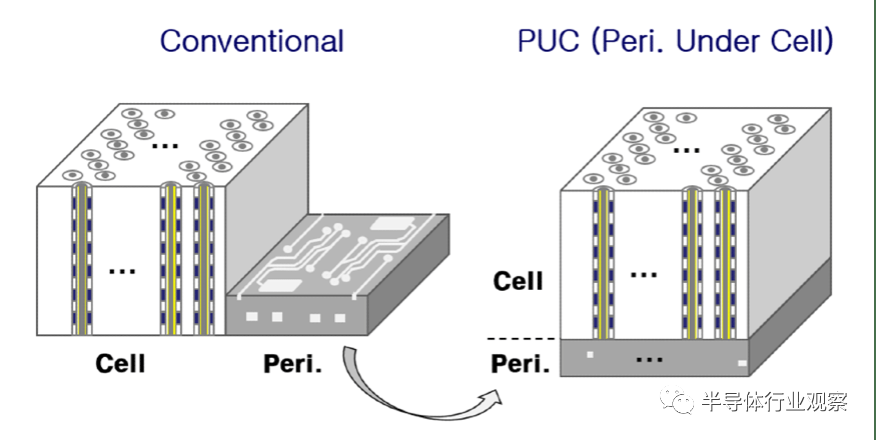

盡管如此,海力士表示,盡管創(chuàng)新了摩天大樓般的堆疊,但第一代 3D NAND 設(shè)計(jì)將外圍電路保留在一邊。

最終,3D NAND 供應(yīng)商將外圍電路移至 CTF 之下。在 SK Hynix 的術(shù)語中,它現(xiàn)在是 Periphery Under Cell (PUC) 層。一方面,說“4D NAND”比 CTF/PUC NAND 更短更酷。另一方面,最終這是 3D NAND 的另一種變體,每單位的單元面積更小。用于更小尺寸的類似設(shè)計(jì)有不同的商品名稱,例如 Micron 的 CMOS under Array (CuA)。

圖 1:SK 海力士對 4D NAND 的解釋。

資料來源:SK 海力士全球新聞編輯室。

圖 2:外圍電路是 4D NAND 的底層。

資料來源:SK 海力士全球新聞編輯室。

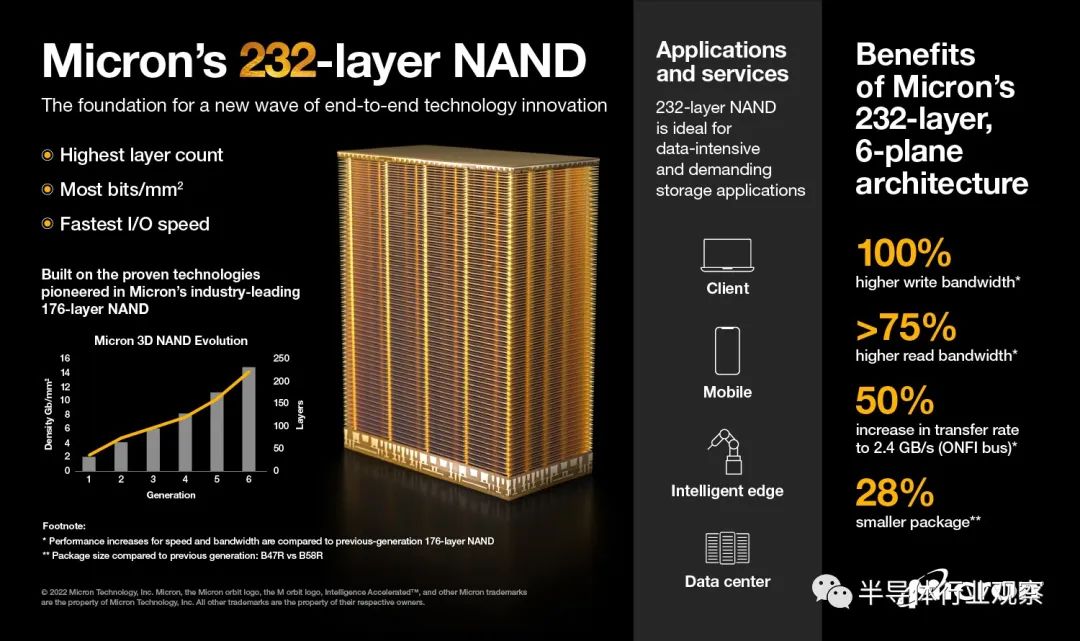

美光本身在 2022 年 7 月下旬宣布推出 232 層 NAND,該產(chǎn)品正在生產(chǎn)中。根據(jù)該公司的新聞稿,美光表示,其 232 層 NAND 是存儲創(chuàng)新的分水嶺,首次證明了在生產(chǎn)中將 3D NAND 擴(kuò)展到 200 層以上的能力。

“添加這些層的主要作用是增加容量,因?yàn)槊總€(gè)人都在尋找更多的 SSD 容量,” Cadence產(chǎn)品營銷集團(tuán)總監(jiān) Marc Greenberg 說。“因此,添加更多層基本上意味著您可以在單一封裝中存儲更多千兆字節(jié),并在單一類型的多層 3D NAND 組件上進(jìn)行存儲。這是一種能力游戲,添加所有這些層和其背后的技術(shù)。”

美光還聲稱擁有業(yè)界最快的 NAND I/O 速度 — 2.4 Gbps — 與上一代產(chǎn)品相比,寫入帶寬提高了 100%,每個(gè)芯片的讀取帶寬提高了 75% 以上。此外,232 層 NAND 包含六平面 TLC 生產(chǎn) NAND,美光表示這是所有 TLC 閃存中每個(gè)裸片最多的平面,并且能夠在每個(gè)平面上獨(dú)立讀取能力。

據(jù)行業(yè)分析師稱,這可能是該公告中最令人印象深刻的部分。由于有六個(gè)平面,這個(gè)芯片可以表現(xiàn)得好像它是六個(gè)不同的芯片。

圖 3:美光的 232 層 NAND。

來源:美光

中國的長江存儲技術(shù)有限公司(YMTC)也宣布推出一款 232 層 3D NAND 模塊。何時(shí)進(jìn)入量產(chǎn)尚不清楚。

制造:優(yōu)勢與挑戰(zhàn)

在去年的 IEEE IEDM 論壇上,三星的 Kinam Kim 發(fā)表了一個(gè)主題演講,他預(yù)測到 2030 年將有 1,000 層閃存。這聽起來可能令人頭暈?zāi)垦#@并不完全是科幻小說。“與 NAND 閃存的歷史趨勢線相比,這已經(jīng)放緩了,”Imec 存儲存儲器項(xiàng)目總監(jiān) Maarten Rosmeulen 說。“如果你看看其他公司,比如美光或西部數(shù)據(jù),他們在公開聲明中提出的內(nèi)容,他們甚至比這還要慢。不同的制造商之間也存在一些差異——似乎他們正在延長路線圖,讓它放慢速度。我們相信這是因?yàn)楸3挚臻g運(yùn)轉(zhuǎn)需要非常高的投資。”

盡管如此,競爭風(fēng)險(xiǎn)仍然足夠高,以至于這些投資是不可避免的。“主要的前進(jìn)方向,主要的乘數(shù),是向堆棧添加更多的層,”Rosmeulen 說。“進(jìn)行 XY 縮小和縮小內(nèi)存孔的空間非常小。這很難做到。也許他們會在這里或那里擠壓幾個(gè)百分點(diǎn),把孔放在一起,孔之間的縫隙更少,諸如此類。但這并不是最大的收獲。如果你能繼續(xù)堆疊更多的層,密度只能以目前的速度顯著提高。”

圖 4:NAND 制造中的 3D 步驟。

資料來源:客觀分析

進(jìn)一步堆疊似乎是合理的,除了整個(gè)過程的核心不可避免的問題。

“主要挑戰(zhàn)在于蝕刻,因?yàn)槟仨毼g刻具有非常高縱橫比的非常深的孔,”Rosmeulen 說。“如果你看看上一代有 128 層,這是一個(gè)大約 6、7 或 8 微米深的孔,只有大約 120 納米直徑,極高的縱橫比——或者可能更高一點(diǎn),但不是那么很多。蝕刻技術(shù)有進(jìn)步,可以一次性蝕刻更深的孔,但不會更快。您無法提高蝕刻速度。因此,如果工藝流程以沉積和蝕刻為主,而這些工藝步驟并沒有提高成本效率,那么添加更多層就不再像降低成本那樣有效。”

蝕刻也只是多個(gè)步驟之一。“除了蝕刻之外,您還需要用非常薄的介電層上下均勻地填充這個(gè)孔,”Synopsys 的 Lin 說。“通常情況下,由于晶圓的化學(xué)性質(zhì),沉積幾納米的層并不容易。在這里,他們必須一路向下才能填滿。有亞原子層沉積方法,但它仍然具有挑戰(zhàn)性。另一個(gè)大挑戰(zhàn)是壓力。如果你建立了如此多的層,這些層會經(jīng)歷一些蝕刻/沉積/清潔/熱循環(huán),這可能會導(dǎo)致局部和全局壓力。在本地,因?yàn)樵谀沣@孔后,你需要在整個(gè)堆棧中切出一個(gè)非常深的溝槽。它變成了一個(gè)非常高的摩天大樓,搖搖欲墜。如果你開始經(jīng)歷一些洗滌或其他過程,很多事情都可能導(dǎo)致兩座摩天大樓相互倒塌。那么你就失去了收益。而且通過將如此多的材料放在一起,切割不同的圖案,這會產(chǎn)生全局應(yīng)力,并導(dǎo)致晶圓翹曲,這將導(dǎo)致晶圓廠無法處理,因?yàn)榫A必須是平的。

這只是開始。請記住,蝕刻正在穿過不同材料的層。”

Objective Analysis 的 Handy 表示,三星的解決方案是創(chuàng)建極薄的層。“這對整個(gè)行業(yè)很有用,因?yàn)槊總€(gè)人都使用幾乎相同的工具來創(chuàng)造這些東西。”

讓它更好地工作

閃存的基本概念也存在固有的功能挑戰(zhàn)。“人們越來越依賴需要越來越強(qiáng)大的糾錯(cuò)算法來與這些設(shè)備一起工作,”Cadence 的 Greenberg 說。

問題是 NAND 閃存設(shè)備內(nèi)置的智能并不多。“通常情況下,SSD 發(fā)生在控制器端,”Greenberg 解釋說。“控制器正在向 NAND 閃存設(shè)備發(fā)送命令,NAND 閃存設(shè)備會做出響應(yīng),但它并沒有太多的智能。它只是響應(yīng)請求,例如針對特定地址的數(shù)據(jù)塊。NAND 閃存設(shè)備將簡單地響應(yīng)該數(shù)據(jù)塊。但是在控制器端,你必須首先對接收到的數(shù)據(jù)進(jìn)行糾錯(cuò),然后確定該塊中是否存在不可接受的錯(cuò)誤數(shù)量,然后決定如何重新映射該塊地址空間并在其位置放置一個(gè)不同的塊。所有這些決定都發(fā)生在控制器端。”

盡管如此,由納米級摩天大樓建造的世界重新強(qiáng)調(diào)了 ONFI 控制器和 ONFI PHYS 等組件,并為設(shè)計(jì)人員提出了新的挑戰(zhàn)。

“內(nèi)存工廠可以生產(chǎn)的層數(shù)使與這些內(nèi)存接口的控制器的設(shè)計(jì)驗(yàn)證問題變得非常復(fù)雜——而且它們可能并不那么明顯。SSD 控制器必須處理更多的內(nèi)存通道。將許多pipeline與越來越快(但永遠(yuǎn)不夠快)的主機(jī)接口連接起來會在非常意想不到的地方產(chǎn)生瓶頸,”西門子的 Whitehead 說。“另一個(gè)設(shè)計(jì)驗(yàn)證挑戰(zhàn)是功率。長期以來,大多數(shù)存儲控制器的優(yōu)先級較低,但現(xiàn)在已轉(zhuǎn)變?yōu)殛P(guān)鍵功能。移動到較小的節(jié)點(diǎn)會有所幫助,但代價(jià)高昂。商業(yè)模式不能容忍重新旋轉(zhuǎn),更不用說供應(yīng)鏈難以排長隊(duì)了。上市時(shí)間的延遲讓高層管理人員非常清楚。存儲的增長動力甚至更多,這需要我們重新思考如何驗(yàn)證設(shè)計(jì)。AI 加速器需要更大的存儲控制器,這可能會很快消耗您的仿真和原型設(shè)計(jì)能力。邊緣智能需要數(shù)量級更復(fù)雜的設(shè)計(jì)驗(yàn)證。內(nèi)存計(jì)算,如 CSD,需要測試新的處理器組合,將 RTOS 和 HTOS 與以前看不見的工作負(fù)載混合在一起。”

這是人們?nèi)绱岁P(guān)注驗(yàn)證 IP 的原因之一。

Siemens Digital Industries Software 的 ICVS 產(chǎn)品經(jīng)理 Joe Hupcey 表示:“使用此 IP 的自動化可以快速生成測試平臺,讓設(shè)計(jì)和驗(yàn)證團(tuán)隊(duì)在幾分鐘內(nèi)啟動并運(yùn)行。”“這種生產(chǎn)力水平使我們能夠?qū)φ麄€(gè)設(shè)計(jì)進(jìn)行架構(gòu)探索,從而盡早對所選擇的權(quán)衡取舍充滿信心。同時(shí),它還建立了自動跟蹤指標(biāo)的框架——如代碼、功能和場景覆蓋率——使團(tuán)隊(duì)能夠衡量他們的進(jìn)度并擁有做出簽核決定所需的數(shù)據(jù)。最后,基于我們在 CXL/PCIe 協(xié)議方面的專業(yè)知識,我們看到通用 Chiplet Interconnect Express (UCIe) 等新興標(biāo)準(zhǔn)在使團(tuán)隊(duì)能夠協(xié)作以快速設(shè)計(jì)和驗(yàn)證這些大規(guī)模可擴(kuò)展內(nèi)存模塊方面發(fā)揮著關(guān)鍵作用。”

此外,Imec 正在探索 3D NAND 的潛在新結(jié)構(gòu)。它展示了所謂的“溝槽架構(gòu)”,這是一種設(shè)計(jì)變體,其中存儲單元是溝槽側(cè)壁的一部分,兩個(gè)晶體管位于溝槽的相對兩端。Imec 鐵電體項(xiàng)目總監(jiān) Jan Van Houdt 解釋了它的價(jià)值:“與目前使用的環(huán)柵(或圓柱形)架構(gòu)相比,3D 溝槽架構(gòu)具有雙倍密度的潛力。”

然而,他接著指出了一些缺點(diǎn)。“有兩個(gè)高縱橫比(=具有挑戰(zhàn)性的)蝕刻步驟而不是一個(gè),以及在閃光情況下隧道氧化物中的電場較低。第二個(gè)缺點(diǎn)在使用鐵電 FET 時(shí)不存在,這使得溝槽版本對鐵比對閃存更有吸引力。”該設(shè)計(jì)仍處于原型階段。

結(jié)論

2016 年,專家指出,由于技術(shù)問題,3D NAND 可能會在 300 層或接近 300 層時(shí)失去動力。這似乎已被今天的謹(jǐn)慎樂觀所取代。

“[在 SK Hynix 的 238 層之后] 我預(yù)計(jì)層數(shù)在未來幾年會以大致相同的速度增加,”IBM 的 Pletka 說。“然而,從技術(shù)角度來看,由于高縱橫比蝕刻工藝,增加層數(shù)受到挑戰(zhàn),而且資本支出也受到挑戰(zhàn),因?yàn)橹圃煨酒臅r(shí)間隨著層數(shù)的增加而增加。這就是為什么我們將通過制作更薄的層、橫向縮放(例如更密集地放置垂直孔)以及使用更高效的布局(例如共享位線和邏輯縮放)來看到新的縮放方向(例如,使用拆分門架構(gòu)或存儲更多每個(gè)單元的位數(shù))。有了這些技術(shù),預(yù)計(jì) NAND 閃存的存儲密度至少在未來 5 到 10 年內(nèi)會以類似的速度增長。”

其他人同意。“當(dāng)人們說我們不能超過這個(gè)層數(shù)時(shí),沒有物理限制,”O(jiān)bjective Analysis 的首席分析師 Jim Handy 說。“在半導(dǎo)體領(lǐng)域,總是有人說我們做不到。我們不能在 20 納米以下進(jìn)行光刻。現(xiàn)在,他們正在研究 1 納米。三星談到了 1,000 層。可能在 20 年后我們會笑,我們曾經(jīng)認(rèn)為這很多。”

審核編輯 :李倩

-

存儲器

+關(guān)注

關(guān)注

38文章

7632瀏覽量

166380 -

堆疊

+關(guān)注

關(guān)注

0文章

37瀏覽量

16808 -

3d nand

+關(guān)注

關(guān)注

4文章

93瀏覽量

29307

原文標(biāo)題:3D NAND,層數(shù)堆疊會有極限嗎?

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

預(yù)期提前,鎧俠再次加速,3D NAND準(zhǔn)備沖擊1000層

佛瑞亞重磅發(fā)布3D“禪境”座椅

使用海爾曼太通/HellermannTyton 3D CAD 模型進(jìn)行快速高效的設(shè)計(jì)

聯(lián)合電子2025年供應(yīng)商大會順利舉行

3D打印中XPR技術(shù)對于打印效果的影響?

TechWiz LCD 3D應(yīng)用:局部液晶配向

騰訊混元3D AI創(chuàng)作引擎正式上線

自帶尺寸標(biāo)注的3D預(yù)覽為制造商組件提供更強(qiáng)勁的客戶體驗(yàn)

TechWiz LCD 3D應(yīng)用:局部液晶配向

3D打印技術(shù),推動手板打樣從概念到成品的高效轉(zhuǎn)化

3D NAND的發(fā)展方向是500到1000層

【半導(dǎo)體存儲】關(guān)于NAND Flash的一些小知識

3D-NAND浮柵晶體管的結(jié)構(gòu)解析

存儲供應(yīng)商正在競相為 3D NAND 添加更多層

存儲供應(yīng)商正在競相為 3D NAND 添加更多層

評論