PCB的設計在產品可靠性設計方面是非常重要的。對于PCB設計在EMI方面的問題考慮:設計工程師通常都非常注意PCB上信號走線的布線,但經常卻沒有考慮他們的返回路徑。理解和解決EMI問題的關鍵是理解電流的流動。電流以環路的形式流動,因此,許多數字電路設計工程師容易忘了這個重要的事實。因為,大多數原理圖的檢查表明,一半的原理圖都忘了地或信號和電源的返回系統。因此就容易忽略了所有的電源和信號的返回路徑,這些信號的布線都是電路板布線人員一時的疏忽才會導致的顯著EMI問題。

通過理解返回電流是如何返回其電源及如何確保返回路徑為低阻抗,就可以很好地解決產品中的EMI問題。

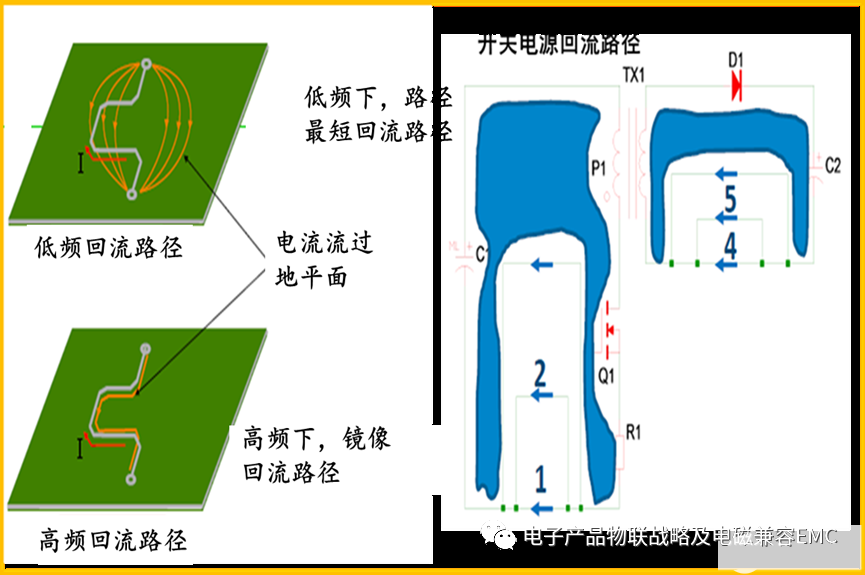

首先,考慮高頻電流是怎樣流動的。在低頻時,返回電流通常沿著電阻最小的路徑流動。在高頻時,返回電流通常沿著阻抗最小的路徑流動。如下圖所示。出現這種現象的原因是:在較高頻率時,當信號或電源導線或PCB走線及與之相關的返回路徑-另外一條導線或返回平面的物理尺寸最小時,其路徑的自感最小。由于這種現象,產生的結果是信號或電源導線中的電流和返回電流通常會使流出電流和輸入電流之間的物理空間最小。如果迫使返回路徑形成了較大的環路面積,這種環路的作用類似于天線,將會產生輻射發射。

不同頻率信號的返回電流路徑示意圖

當頻率大于1MHz時,返回電流通常在信號PCB走線下方或者上方的信號返回平面上直接流動。這取決于信號PCB電路板的層結構。如果迫使返回路徑距信號走線的下面有較長的路徑,那么環路的物理尺寸將變得非常大,通常會產生環天線的輻射發射,同時也將產生共模電壓源。這些電壓源會在PCB的周圍且通常沿著I/O電纜或電源電纜產生共模電流,這些電纜就會像單極子天線或偶極子天線一樣產生輻射發射。

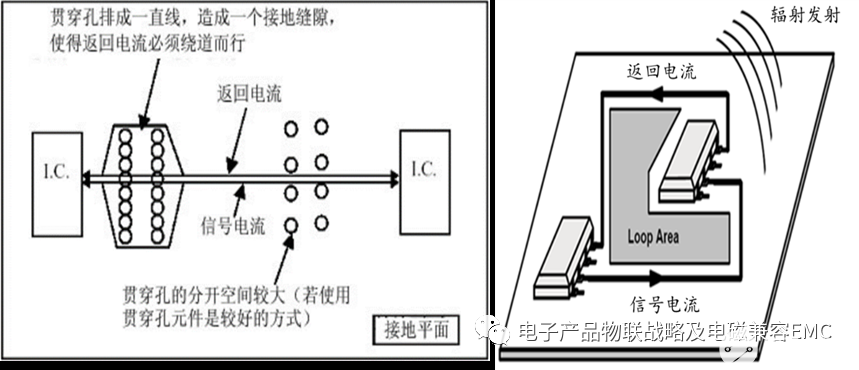

在實際的應用中,常常會發現電子工程師為其產品設計的PCB信號和電源返回平面上存在被疏忽的間隙和分割。這樣就會帶來更大的返回電流路徑,如下圖所示。

電流被PCB強行改變路徑的示意圖

返回電流被強行改變路徑及所產生的環繞PCB的磁場。當迫使返回電流遠離阻抗最小的優先路徑時,會形成環天線,如上圖所示。這就會在整個電路板附近產生磁場,這些磁場也能與其他PCB走線產生耦合,從而有效地形成小的電壓源,電壓源又在電路板附近產生共模電流。這些共模電流然后耦合給I/O電纜或電源電纜,他們會輻射基波信號的高頻諧波。

返回平面的互感產生小的電壓降ΔU=L·(di/dt),這種電壓降會產生共模電流。信號電流環路和附近的另外一個電路環路之間的互感也將會產生電壓差,這種電壓差可在附近的電路中產生電流。

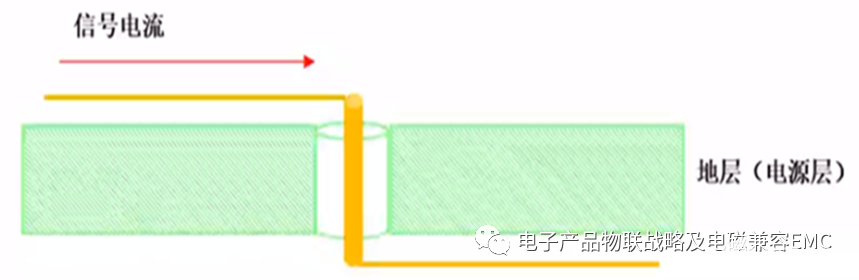

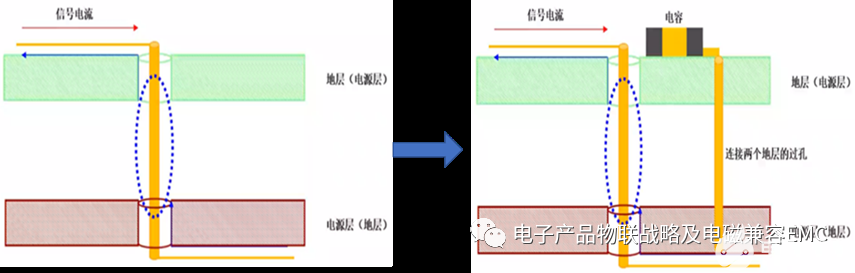

當進行PCB布線時,產生EMI的另外一個常見問題是改變參考平面層,沒有為返回電流的信號PCB走線規定閉合的物理路徑。比如,如果信號PCB走線在參考返回平面的頂部開始布線,穿過過孔,繼續參考到這個相同的返回平面,這是沒有問題的是可以接受的,如下圖所示。

數字信號參考相同的參考面返回電流

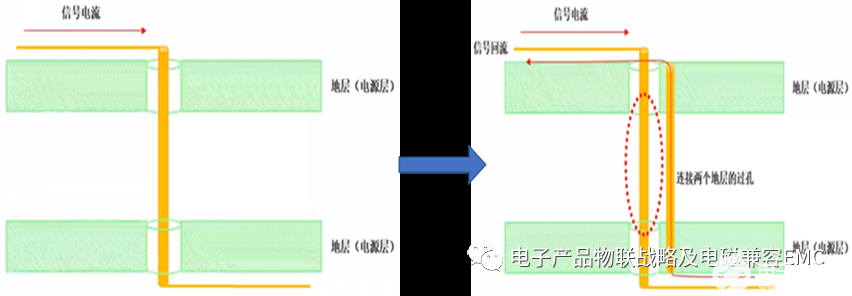

如果出現這樣的情況,一條PCB走線從PCB板子上的一層(參考到信號返回平面)開始,穿過過孔后到達另外一層(其使用不同的參考面)如下圖所示。如果這兩個參考平面(即信號返回的路徑)的電位相同,且兩層通過過孔多次連接在一起,那么規定的返回路徑將具有小的環路面積。這是我們希望的設計。

信號穿過兩層地線層及處理方法

信號在兩層之間換層的處理方法示意圖

在如上面的圖示中,過孔的作用當數字信號參考到兩個不同的平面時,在信號PCB走線的穿過點,如果兩個平面的電位相同,則兩個層之間應使用一個或多個過孔。如果兩個平面的電位不同,那么應盡可能使用兩個或多個縫合電容在信號的穿過點將這兩個平面相連接,優先采用對稱的方式。

然而,如果兩個參考平面具有不同的電位;比如信號返回平面和電源平面,那么返回路徑可能會規劃設計的不好,從而形成了具有較大環路面積的繞行走線,這將會發生常常說到的走線跨分割或裂縫的問題。

為了更好地規劃信號電流的返回路徑,在信號PCB走線設計之初穿過第二個參考平面的地方需要放置附加的過孔。

如果電路足夠復雜以至于可能有太多的參考平面變化,這時就可能需要采用更多層板的設計,以增加附加的信號或電源返回層。

注意:為了實現最佳的高頻噪聲抑制,電源返回“三明治”式的層間距要小-通常認為3~4mil是比較理想的。

通常情況下,電源和電源返回平面之間3~4mil的間距能夠提供好的高頻旁路。因此,去耦電容要均勻地放置在基板面的周圍。然而,如果使用更傳統的10mil間距,那么去耦電容必須從物理上盡可能近地放置在每一個IC的VCC管腳。

另外一種常見錯誤是布線時把數字或大功率的模擬信號PCB走線穿過電路中敏感的模擬電路部分。在布線時數字PCB走線穿過無噪聲的模擬返回平面,數字開關噪聲通常會干擾低電平的模擬信號。

注意:當改變參考平面兩次,這就會迫使返回電流遠離阻抗最小的路徑,這是產生共模電流的最常見的原因。

同時,下面的5個方面在設計時需要注意:

一.接地和搭接

在EMI的故障整改領域中,接地實際上是指產品內電路或組件的返回路徑的分析與設計。在實際工作中,接地經常指的是信號或電源的返回路徑,而不是地或地平面。

為了防止誤解,尤其對于EMI分析,接地也指用于把產品與大地相連接的安全導線接地。搭接:指的是兩塊導電材料通常為金屬片或電纜的屏蔽層之間低阻抗的連接,多次搭接或連接的點之間應具有較低的直流阻抗。比如小于10mΩ,盡管許多標準要求小于2.5mΩ或更小。好的搭接可為電流的流動包括高頻電流確保實體的路徑。

關鍵的問題點是電流必須能夠無阻擋地流回噪聲源端或能量源頭。在實際的應用中并不存在這種具有魔法的孔或地上的某點,即噪聲電流大量流入或消失在這些地方。因此在進行EMI問題的分析時,用信號或電源返回路徑或參考的接地更能準確地表達正確的EMI設計概念。

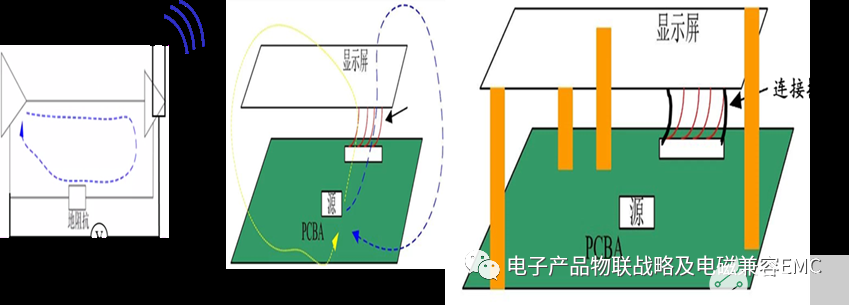

二.產品殼體上的間隙

產品金屬殼體上的間隙,當長度大于大約1/10波長-該波長為產品產生的許多諧波頻率中的任何一個所對應的數據時,其開始作為有效的輻射天線。由于天線既能接收又能發射,因此這些間隙也能使外部的射頻或脈沖能量能進入產品內部,從而引起電路的擾亂及內部信號的誤動作。此外,任何組件,如LCD,也必須在多點進行搭接,如下圖所示。

LCD組件的搭接到屏蔽殼體對于減小發射很重要

注意:當評估屏蔽殼體搭接的完整性時,金屬粘性銅帶或鋁箔都是比較好的故障診斷分析工具。在使用時一定要確定這些粘性的銅帶確實具有連續導電性。

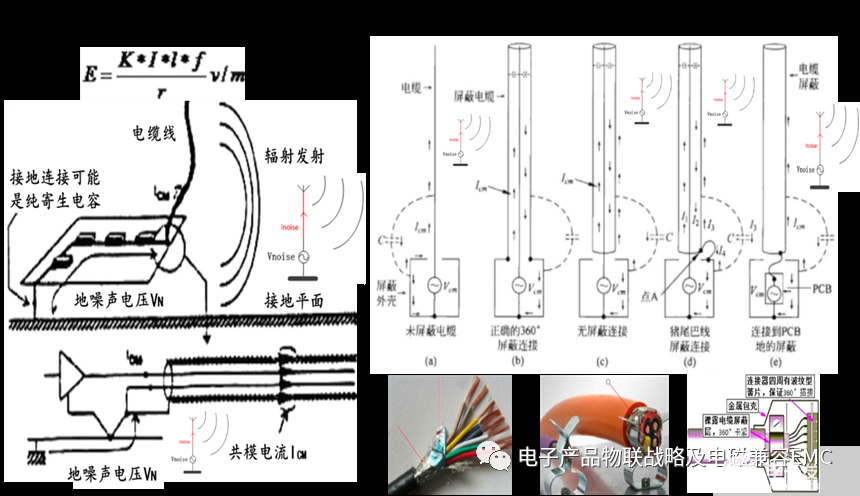

三.連接線電纜的搭接

任何I/O或電源連接器的導電外殼都應與產品的屏蔽殼體進行很好的搭接,這也是非常重要的。由于完整的圓形比如3600搭接有助于阻止電纜的輻射,因此只有采用這種搭接是最佳的。如下圖所示。

連接線電纜搭接及屏蔽與電磁兼容的關系

四.屏蔽

金屬屏蔽體可作為高頻場的屏障。大多數產品都有完全包圍電路的金屬殼體或金屬鍍層的塑料殼體。基于這個原因,確保產品殼體的所有部分很好地搭接在一起則是非常重要的。當需要將連接線電纜穿過產品殼體時就需要一定的技巧。除非電纜連接器搭接到殼體,否則共模噪聲電流將會沿著連接線電纜導線或電纜屏蔽層的外層泄漏。這里的重點是搭接。這必須是非常低阻抗=10mΩ或更小的連接。理想情況下應與產品殼體進行3600搭接,如上圖所示。也就是連接器的所有面都應與產品殼體進行搭接。這意味著涂層比如油漆、鍍層等都將會阻礙好的搭接。因此,低阻抗的3600搭接將會達到最佳的效果。

五.濾波

在設計得很好的產品中通常都會使用濾波器。設計他們的目的是阻止高頻電流-其會產生輻射發射電流的流動或阻止脈沖能量比如ESD、電源線瞬態,或射頻電流進入電路。殼體設計為非屏蔽的產品必須依靠濾波和好的PCB設計、以符合EMI要求。比如,通常使用下面的方法:

(1)開關電源的輸入和輸出都需要進行濾波以平滑直流輸出以及阻止開關噪聲電流通過電源的輸入導線進行發射。

(3)I/O數據線和電源線使用RC濾波器或共模扼流圈。

(4)I/O電纜上所夾的鐵氧體可作為高頻扼流圈。

注意:濾波器的作用是建立高阻抗以阻止連接線電纜上流動的射頻電流或者為電流返回到本地能量源提供低阻抗的路徑。通常如果能實現這兩個目的則是最佳的。其濾波的設計的詳細信息參考《物聯產品電磁兼容分析與設計》。

-

電源

+關注

關注

185文章

18372瀏覽量

256324 -

pcb

+關注

關注

4368文章

23492瀏覽量

409729 -

濾波器

+關注

關注

162文章

8138瀏覽量

182078

發布評論請先 登錄

高速PCB設計抗EMI干擾的九大規則,你都知道嗎?

高速PCB設計解決EMI問題的九大規則

【下載】《PCB設計技巧》 | 一線優秀電子工程師PCB設計進階必備

高速PCB設計中走線屏蔽的各項規則解析

PCB設計EMI的高速信號走線規則

如何通過高速PCB來控制EMI問題?

四大視角看EMC設計:濾波、接地、屏蔽、PCB布局

EMI問題的PCB設計考慮及接地屏蔽濾波分享

EMI問題的PCB設計考慮及接地屏蔽濾波分享

評論