幾乎所有使用MCU的產(chǎn)品,外圍電路都離不開晶振電路設(shè)計,大多數(shù)電子設(shè)計人員從入門開始都會接觸到晶振電路,但實際上,很少有人真正了解晶振電路是如何工作的,在晶振出現(xiàn)問題之前,多數(shù)人不會付出太多精力去關(guān)注振蕩器電路設(shè)計是否合理,通常等到產(chǎn)品量產(chǎn),由于晶振而導致的大面積宕機現(xiàn)象時,才開始注意到晶振電路設(shè)計是否合理。

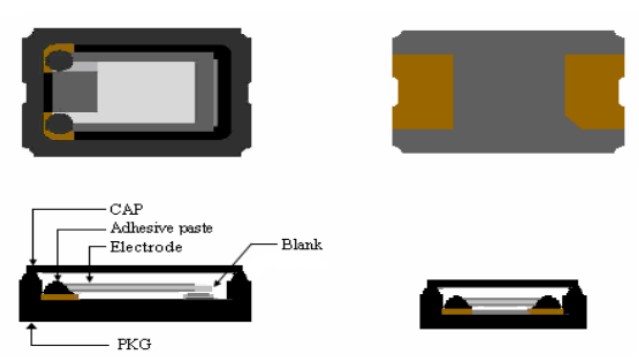

晶振的全稱叫:石英晶體振蕩器。是利用石英晶體的壓電效應(yīng)廠商高精度振蕩頻率的一種電子元件。查看維基百科,對于這種神奇的材料具體的講解是:

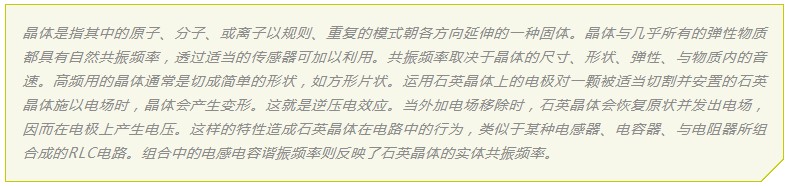

石英晶體等效模型:

Cp:等效電路中與串聯(lián)臂并接的電容(譯注:也叫并電容,靜電電容,其值一般僅與晶振的尺寸有關(guān))。

Ls:(動態(tài)等效電感)代表晶振機械振動的慣性。

Cs:(動態(tài)等效電容)代表晶振的彈性。

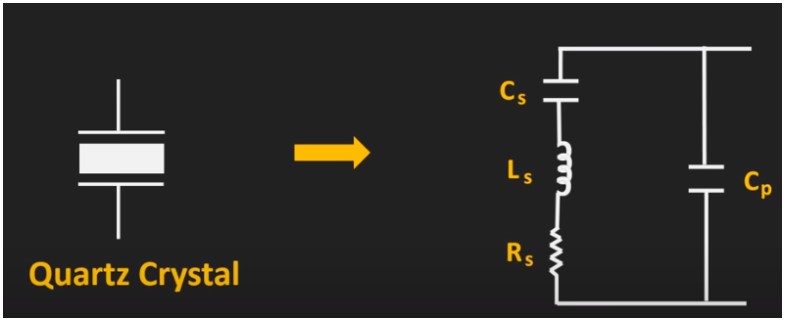

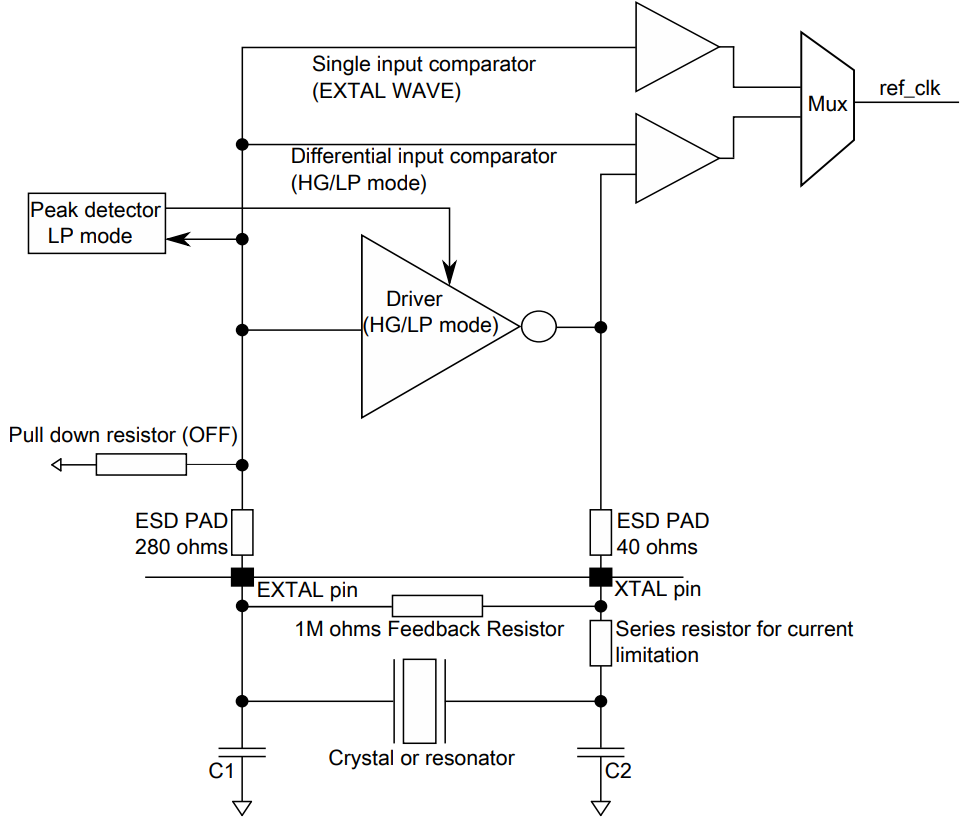

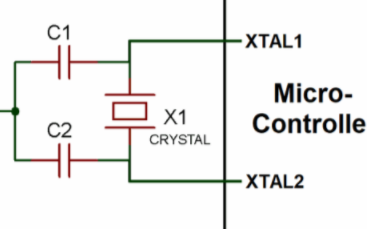

了解晶振電路的設(shè)計,首先你要熟悉Pierce(皮爾斯)振蕩器電路。該模型電路簡單,工作有效而且穩(wěn)定,因此現(xiàn)今幾乎所有的晶振電路設(shè)計都采用這個模型。如下,該設(shè)計包含一個反相器、一個電阻、一個石英晶體、兩個小電容。石英晶體在此扮演高選擇度的濾波元件:

Inv:內(nèi)部反相器器,作用等同于放大器。

Q:石英或陶瓷晶振。

Rf:內(nèi)部反饋電阻(譯注:它的存在使反相器工作在線性區(qū), 從而使其獲得增益,作用等同于放大器)。

RExt:外部限流電阻。

CL1和CL2:兩個外部負載電容。

Cs:由于PCB布線及連接等寄生效應(yīng)引起的等效雜散電容(OSC_IN和OSC_OUT管腳上)

接下來,我們重點關(guān)注內(nèi)部反饋電阻Rf、負載電容Cl、外部限流電阻Rext——

反饋電阻Rf

皮爾斯振蕩器中,連接晶振的芯片內(nèi)部是一個線性的運算放大器,由于運算放大器的電壓增益非常大,范圍從數(shù)百到數(shù)萬倍不等,因此通常使用運算放大器會將輸出端與反向輸入端連接形成一個負反饋組態(tài)(即閉環(huán)放大器)。皮爾斯振蕩器中的反饋電阻Rf可以看成是反相器的偏壓電阻,可以令反相器工作在線性區(qū)域而不至于由于增益過大而工作在完全導通或截止的狀態(tài)。

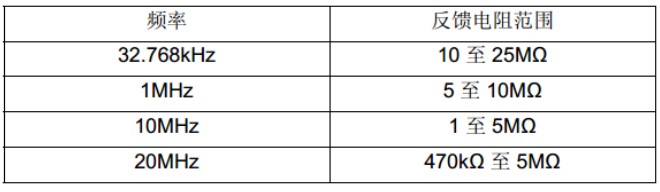

大多數(shù)情況下,Rf是內(nèi)嵌在芯片內(nèi)部中,但不排除有些芯片的設(shè)計并未內(nèi)嵌這個電阻,因此在這種情況下,你會看到有些晶振電路的外部并聯(lián)著一個電阻。不同頻率對應(yīng)的反饋電阻參考值:

負載電容CL

負載電容指連接到晶振上的終端電容,該終端電容包括:外部電容CL1和CL2、印刷電路板上的雜散電容(Cs)。CL的值是晶振本身決定,供應(yīng)商會在規(guī)格書中給出,當晶振外部等效電容等于負載電容CL時,無源晶振輸出的頻率最準確。

CL=(CL1//CL2)+CS

即:CL=[(CL1xCL2)/(CL1+CL2)]+CS

需要注意的是:電容具有充放電的功能,電容容值越大,放電越慢,電容容值越小,放電越快。因此實際調(diào)試中,如果測得的實際頻率比理論值偏小,說明振蕩器振蕩頻率偏慢,電容的放電太慢,等效電容大于負載電容,需要降低外部的匹配電容

外部電阻Rext

在開始闡釋外部電阻之前,我們需要再了解兩個概念:振蕩器增益余量gain、驅(qū)動級別DL——

增益余量gain:表征振蕩電路的放大能力

驅(qū)動級別DL:表征晶振的驅(qū)動功耗

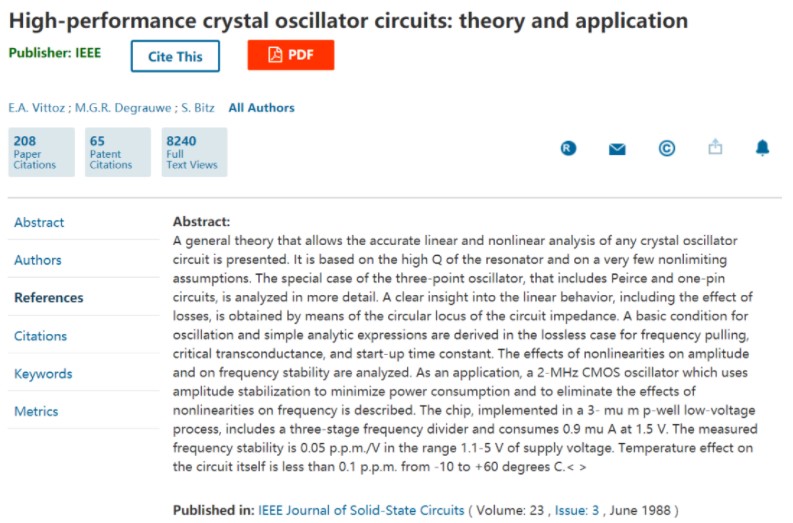

早在1988年, Eric Vittoz發(fā)表了晶振RLC動態(tài)等效電路的相關(guān)理論研究,基于前人的理論,反相器跨導gm必須大于gmcrit才能滿足起振條件,為保證可靠性,還必須滿足至少5倍的關(guān)系;即:gmargin = gm / gmcrit

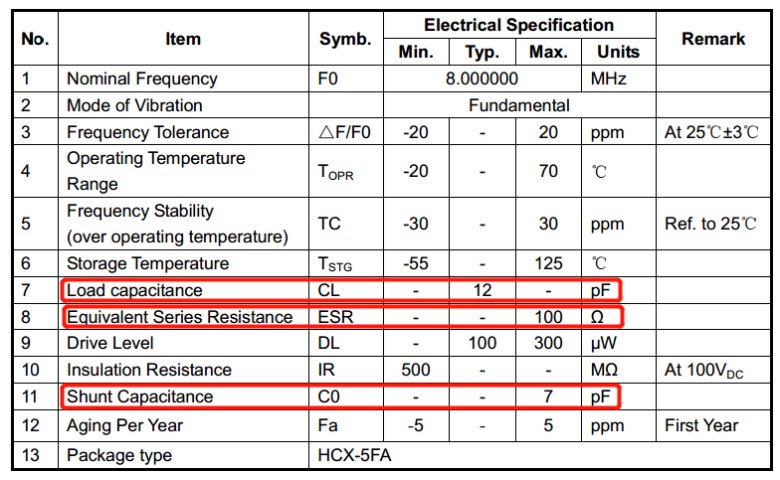

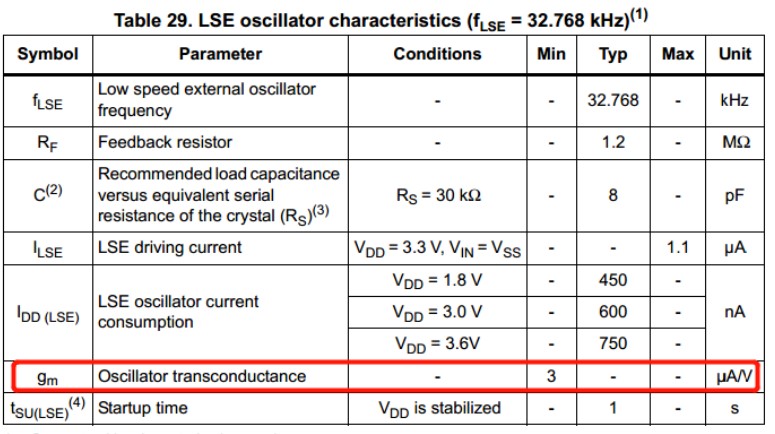

其中,gmcrit = 4 x ESR x (2πF)2 x (C0 + CL)2,ESR、C0、CL都可以從晶振規(guī)格書中獲取,gm從芯片規(guī)格書中獲得;

驅(qū)動級別DL描述的是晶振的功耗,晶振的功耗必須限制在一定范圍內(nèi),否則石英晶體可能會由于過度機械振動而導致不能正常工作。

DL = ESR x I2,其中ESR為晶振的等效串聯(lián)電阻,I為流過晶振的電流的均方根有效值;

你必須讓DL值小于晶振規(guī)格書中限定的DL值,如果實際DL值較高,則需要Rext電阻對驅(qū)動功率進行限制。

對于I的測量需要電流探頭進行測量,而且由于驅(qū)動電流一般比較小,因此需要1mA/mV檔,實際操作中,你可能并沒有分辨率這么高的電流探頭,那么你可以通過觀測晶振引腳輸出波形的形狀進行確認,具體方法我們在下面講。

當你能耐心看到這里,對于晶振設(shè)計的基礎(chǔ)概念、計算已經(jīng)都了解過,接下來,可以搬上我們最終的晶振設(shè)計步驟:

第一步:增益余量的計算

gmcrit = 4 x ESR x (2πF)2 x (C0 + CL)2,ESR、C0、CL都可以從晶振規(guī)格書中獲取,gm從芯片規(guī)格書中獲得;gmargin = gm / gmcrit ,

若gmargin<5,說明這不是一個合格的晶振,你該去挑選一個更低ESR或CL值的晶振;

若gmargin>5,進行第二步;

第二步:外部負載電容計算

CL=(CL1//CL2)+CS

即:CL=[(CL1xCL2)/(CL1+CL2)]+CS

CL為晶振規(guī)格書給出的負載電容,CL1,CL2為所要計算的外部電容,CS為雜散電容(可粗略使用4pf進行計算)

第三步:驅(qū)動級別和外部電阻的計算

用一臺示波器檢測OSC輸出腳,

如果檢測到非常清晰的正弦波,且正弦波的上限值和下限值都符合時鐘輸入需要,則晶振未被過分驅(qū)動;那么祝賀你,你找到了合適的晶振;

如果正弦波形的波峰,波谷兩端被削平,而使波形成為方形,則晶振被過分驅(qū)動。這時就需要用電阻Rext來防止晶振被過分驅(qū)動。判斷電阻RD大小的最簡單的方法就是串聯(lián)一個微調(diào)電阻,從0開始慢慢調(diào)高,一直到正弦波不在被削平為止,這時的電阻值為Rext值。此時,由于需要串聯(lián)Rext,晶振模型的ESR已經(jīng)發(fā)生了改變,因此你需要回到第一步計算gmarin,如果gmarin>5,那么你找到了合適的晶振,如果gmarin<5,那么重新挑選另外一個晶振,重新回到第一步吧。。。

審核編輯:劉清

-

mcu

+關(guān)注

關(guān)注

146文章

17847瀏覽量

360633 -

示波器

+關(guān)注

關(guān)注

113文章

6553瀏覽量

188252 -

振蕩器

+關(guān)注

關(guān)注

28文章

3968瀏覽量

140434 -

晶振電路

+關(guān)注

關(guān)注

7文章

96瀏覽量

25726

發(fā)布評論請先 登錄

關(guān)于晶振電路的測量方案

硬件電路設(shè)計之晶體與晶振電路設(shè)計

怎么判斷晶振是否起振?晶振不起振該怎么辦?

晶振選型設(shè)計有多重要?這些重點關(guān)注對象一定要注意了

無源晶振的選型理念 無源晶振的EMC電路設(shè)計

晶振電路設(shè)計是否合理

晶振電路設(shè)計是否合理

評論