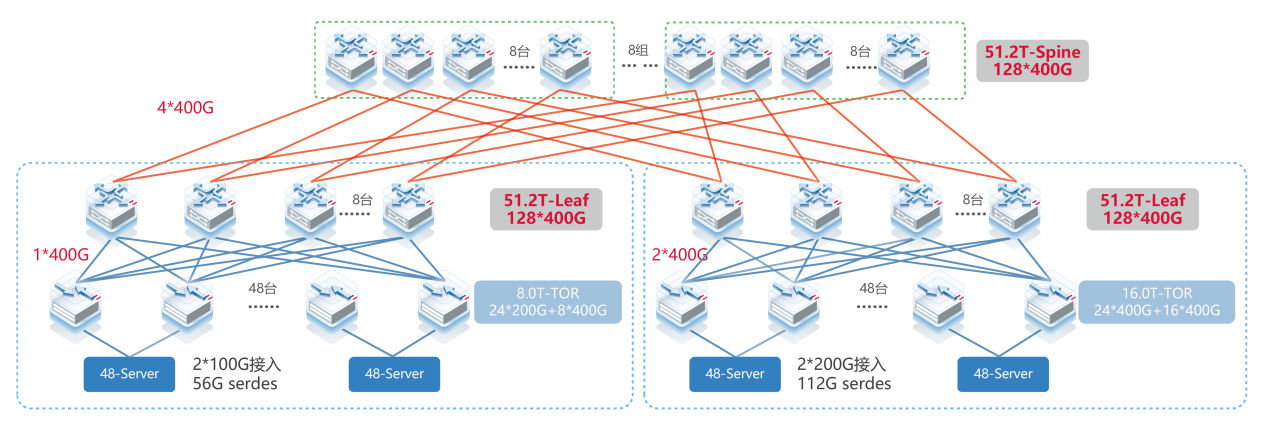

各種終端應用對更快數據速率的持續需求促使開發了最新一代的 SerDes 硬件,目前的速率已達到 112Gbps。例如,數據中心架構中的網絡交換機開始利用這些新的 112Gbps 實施(51.2Tbps 和 512 個通道)提供 51T 的吞吐量。

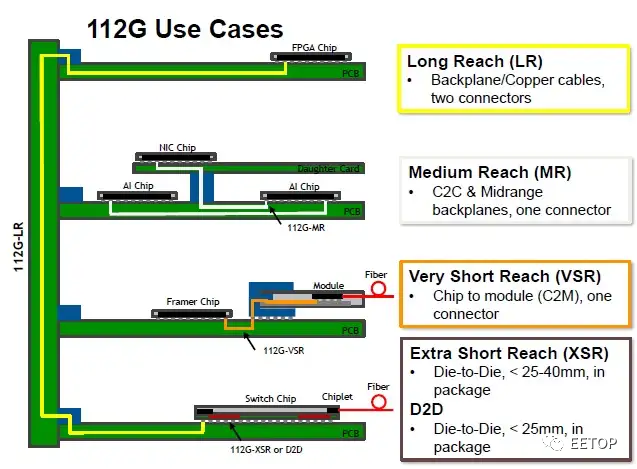

112Gbps SerDes設計將根據應用情況在各種配置中被采用。下圖展示了長距離(LR)、中距離(MR)、極短距離(VSR)和超短距離(XSR)拓撲,其中112G信令路徑在每個拓撲中都突出顯示。

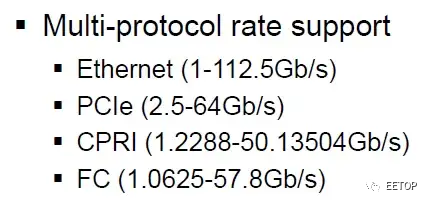

這些配置的插入損耗、每比特功率和誤碼率(BER)要求變化很大——SerDes設計滿足所有這些使用情況的約束是相當大的。 然而,高速 SerDes IP 的設計還有另一個考慮因素——即需要在與這些標準相關的數據速率范圍內支持多種通信協議。換句話說,網絡架構師需要靈活地對交換機進行編程,以支持協議內的傳統數據速率,并支持最新一代的系統。下圖提供了通用高速 SerDes 支持的多種協議和數據速率的示例:

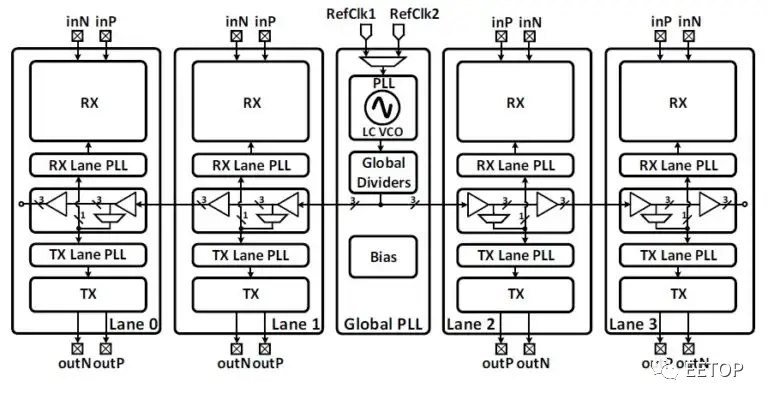

因此,協議的每個通道都必須具有獨立的速率可編程性和單獨的速度設置。 在最近的 VLSI 技術和電路研討會上,來自 Cadence Design Systems 高速 SerDes 設計團隊的 Aida Varzaghani 對 Cadence 的 112Gbps 設計進行了詳盡的描述,該設計最近采用 5nm 技術節點制造。本文將僅重點介紹 Aida 演示的一部分,以說明集成到SerDes IP的獨特時鐘設計,以獲得最廣泛的適用性。Cadence的 112G SerDes 的一般架構如下圖所示:

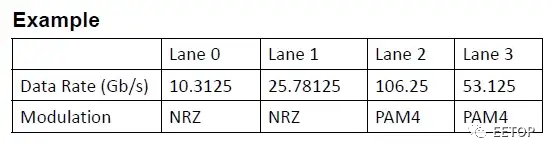

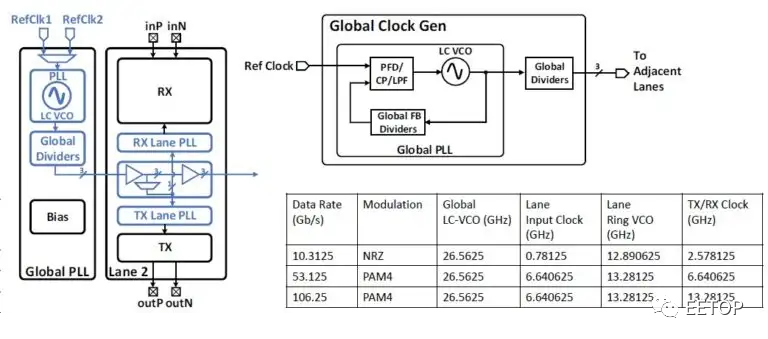

基本的宏設計是一組四通道的嵌入式全局時鐘生成生單元。(可以將其他通道添加到宏中。)下圖提供了一個獨特的協議數據速率(和信號調制)示例,可以為共享全局時鐘分布的各個通道進行編程。

如下圖所示,全局 PLL 將三個(單端)時鐘分配給相鄰的 Tx/Rx 通道。圖中的表格說明了全局 PLL 內部壓控振蕩器 (VCO) 頻率的示例,以及輸出到通道的“全局分頻器”的時鐘。還顯示了通道 PLL 的 VCO 頻率和最終通道時鐘頻率。

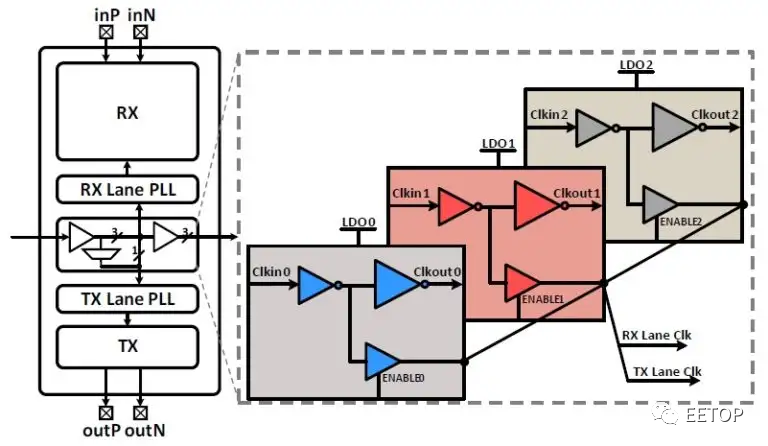

請注意,每個通道中都集成了一個 Tx PLL 和一個 Rx PLL。Tx 通道 PLL 合成目標頻率(以 1/4 的數據速率,如稍后所述)。專用 Rx PLL 用于從輸入的 SerDes 數據中恢復/跟蹤時鐘。通道 Tx/Rx PLL 的時鐘輸入電路如下圖所示:

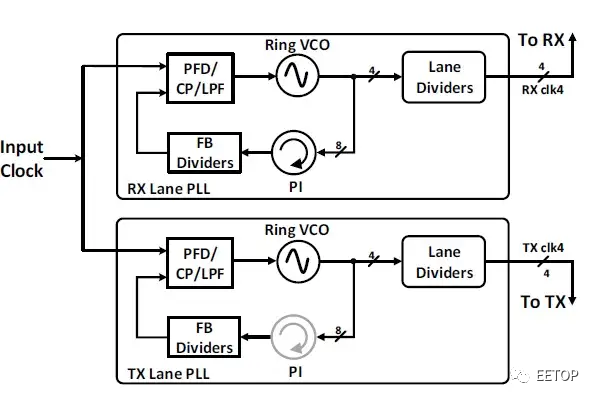

來自全局 PLL 分頻器通道的三個輸入時鐘通過三個驅動器多路復用到通道 PLL,并具有可編程的三態使能。(一個緩沖器將時鐘發送到下一個通道。)每個驅動器都由一個獨特的LDO供電。這種配置降低了通道 PLL 時鐘輸入中電源噪聲引起的抖動。Tx 和 Rx PLL 是相同的,如下所示:

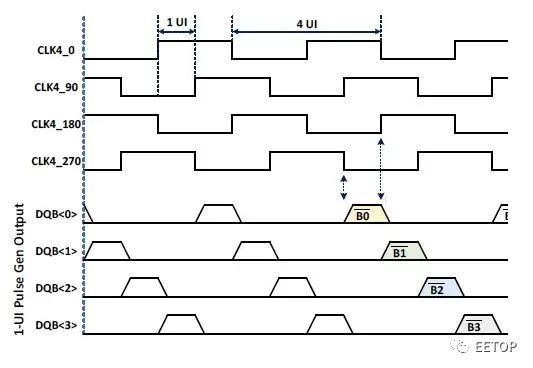

每個 PLL 中的 Ring VCO 提供四個與基頻相移(正交)的時鐘,它定義了數據速率傳輸的單位間隔,如下圖所示:

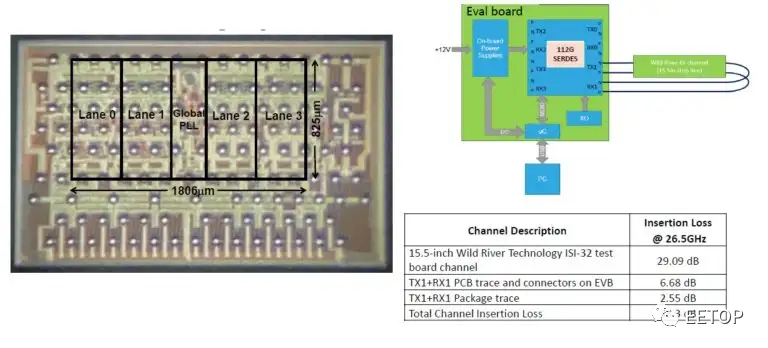

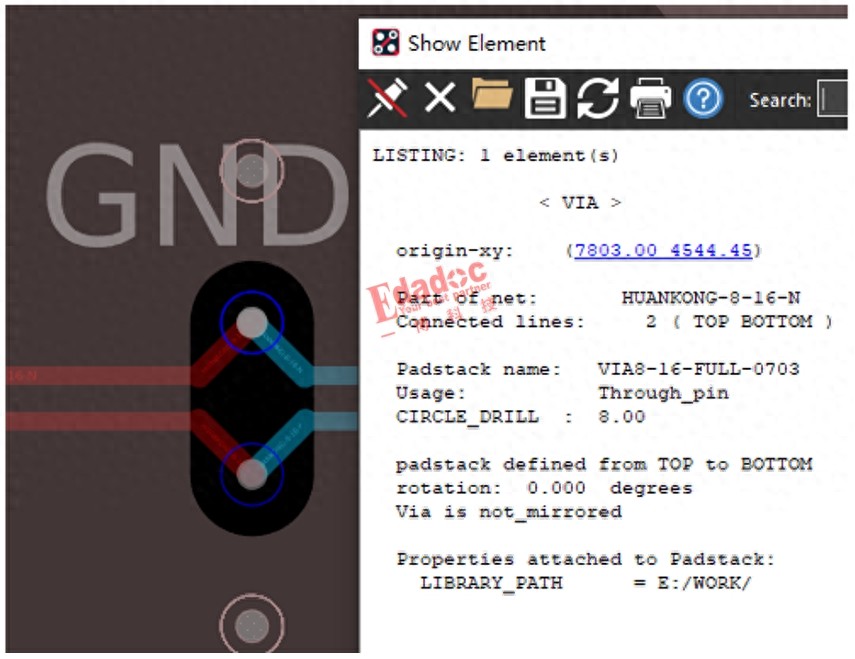

低數據速率是通過數字位填充實現的。Aida 還詳細介紹了連續校正占空比和最小化(正交)時鐘的到達偏差以減少輸出抖動的方法。 Rx 時鐘數據恢復功能由相位內插器支持,該內插器將 Rx 時鐘相位調整到反饋分頻器和輸入相位頻率檢測器。內插器中的各個相位邊沿是從振蕩器內的相移信號中提取的,如上所示。5nm 工藝節點中的 IP 測試裸片和用于表征電路的環回測試配置如下所示:

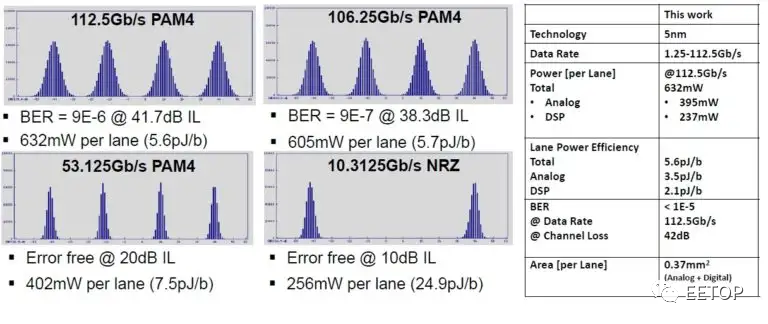

下圖顯示了環回測試的 Rx 特性——特別是不同數據速率下的每比特功率和 BER。

總結最新一代高速 SerDes IP 的設計需要提供最大的靈活性,能夠支持不同的協議標準和廣泛的數據速率。每通道可編程性是網絡架構師的一個重要特性。 在最近的 VLSI 技術和電路研討會上,Cadence SerDes 團隊最近著重介紹了他們的 112G IP 宏方法,特別是獨特的全局和 Tx/Rx 通道時鐘架構,以支持這些不同的協議和數據速率要求。

審核編輯 :李倩

-

數據中心

+關注

關注

16文章

5130瀏覽量

73184 -

SerDes

+關注

關注

7文章

209瀏覽量

35582

原文標題:5nm 112Gbps 最新一代 SerDes IP 時鐘設計詳解

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

蔚來5nm智駕芯片流片,車企智駕之戰一觸即發

性能殺手锏!臺積電3nm工藝迭代,新一代手機芯片交戰

Cadence推出HBM4 12.8Gbps IP內存系統解決方案

【高云GW5AT-LV60 開發套件試用體驗】一、硬件篇

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

聊聊高速PCB設計100Gbps信號的仿真

消息稱臺積電3nm、5nm和CoWoS工藝漲價,即日起效!

Alpahwave Semi推出全球首個64Gbps UCIe D2D互聯IP子系統

臺積電產能爆棚:3nm與5nm工藝供不應求

AI芯片驅動臺積電Q3財報亮眼!3nm和5nm營收飆漲,毛利率高達57.8%

臺積電3nm/5nm工藝前三季度營收破萬億新臺幣

三星將為DeepX量產5nm AI芯片DX-M1

51.2T交換機網絡解決方案

5nm 112Gbps最新一代SerDes IP時鐘設計詳解

5nm 112Gbps最新一代SerDes IP時鐘設計詳解

評論