這種類型的損壞最容易發生在組裝過程中或在芯片組裝到它們最終的 PCB 放置位置之前。

是的,理論是偉大的,但沒有什么比現實更能把你從云端帶出來了。對于今天的電子產品,我們應該通過在我們的集成電路中設計穩健的 ESD 結構來覆蓋所有 ESD 基礎。我們認為一切都很好,我們的電路是安全的,直到我們開始工作而不考慮 ESD 保護。

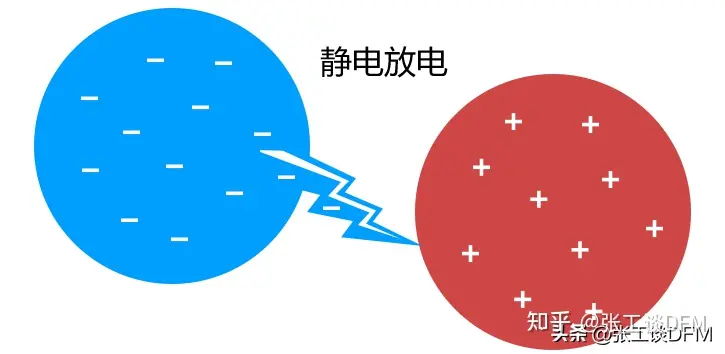

靜電放電或 ESD 的定義是在不同靜電勢的物體或表面之間的靜電荷轉移。此事件在短時間內發生在高電壓下,在千伏 (kV) 范圍內,從 1 到 100 納秒 (ns)。您可以想象,使用這些類型的電壓和時間單位,ESD 事件具有快速邊緣。當此類事件發生時,存儲的靜電荷會轉移,并且會出現可見或不可見的火花。

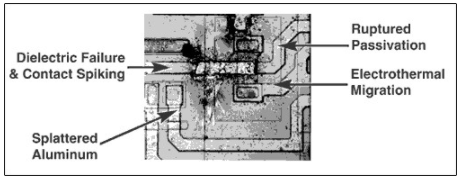

您可以穿著皮鞋穿過地毯并觸摸您的同伴的鼻子,從而體驗您自己的個人 ESD 事件。這是一次令人震驚的經歷,至少對我們中的一個人來說,但不是致命的。明顯的火花很容易被人類識別;但正是這些看不見的火花是如此之小,只有我們帶有敏感接口的電子設備才能檢測到。個人很可能通過觸摸沒有 ESD 保護的設備而在不知不覺中造成破壞性 ESD 電路損壞。我從個人經歷中知道這一點。在高電荷 ESD 環境中,其封裝內的 ESD 保護硅芯片將被破壞(圖 1)。

圖 1. 硅 ESD 損壞的放大示例顯示金屬跡線消失、鈍化破裂和一種熱遷移。

在圖 1 中,硅已經暴露在 ESD 事件中。造成的損壞是災難性的,包括金屬痕跡蒸發、鈍化區域受損以及可能的電熱遷移軟錯誤。從技術上講,如果電路仍在運行,則以后可能會出現軟錯誤(也稱為規格降級)。

這種類型的損壞最容易發生在組裝過程中或在芯片組裝到它們最終的 PCB 放置位置之前。IC 的內部 ESD 保護電路在預組裝處理和組裝操作期間為硅片提供一些保護。在這種環境中,低阻抗接地路徑用作放電路徑。在組裝或 IC 測試環境中,低阻抗接地路徑的實現包括腕帶、接地地板、接地桌面和 ESD 離子發生器。一旦 IC 安裝在 PCB 中并與其他組件互連,這種受保護的環境就會顯著降低易失性 ESD 路徑的可能性。通過適當的 ESD 控制和預防,內部 ESD 電路很有可能永遠不會被使用。

人們在與周圍環境互動時經常會產生 ESD 火花。這些有害火花可以通過完全降解或破壞硅來改變半導體器件的特性。ESD 事件是一個嚴重的工業問題,每年造成數十億美元的損失。在您選擇最終產品之前,在您的實驗室中遵循良好的 ESD 預防實踐并檢查您的產品數據表以了解 ESD 保護規范是值得的。幾周后加入我,我將為您提供硅 ESD 測試策略。

審核編輯:郭婷

-

ESD

+關注

關注

50文章

2294瀏覽量

175800 -

pcb

+關注

關注

4368文章

23492瀏覽量

409727

發布評論請先 登錄

保護您的電路免受靜電放電損壞

保護您的電路免受靜電放電損壞

評論