在我們開始詳細討論FEV 技術(shù)之前,我們需要有一個定義

到底什么才是我們所說的“等價”。

一般我們將等價定義為一組關(guān)鍵點之間的匹配,也就是說比較兩個模型在相同的激勵下,這些關(guān)鍵點是否完全具有相同的邏輯。關(guān)鍵點可能包括:

-

輸入

-

輸出

-

時序單元輸出(鎖存器和觸發(fā)器)

熟悉數(shù)字芯片實現(xiàn)的人可能發(fā)現(xiàn),這不就是一個寄存器傳輸級電路的幾個屬性么。

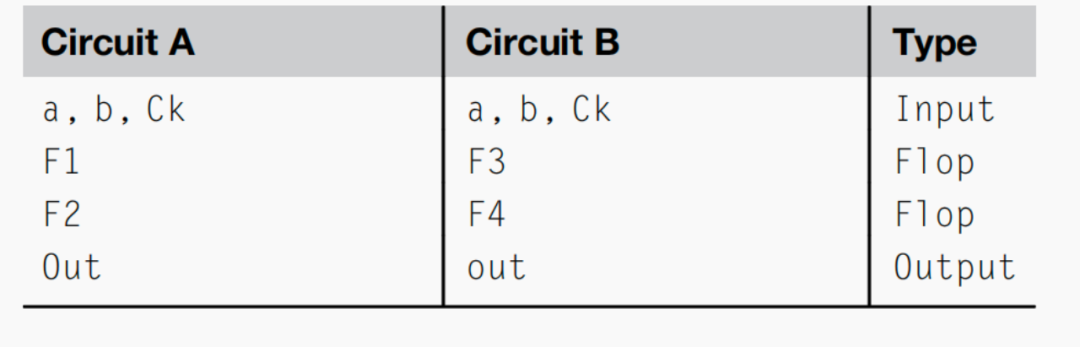

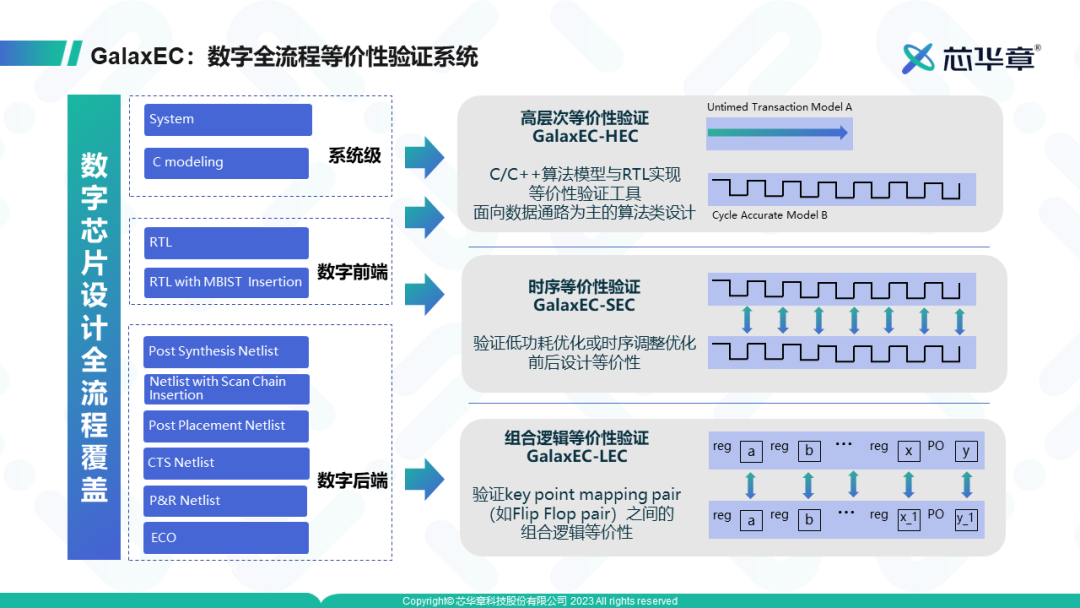

基于對于這些關(guān)鍵點的不同比對方式,有三種類型的等價性比對:

-

combinational equivalence

-

sequential equivalence

-

transactional equivalence

從上到下,比對的方式越來越寬松,但是整個模塊的端到端功能都能囊括在內(nèi)的。

具體的差異性,見后續(xù)的幾篇文章。

Combinational equivalence

Combinational equivalence是使用EDA工具進行等價性比對中最成熟的FEV技術(shù),一般情況下是將RTL和原理圖網(wǎng)表進行等價性比對

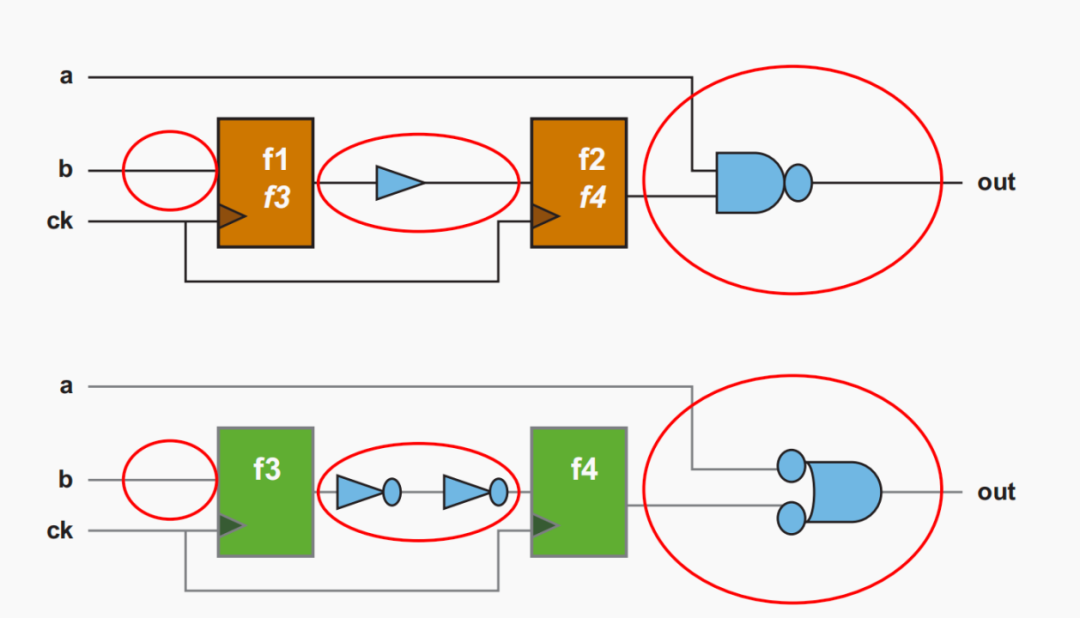

上圖中每個SPEC模型中的觸發(fā)器都對應于IMP模型中的特定觸發(fā)器并且兩兩觸發(fā)器之間的組合邏輯功能都是完全等價的。換句話說,這兩個模型之前的所有關(guān)鍵點都存在一一對應的關(guān)系,中間不存在任何其他的操作。

上一篇文章已經(jīng)說過,這種類型的等價性比對幾乎和邏輯綜合同時出現(xiàn),用來保證RTL和綜合后的門級網(wǎng)表一一對應。

-

這種方式的好處是:EDA工具不需要考慮寄存器之間的時序關(guān)系,只需要關(guān)心組合邏輯錐是否等價,

-

也有它的局限性:只適合于RTL和門級網(wǎng)表之間的寄存器數(shù)量一一對應的場景。熟悉邏輯綜合技術(shù)的人想必都知道,很多邏輯綜合技術(shù)會改變寄存器的位置和數(shù)量。

上面電路圖中,如果使用的是Combinational equivalence等價性驗證,那么需要比對的關(guān)鍵點就是輸入(a,b,Ck)、寄存器(F1、F2)和輸出(Out)

很明顯Combinational equivalence比對最嚴格,但是在很多場景下有限制(不適應于時序單元變化的場景)。

實際上,我們其實只要證明在相同的輸入下,輸出能夠比對上就可以了,不需要太關(guān)心中間的時序邏輯單元個數(shù),所以后面我們將介紹放寬這種約束的等價性比對sequential equivalence和transactional equivalence。

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123290 -

eda

+關(guān)注

關(guān)注

71文章

2881瀏覽量

176414 -

鎖存器

+關(guān)注

關(guān)注

8文章

922瀏覽量

42100 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2032瀏覽量

61860

原文標題:等價性比對驗證之combinational equivalence

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

介紹放寬約束的等價性比對sequential equivalence

Design of Combinational Circuit

關(guān)于功能驗證、時序驗證、形式驗證、時序建模的論文

分享一個FEC RTLvs Netlist等價性比對的示例

Combinational Design Examples

帶黑盒組合電路的等價性驗證

嵌入式操作系統(tǒng)實時性比對與分析

什么是軟件與硬件的邏輯等價性

深層解析形式驗證

形式驗證工具對系統(tǒng)功能的設(shè)計

RTL與網(wǎng)表的一致性檢查

Formal Verification:形式驗證的分類、發(fā)展、適用場景

打通系統(tǒng)到后端,芯華章發(fā)布首款自研數(shù)字全流程等價性驗證工具

一文解析最嚴格的等價性比對驗證combinational equivalence

一文解析最嚴格的等價性比對驗證combinational equivalence

評論