形式驗證工具(Formal Verification Tool)是通過數學邏輯的算法來判斷硬件設計的功能是否正確,通常有等價性檢查(Equivalence Checking)和屬性檢查(Property Checking)兩種方法。

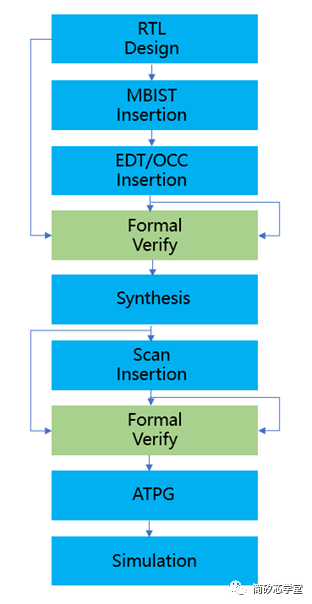

等價性檢查用來檢查兩個數字集成電路設計之間的邏輯等價性。在集成電路設計過程中許多步驟都可能做邏輯修改,例如插入可測性設計邏輯、時鐘樹綜、工程變更單等,如果用仿真驗證會耗費大量時間而且難以保證驗證的覆蓋率。等價性檢查時通過靜態和數學邏輯的算法來比較修改前后邏輯的一致性,理論上可實現全覆蓋驗證。

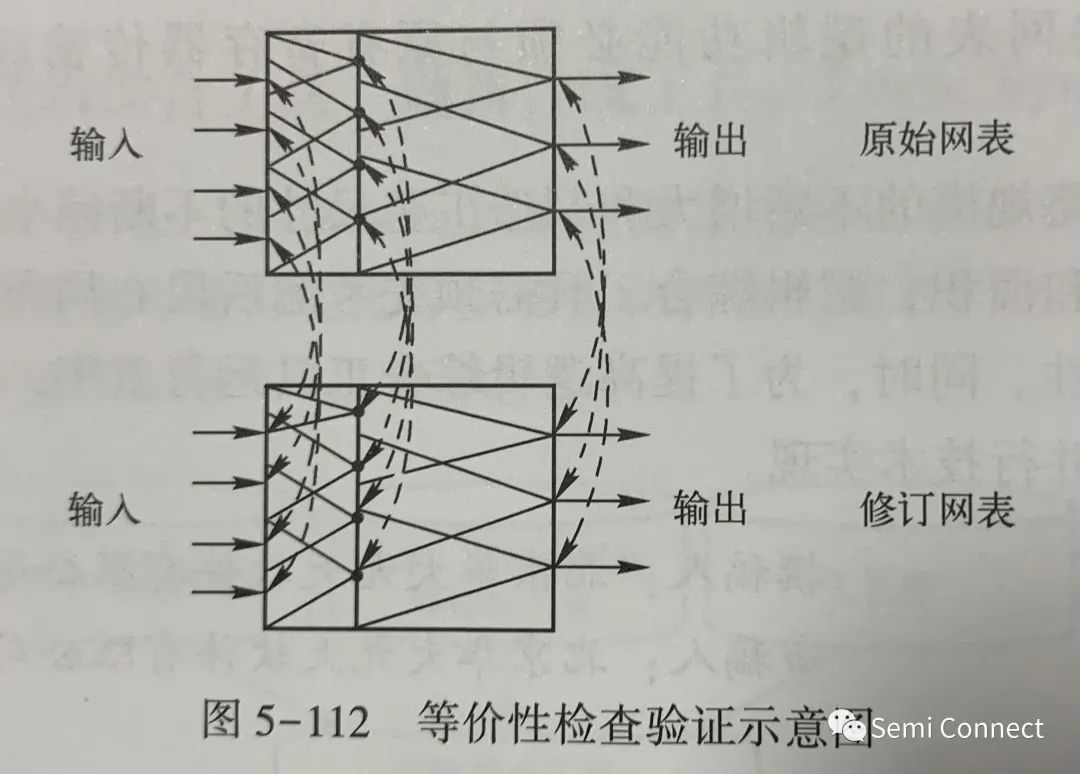

對于給定的兩個網表(可以稱為原始網表和修訂網表),假設兩個網表的輸入信號、輸出信號,以及網表中的輸入信號、輸出信號和網表中的寄存器配對,產生多對組合邏輯錐(Combinational Logic Cones);然后再用二元決策圖(Binary Decision Diagram)、合取范式的可滿足性求解器(SAT So lver)等算法,對每一對組合邏輯錐進行比較。如果每一對里兩個邏輯錐的布爾函數都是等價的,就能斷定兩個網表的靜態和時序邏輯功能是相同的。等價性檢查驗證示意圖如圖5-112所示。

當原始網表和修訂網表的寄存器個數不相同時 ,上述的算法通常會發現有些配對的組合邏輯錐里的兩個布爾函數是不等價的。這時就必須用一些檢測時序邏輯等效性(Sequential Equivalence Checking)的算法做進一步分析,從而判定兩個網表的邏輯功能是否相同。

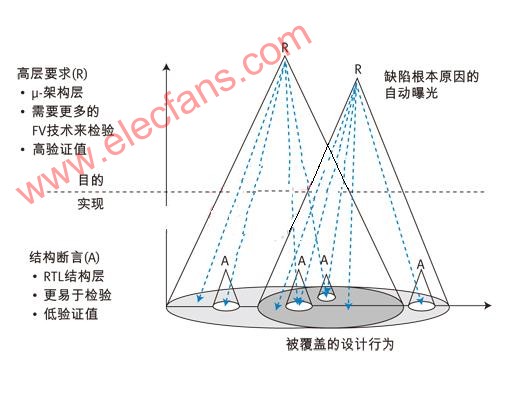

屬性檢查時一種分析電路設計是否滿足某些給定規范或斷言(Assertion)的方法。首先用邏輯結構和形式化邏輯描述系統模型和待驗證的屬性,如時序邏輯結構、有限狀態機和形式邏輯公式等,再通過形式驗證的算法來檢測設計是否滿足該屬性。屬性檢查技術又可以分為定理證明(Theorem Proving)和模型檢查(Model Checking)。

定理證明是將設計和待驗證的屬性用某種形式化邏輯系統的公式表示出來,再根據該系統的公理、推理規則以及已經證明的定理,推導出表達系統屬性的公式,從而證明設計滿足該屬性。這種推導的過程通常需要人工參與,并要對系統功能設計有相當程度的了解。

模型檢查是用時序邏輯結構或有限狀態機表示待檢驗的設計。首先用某種時態邏輯表示設計應該具有的屬性,再通過二元決策圖、合取范式可滿足性求解、自動測試生成(ATPG)等技術搜尋設計的狀態空間,檢測是否在所有可能的狀態下設計都滿足這些屬性。如果檢測出設計不滿足某種屬性時,也能給出反例,方便錯誤的定位。模型檢查算法通常不需要人工參與,但如果設計可能存在的狀態空間太大時,會遭遇所謂的狀態爆炸(State Explosin)問題,導致無法在有限的時間內得到最終的結果。

由于工藝的不斷演進,等價性檢查和屬性檢查的技術必須不斷地改進才能處理越來越大的設計規模。

-

硬件

+關注

關注

11文章

3459瀏覽量

67178 -

形式驗證

+關注

關注

0文章

8瀏覽量

5759 -

數學邏輯

+關注

關注

0文章

3瀏覽量

5242

原文標題:可編程邏輯電路設計—形式驗證工具

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

關于功能驗證、時序驗證、形式驗證、時序建模的論文

形式驗證技術商機凸顯 SoC整合問題亟需解決

上海控安iVerifier計算機聯鎖系統驗證工具概述

關于形式驗證的11個誤區

Formal Verification:形式驗證的分類、發展、適用場景

從小眾走向普及,形式化驗證對系統級芯片開發有多重要?

形式驗證工具對系統功能的設計

形式驗證工具對系統功能的設計

評論