移動數(shù)據(jù)的迅速攀升,蓬勃發(fā)展的人工智能及機(jī)器學(xué)習(xí)(AI / ML)應(yīng)用,和 5G 通信對帶寬前所未有的需求對現(xiàn)有云數(shù)據(jù)中心的服務(wù)器、存儲和網(wǎng)絡(luò)架構(gòu)形成了巨大壓力。這些頗具挑戰(zhàn)性的應(yīng)用需要高 I / O 帶寬和低延遲通信的支持。

由于超大規(guī)模數(shù)據(jù)中心需要 12.8Tbps 甚至更高的網(wǎng)絡(luò)交換帶寬,ASICs 和 SoC 對 112G SerDes IP 的需求也應(yīng)運(yùn)而生。Cadence 的 112G SerDes 技術(shù)具有卓越的長距性能、優(yōu)秀的設(shè)計裕度、優(yōu)化的功耗和面積,是下一代云網(wǎng)絡(luò)、AI / ML 和 5G 無線應(yīng)用的理想選擇。

SerDes PHY IP 支持 PAM4 和 NRZ 信號調(diào)制,以及從 1G 到 112G 的數(shù)據(jù)傳輸速率,采用業(yè)界領(lǐng)先的模擬-數(shù)字轉(zhuǎn)換器(ADC),時鐘數(shù)據(jù)恢復(fù)(CDR)和數(shù)字信號處理(DSP)技術(shù),可支持 40dB 以上的通道。該技術(shù)可實現(xiàn)背板、直連電纜(DAC)、芯片到芯片、以及芯片到模組間的高速數(shù)據(jù)傳輸,實現(xiàn)高性能計算(HPC)SoC。采用了 7nm 制程工藝的 Cadence 112Gbps 多速率 PAM4 SerDes IP 助力達(dá)成業(yè)界領(lǐng)先的功耗、性能和面積(PPA)目標(biāo),面向下一代云端架構(gòu)和電信數(shù)據(jù)中心打造高端口密度的網(wǎng)絡(luò)產(chǎn)品。

高速 SerDes 的市場趨勢

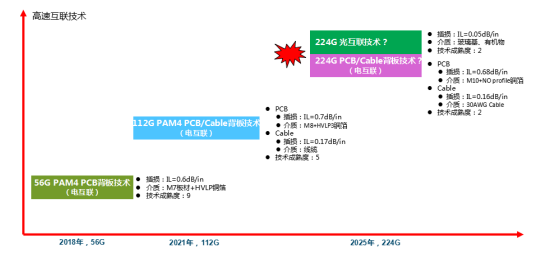

56G / 112G SerDes IP 屬于高速 I / O,支持超大規(guī)模計算客戶所需的指數(shù)級流量增長,推動制定采用 8 條 112G 鏈路的 800G 標(biāo)準(zhǔn)。業(yè)界龍頭企業(yè)已發(fā)布了 25.6TB 交換機(jī)產(chǎn)品,下一代 51.2TB 產(chǎn)品也即將推出。這些高帶寬交換機(jī)會使用ASICs,并將 112G PAM4 SerDes 作為基礎(chǔ) IP。支持 51.2TB 交換機(jī)的吞吐量需要大量的 I / O,但將其整合至同一個 SoC 則是一大挑戰(zhàn),在封裝設(shè)計和功耗管理方面都需要作出突破。

在即將推出的協(xié)同封裝硅片(CPO)解決方案中,裸片和光學(xué)多晶粒被集成到同一個封裝中,以此避免在 PCB 板上的長距離布線,并擁有更高的吞吐量。得益于支持多插槽配置和芯片間互聯(lián)的高速 I / O 接口,高帶寬以及低延遲,112G SerDes 的另一個應(yīng)用場景是 AI / ML SoC。5G 應(yīng)用同樣需要高帶寬,112G SerDes 也是理想的選擇。

挑戰(zhàn)

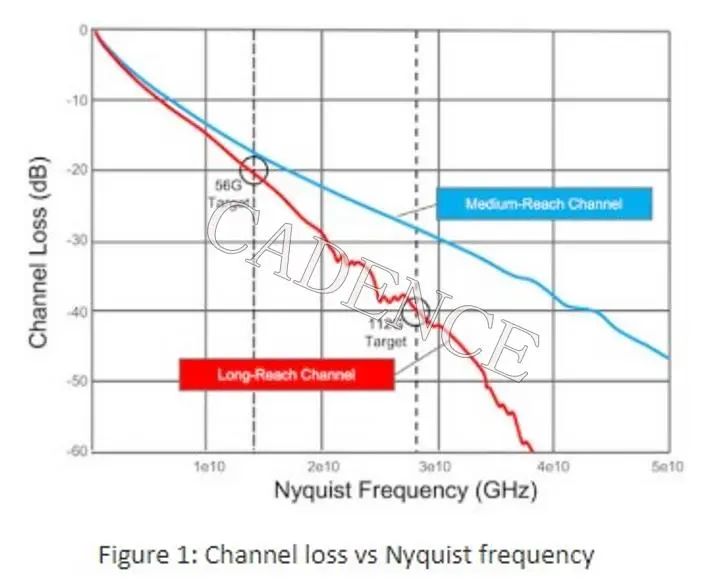

112G SerDes 技術(shù)可以滿足數(shù)據(jù)密集型應(yīng)用對高速互聯(lián)的需求。但是,長距離連接需要更先進(jìn)的服務(wù)器和網(wǎng)絡(luò)設(shè)備,其設(shè)計本身就是巨大的挑戰(zhàn)。由于奈奎斯特頻率的翻倍,112G 系統(tǒng)的通道損失遠(yuǎn)超過 56G 系統(tǒng),解決這一問題需要新的 SerDes 設(shè)計方法,如圖一所示。

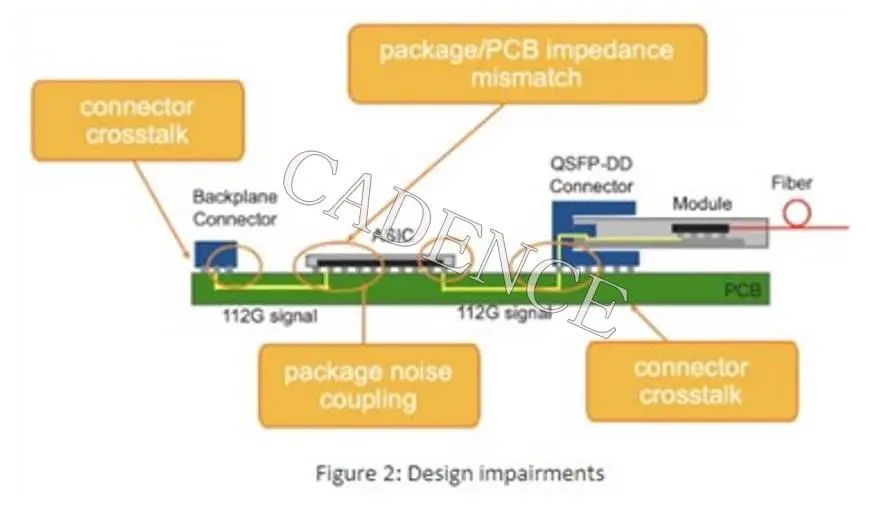

由于系統(tǒng)中的設(shè)計缺陷,112G 的部署也面臨挑戰(zhàn),如圖二所示。SoC 封裝,封裝到母板阻抗失配,前面板和背板的串?dāng)_以及噪聲耦合等設(shè)計問題均會對誤碼率(BER)產(chǎn)生顯著影響。由于更小的 UI 和更低的 SNR,我們在采用 112G 數(shù)據(jù)速率的過程中還會遇到更大的挑戰(zhàn)。

因此,在設(shè)計階段就確保總體通道性能滿足 IEEE 標(biāo)準(zhǔn)至關(guān)重要。通道性能不應(yīng)僅依據(jù)插入損耗判斷。IEEE 標(biāo)準(zhǔn)指出,應(yīng)將通道運(yùn)行裕度(COM)作為測量標(biāo)準(zhǔn)。通過預(yù)先規(guī)定 COM 的最小值,這一標(biāo)準(zhǔn)允許設(shè)計師在滿足 BER 規(guī)范的前提下自行選擇優(yōu)化信號缺陷和均衡方案。在包括 RX / TX 規(guī)范、串?dāng)_、抖動、碼間干擾(ISI)和噪聲等多維設(shè)計空間中,優(yōu)秀的設(shè)計應(yīng)該考慮 COM 的最大值。COM 的目的是用最少的指定 SerDes 對系統(tǒng)中的通道進(jìn)行表征化,但是 COM 也可以檢查高速串行系統(tǒng)的互操作裕度。根據(jù) IEEE 802.3ck 規(guī)范對 112G 的規(guī)定,COM 裕度不得小于 3dB。

Cadence 112G SerDes PHY IP

為了補(bǔ)償上述提及的無法避免的設(shè)計缺陷和挑戰(zhàn),IP 供應(yīng)商為其 IP 設(shè)計了更高的裕度。Cadence 112G Extended Long-Reach(ELR)PHY IP 提供額外的性能裕度,通過反射消除和增強(qiáng)的 DSP 來應(yīng)對設(shè)計缺陷。這些增強(qiáng)讓我們?yōu)楦邠p耗和高反射的通道提供更高的裕度。這些對生產(chǎn)系統(tǒng)行之有效的特性包括:

基于第四代設(shè)計和優(yōu)化的成熟解決方案

在 Cadence 測試芯片和客戶產(chǎn)品上經(jīng)過驗證的架構(gòu)

超越 IEEE 規(guī)范的性能

可編程的反射消除邏輯可有效減少設(shè)計缺陷,并降低產(chǎn)品生產(chǎn)風(fēng)險,加速上市進(jìn)度

基于固件的調(diào)整,智能功耗優(yōu)化和片上溫度傳感器等內(nèi)置智能工具

關(guān)于 Cadence

Cadence 在計算軟件領(lǐng)域擁有超過 30 年的專業(yè)經(jīng)驗,是電子系統(tǒng)設(shè)計產(chǎn)業(yè)的關(guān)鍵領(lǐng)導(dǎo)者。基于公司的智能系統(tǒng)設(shè)計戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產(chǎn)品,助力電子設(shè)計從概念成為現(xiàn)實。Cadence 的客戶遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計算、5G 通訊、汽車、移動設(shè)備、航空、消費(fèi)電子、工業(yè)和醫(yī)療等最具活力的應(yīng)用市場交付從芯片、電路板到完整系統(tǒng)的卓越電子產(chǎn)品。Cadence 已連續(xù)八年名列美國財富雜志評選的 100 家最適合工作的公司。如需了解更多信息,請訪問公司網(wǎng)站 cadence.com。

2022 Cadence Design Systems, Inc. 版權(quán)所有。在全球范圍保留所有權(quán)利。Cadence、Cadence 徽標(biāo)和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標(biāo)志均為 Cadence Design Systems, Inc. 的商標(biāo)或注冊商標(biāo)。所有其他標(biāo)識均為其各自所有者的資產(chǎn)。

-

Cadence

+關(guān)注

關(guān)注

66文章

963瀏覽量

143800 -

服務(wù)器

+關(guān)注

關(guān)注

12文章

9681瀏覽量

87260 -

SerDes

+關(guān)注

關(guān)注

7文章

209瀏覽量

35582

原文標(biāo)題:高速 112G 設(shè)計和通道運(yùn)行裕度

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

無鉛低溫錫膏激光焊接的研發(fā)現(xiàn)狀和市場趨勢

車載SerDes技術(shù)與靜電防護(hù)方案解析

信號集成滑環(huán)的技術(shù)特點與市場趨勢分析

高速線纜在數(shù)據(jù)中心的應(yīng)用和解決方案

鑄就AI服務(wù)器質(zhì)量動脈 – 高速背板連接器新趨勢(一)

224G 高速互聯(lián)對 PCB 及覆銅板需求及激光錫球植球機(jī)的助力(下)

224G 高速互聯(lián)對 PCB 及覆銅板需求及激光錫球植球機(jī)的助力(上)

數(shù)據(jù)采集器的市場趨勢與前景

dp接口的市場趨勢分析

物聯(lián)網(wǎng)設(shè)備的市場趨勢

RFID手持終端市場趨勢

數(shù)字人的市場趨勢分析

MES軟件的市場趨勢分析

MCU前沿市場趨勢:8位單片機(jī)和32位單片機(jī)

電池分選機(jī)的市場趨勢與機(jī)遇

高速112G SerDes技術(shù)的市場趨勢與設(shè)計挑戰(zhàn)

高速112G SerDes技術(shù)的市場趨勢與設(shè)計挑戰(zhàn)

評論