本文為明德揚原創文章,轉載請注明出處!

由于AD9144是高速DA轉換模塊,轉換速率可以達到2.5G,可以滿足普通的DA數據接口。為了匹配高速AD/DA轉換,JESD204B接口就應運而生,在本高速DA轉換工程中,AD9144的參數設定與JESD204B有千絲萬屢的關系,二者是相互對應的。

本次工程實現的目標:

波形:正弦波(波形由16個16位寬數據構成)

頻率:31.25MHZ

采樣率:500MHZ

DAC個數:2個

LANE個數:4個

插值:1

類型:單link

單次傳輸數據為:128位

一、 AD9144工作模式的選擇

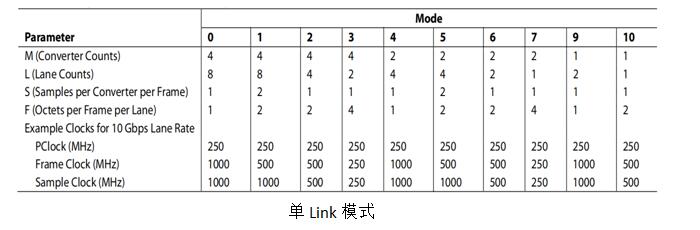

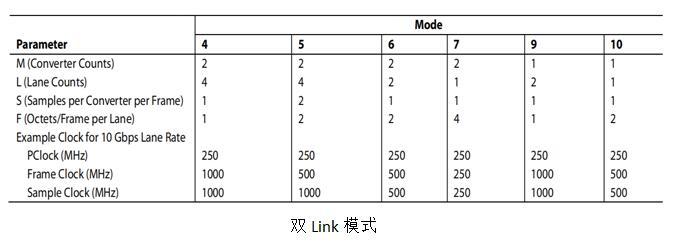

AD9144共有Single-Link和dual-Link兩種類型可以選擇,其中Single-Link類型有10種工作模式,Dual-Link有6種工作模式。

具體工作模式如下圖所示:

1. 參數介紹:

M:轉換DA個數;

L:lane的個數;

S:每一個AD的每一幀的采樣點數;

F:每條lane的每一幀的字節數;

2. 模式的選擇步驟

對于工作模式的選擇不同的項目有著不同的思考:

1) 本次采用單link方式所以有10種工作模式選擇;

2) AD9144使用兩個DAC所以只能在mode4-mode7之間選擇;

3) AD9144和JESD204B間采用4條lane相連,所以只能選擇mode4或mode5;

4) 為了便于AD9144參數計算,本次采用JESD204B的mode4。

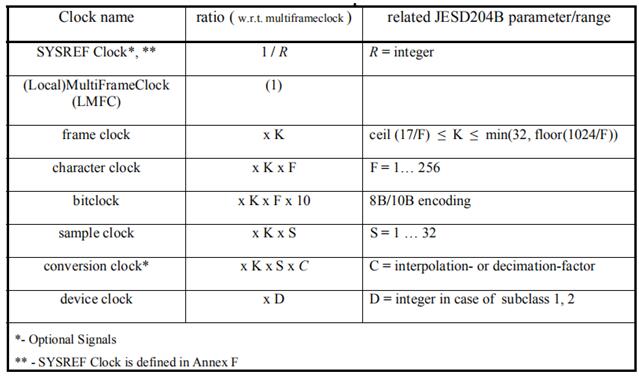

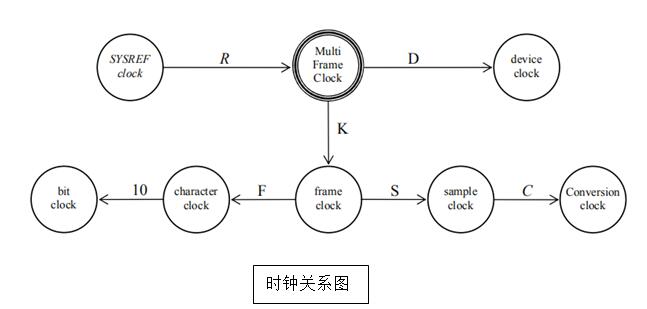

二、JESD204B的時鐘關系

了解AD9144時鐘關系是我們計算AD9144參數的前提,下面介紹一下JESD204B中各個時鐘之間的關系。

1.名詞解釋:

SYSREF clock:同步時鐘頻率

Device clock:驅動時鐘頻率

Multifram clock:多幀頻率

Fram clock:幀頻率

Bit clock:單條lane數據傳輸速率

Sample clock:采樣率

Conversation clock:轉換率

2.關系介紹

1個同步時鐘周期內,可以發R個多幀

1個多幀的發送需要D個工作時鐘;

1個多幀由K個幀組成

1個幀內由F個字節數

1個字節經過8B/10B編碼得到bit數

1幀內由S個采樣點

1個采樣點經過C倍插值得到轉化后的采樣結果(C由x1,x2,x4,x8四種模式)

三、 AD9144的參數設定

1.參數設定的意義

①確定配置AD9144所需要的寄存器值;

②設定JESD204B的IP核的參數;

③ 確定AD9516的分頻時鐘頻率;

2.AD9144的時鐘參數計算

由工程的設計目標,可以結合JESD204B對AD9144進行參數設置。

| = 1 * GB3 * MERGEFORMAT ① |

有效數據傳輸速率 =sample*16*2=16G/s;

實際傳輸數據速率 =16G*(10/8)=20G/s;

Lane_rate =20G/4=5G;

Sapmple_clock =500MHZ;

Frame_clock =sample_clock/S=500MHZ(S取1);

Char_clock =fram_clock*F=500MHZ(F取1);

Bit_clock =char_clock*10=5G(8b/10B編碼得出);

Conversion_clock =sample_clock*C=500MHZ(單倍插值C=1);

Mul_fram_clock =fram_clock/K=15.625MHZ(K取32);

| = 2 * GB3 * MERGEFORMAT ② |

Sysref_clock =mul_fram_clock/R=7.8125MHZ(R取合適的整數即可R=2);

device_clock =mul_frame_clock*D=125MHZ(D 取合適整數即可D=8);

Refclk=lane/40 =125MHZ(AD9144參考時鐘);

注釋:

= 1 * GB3 * MERGEFORMAT ①實際速率是有效速率經過8B/10B編碼得出;

= 2 * GB3 * MERGEFORMAT ②D最小值是,Dmin=有效數據量/128,D為整數;

四、 AD9144的配置表生成

1.實現方法

方法1;對照AD9144手順根據工程的實現功能以及AD9144的計算參數進行逐個配置

方法2:使用AD9144的配置軟件進行配置,然后對照手順進行配置

本次使用方法2進行AD9144的寄存器值的配置

2.實現步驟

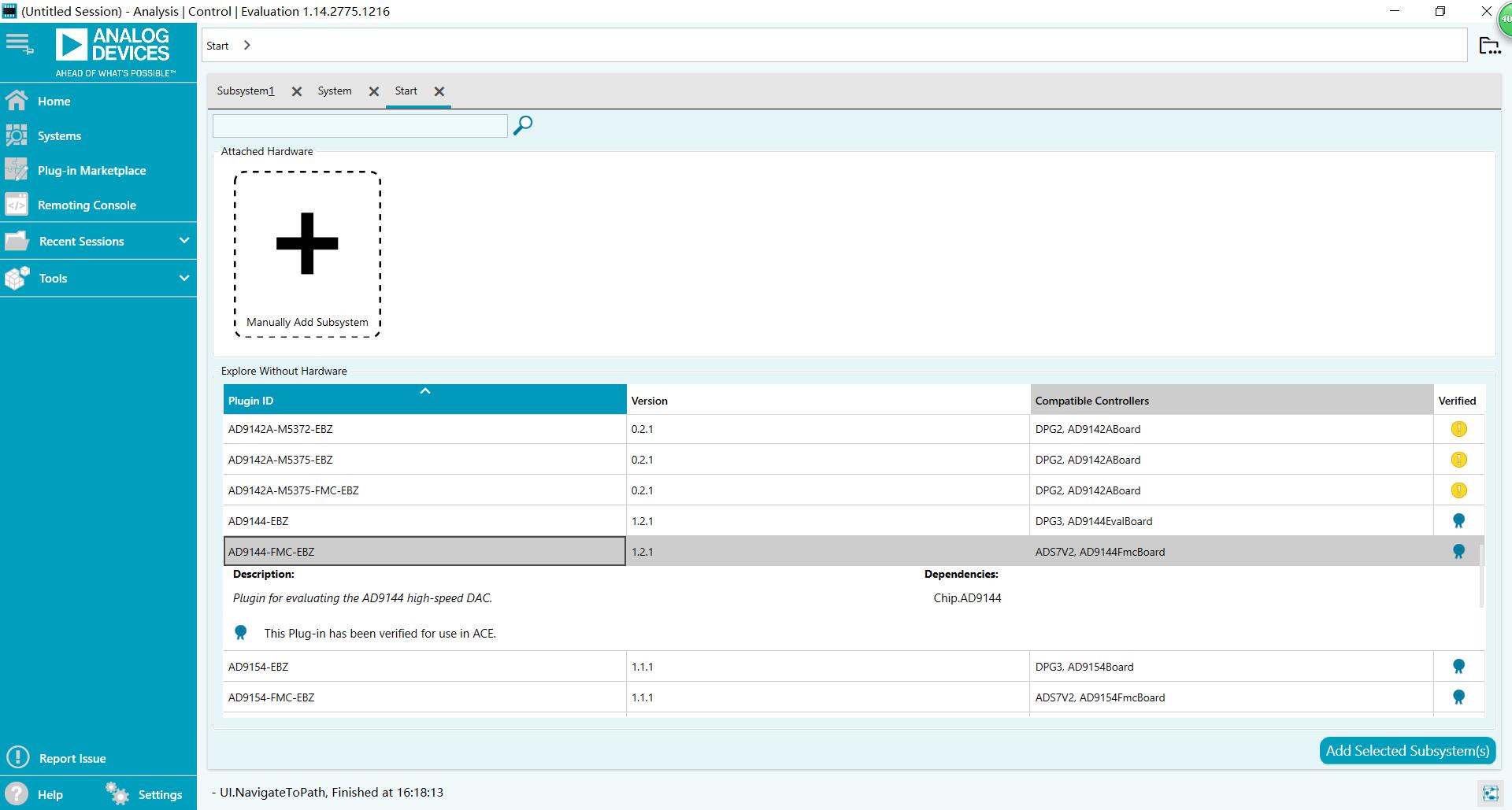

1. 打開ACE軟件選擇對應芯片AD9144-FMC-EBZ,并選擇添加。

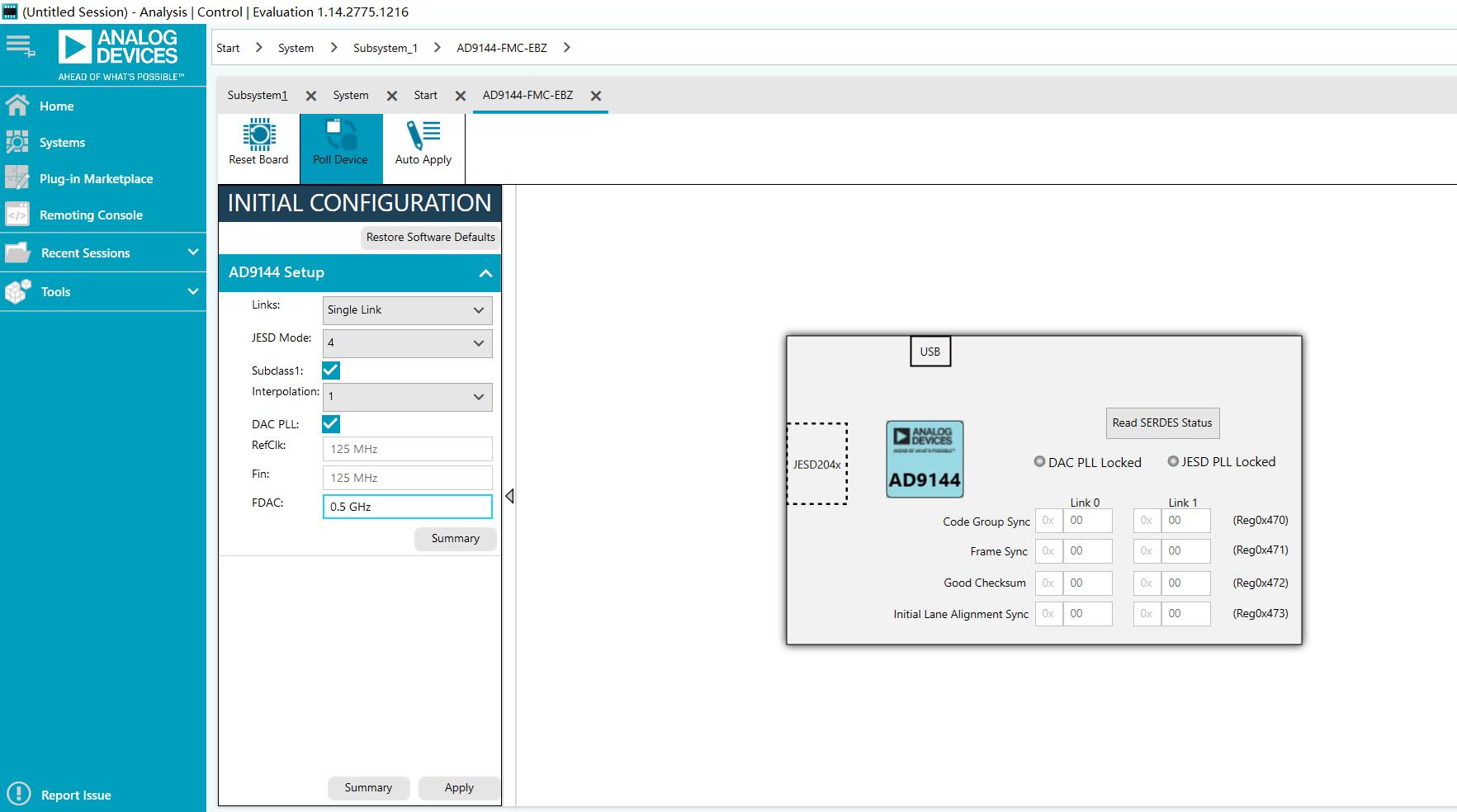

2. 對照計算的AD9144的參數進行芯片設置,完成后雙擊藍色AD9144圖標。

(1)Link模式:single; (2)link;JESD MODE :mode4;

(3)Subclss:子類1; (4)Interpolation:選擇1倍插值(無插值模式);

(5)DAC PLL勾選; (6)RefClk:計算的AD9144參考時鐘,125MHZ;

(7)FIN=device_clock=125MHZ; (8)FADC=采樣率=500MHZ;

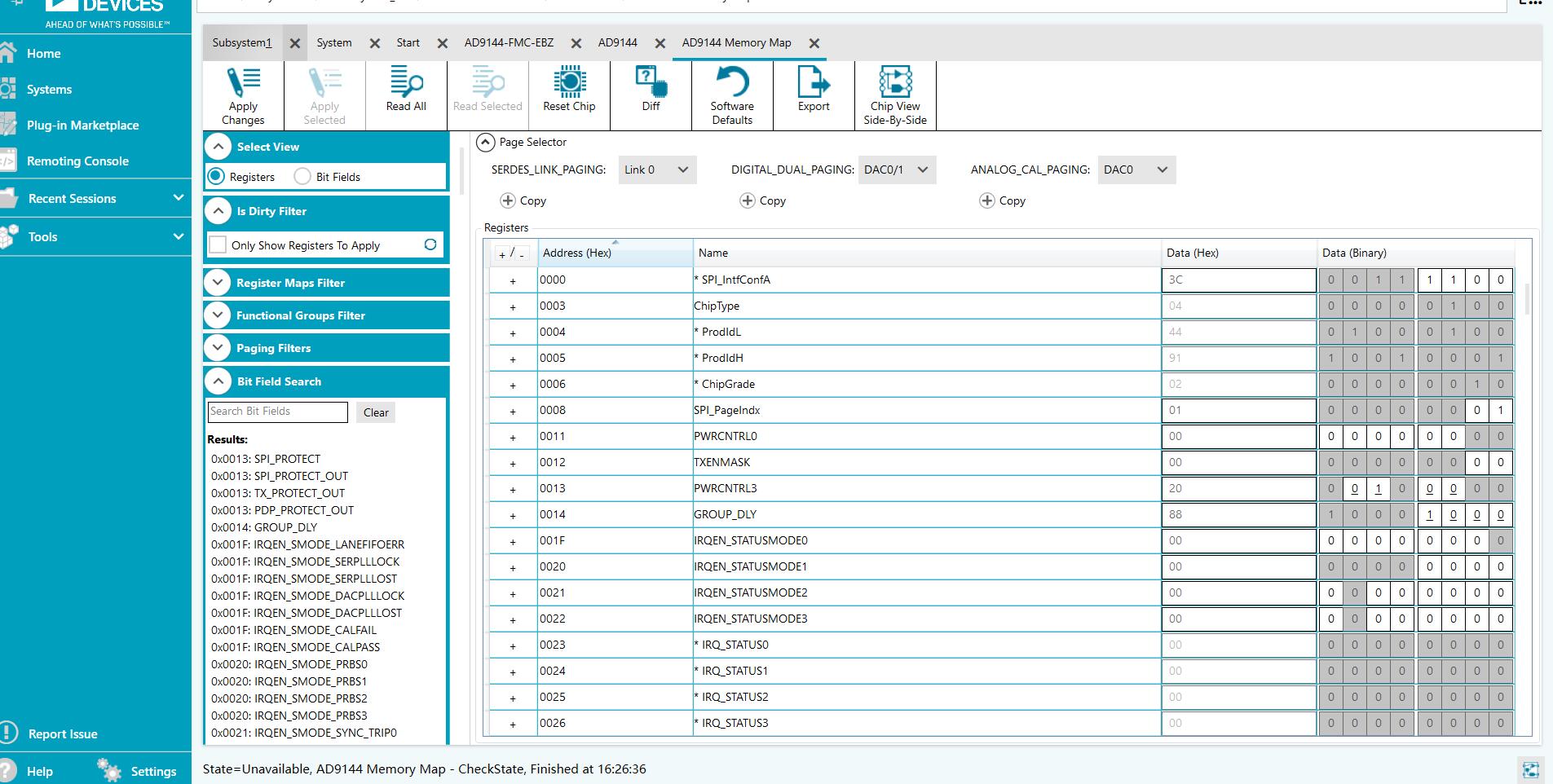

3. 寄存器配置表生成后,即可用來配置AD9144寄存器

以上就是AD9144的參數設定,感興趣的同學可以留言相互討論!

審核編輯 黃昊宇

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613988 -

JESD204B

+關注

關注

5文章

82瀏覽量

19502 -

ad9144

+關注

關注

0文章

8瀏覽量

1991 -

jesd204b時鐘

+關注

關注

0文章

2瀏覽量

919

發布評論請先 登錄

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

AD9680 JESD204B接口的不穩定會導致較大的電流波動,怎么解決?

使用jesd204b IP核時,無法完成綜合,找不到jesd204_0.v

JESD204B有專用于ADC/DAC和FPGA或ASIC的接口嗎?

調試ADS52J90板卡JESD204B接口遇到的問題求解

使用JESD204B接口,線速率怎么計算?

ADC16DX370 JESD204B串行鏈路的均衡優化

從JESD204B升級到JESD204C時的系統設計注意事項

使用JESD204B接口的AD9144高速DA轉換模塊參數設定(私人總結版)

使用JESD204B接口的AD9144高速DA轉換模塊參數設定(私人總結版)

評論