FPGA中實現對數運算主要有三種方法:

(1)在外部直接算好對數值,按照數值范圍做個表,存在ram里,到時候查表。為了減少表深度,提高資源利用率,可以考慮去掉部分低位數值,損失一定的精度。

(2)使用cordic算法求解對數。

(3)log10(x)=ln(x) * log10(e) , log10(e)是常數可以手動先計算好,用IP Core的話多個乘法器。

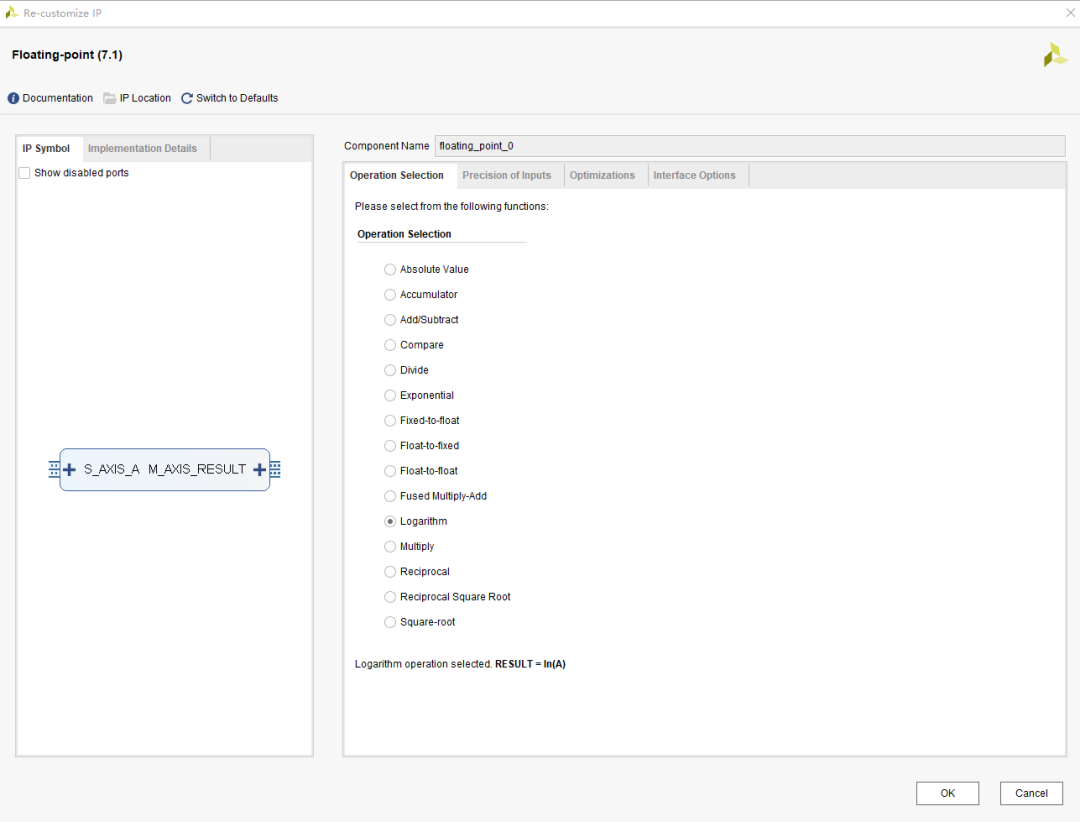

下面介紹使用IP核floating-point來計算對數,該IP計算對數時,計算的是Ln(A)(A是輸入),如下圖所示:

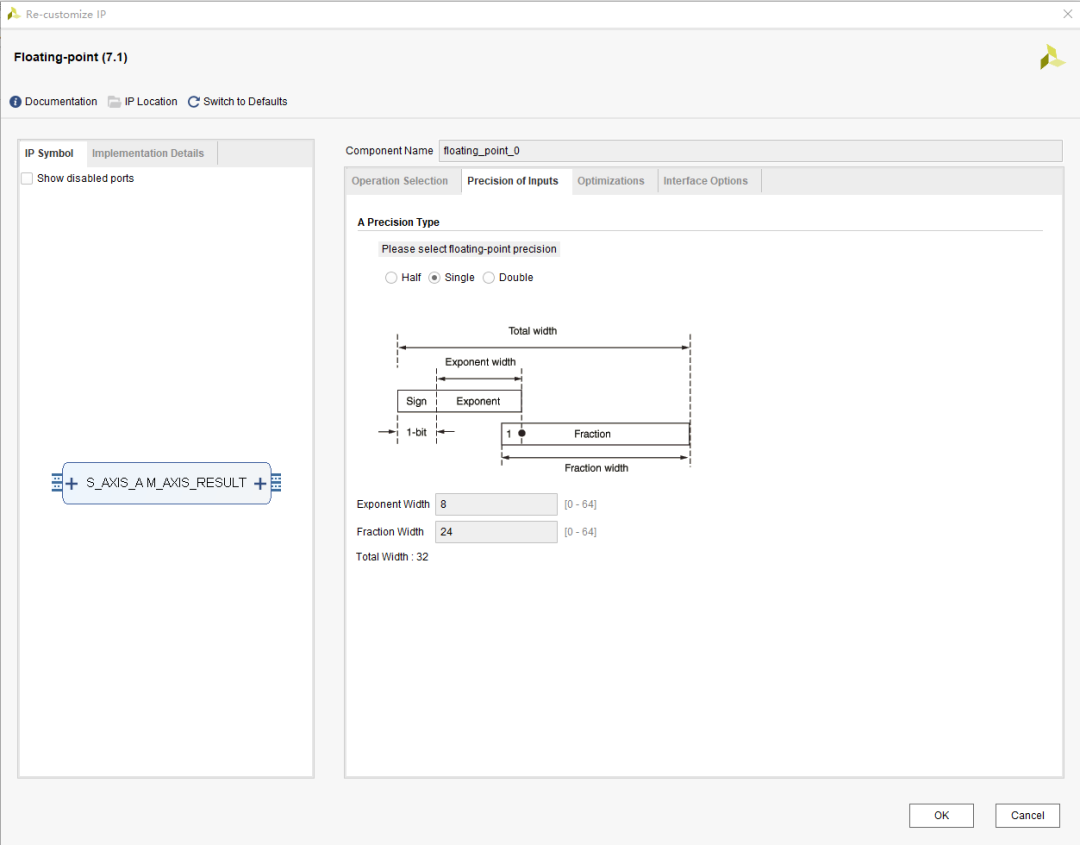

輸入是浮點數,所以如果我們在FPGA內使用的定點數,則需要先將定點數轉化為浮點數:

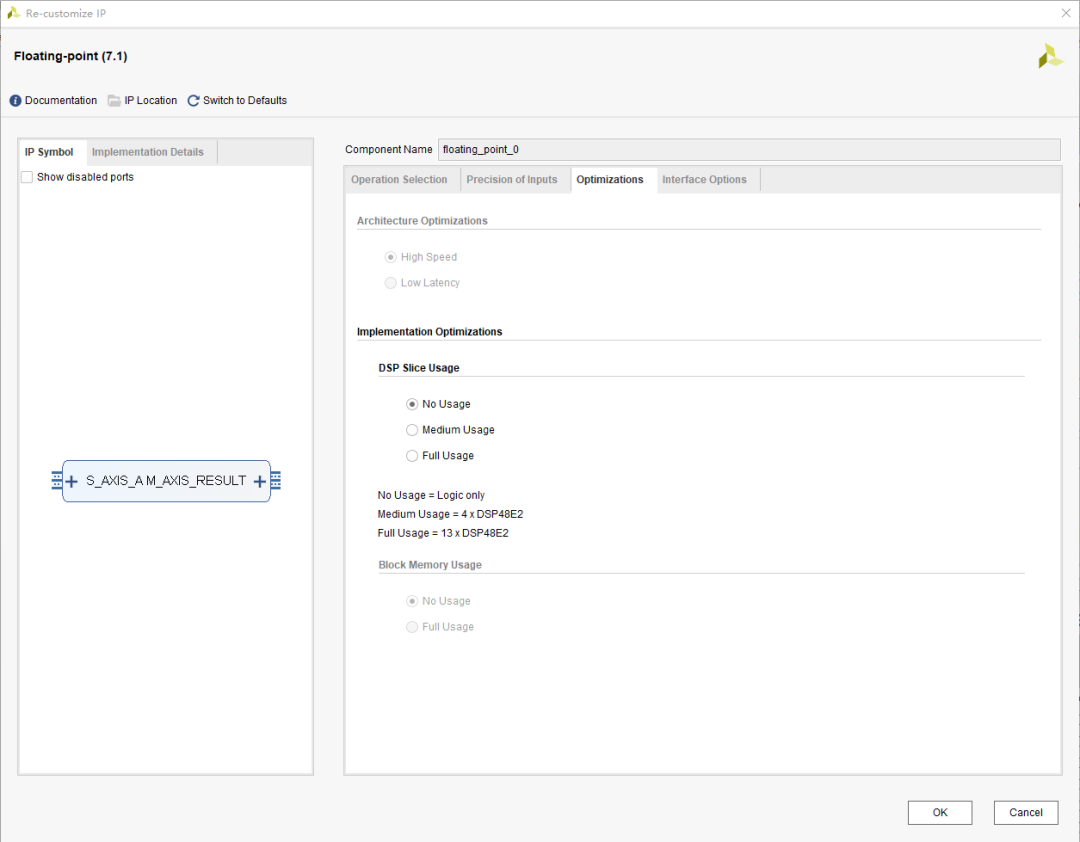

實現對數運算時,可以使用DSP核心,也可以不用,IP配置中提供了三個等級:

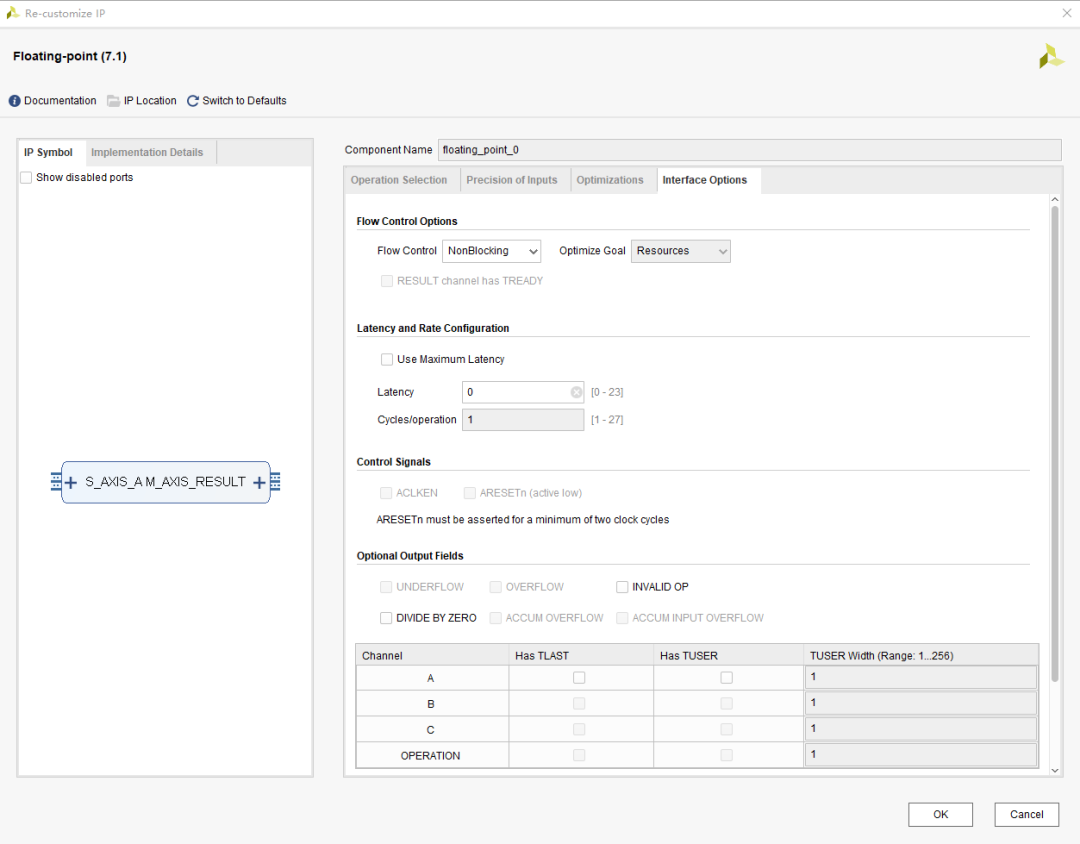

對于Flow Control可以選擇帶緩存的Blocking模式,也可以選擇沒有緩存的NonBlocking模式,延時也可以選擇從0到23:

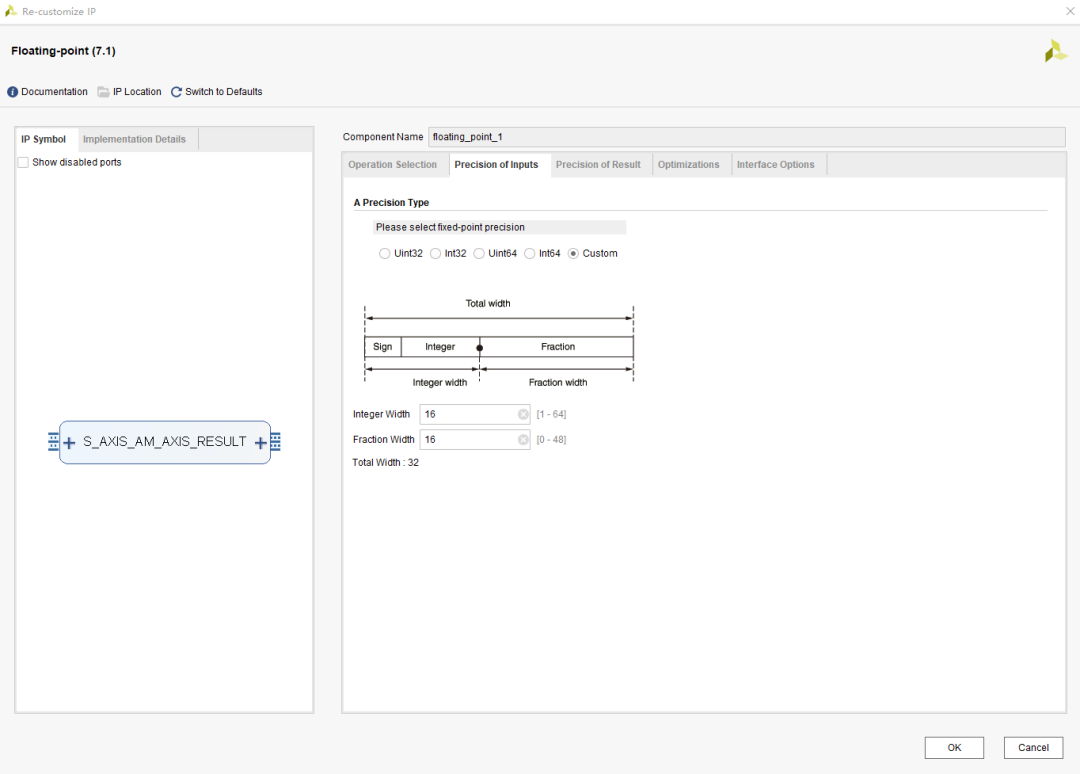

上面也提到,計算LOG的輸入是浮點數,如果需要,可以繼續使用floating-point來實現定點數轉浮點數,對于轉換IP的輸入可以自主設定如下圖所示,這里設為int16+fra16,輸出為單精度浮點數,可以直接給計算LOG的IP核:

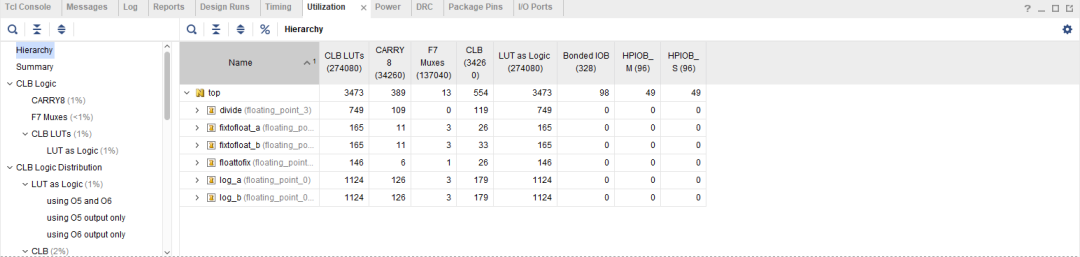

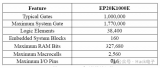

我們要計算以任意數為底的對數時,可以通過來計算,由此完成一次計算,需要兩個定點轉浮點的IP(fixtofloat),兩個LOG的IP(log不使用DSP),以及一個除法IP(divide),最后再將浮點數轉為定點數輸出,綜合實現后的資源占用情況為:

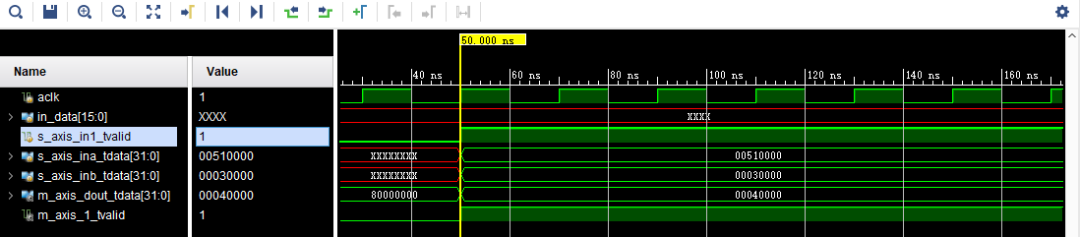

一次簡單的RTL仿真為:

原文標題:FPGA中實現對數運算

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

dsp

+關注

關注

555文章

8142瀏覽量

355318 -

FPGA

+關注

關注

1643文章

21967瀏覽量

614257 -

乘法器

+關注

關注

9文章

211瀏覽量

37822

原文標題:FPGA中實現對數運算

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

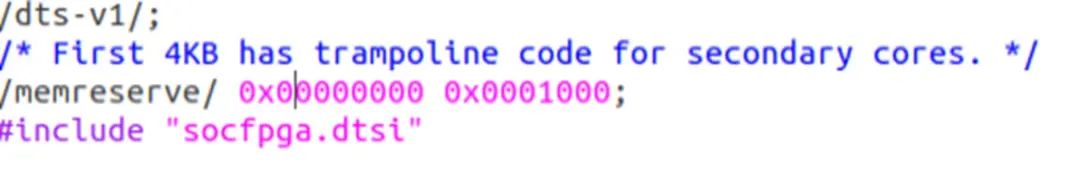

Linux系統中通過預留物理內存實現ARM與FPGA高效通信的方法

進群免費領FPGA學習資料!數字信號處理、傅里葉變換與FPGA開發等

基于FPGA實現圖像直方圖設計

FPGA中實現對數運算的方法

FPGA中實現對數運算的方法

評論